![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](//s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-768x994.png)

Elementy cyfrowe i układy

logiczne

Wykład 4

Legenda

Podział układów logicznych

Układy cyfrowe, układy scalone

Synteza logiczna

Układy TTL, CMOS

2

1

Podział układów

Układy logiczne

sekwencyjne

kombinacyjne

n

.

.

.

Układ

kombinacyjny

.

.

.

m

?

3

Hierarchia projektowa

bloki

Symbol układu

Źródło: Podstawy projektowania układów logicznych i komputerów

4

2

Hierarchia - diagram

bloki elementarne

(ang. primitive blocks)

A to też?

5

Źródło: Podstawy projektowania układów logicznych i komputerów

Projektowanie – metoda

zstępująca (ang. top down)

synteza ręczna

Informacja o ograniczeniach związanych z

kosztami, szybkością pracy, możliwością

ponownego wykorzystania bloków

Podział na bloki

synteza automatyczna

Funkcja układu określona za pomocą

tekstu lub języka opisu sprzętu (HDL)

Projekt logiczny

6

3

Synteza „ręczna”

Kombinacyjny układ logiczny otrzymujemy łącząc bramki

(elementarne układy logiczne). Synteza układu kombinacyjnego może

być podzielona na następujące etapy:

Określenie funkcji logicznej rozpatrywanego problemu

Minimalizacja funkcji logicznej

Sporządzenie schematu układu logicznego realizującego

zminimalizowaną funkcję logiczną

Weryfikacja schematu układu logicznego

7

Projektowanie wspomagane komputerowo

(CAD – computer-aided design)

Narzędzia do graficznego

wprowadzania schematów

(ang. schematic capture)

Biblioteki symboli

graficznych bloków

elementarnych i

Modele umożliwiające

funkcjonalnych

zweryfikowanie działania i

zależności czasowych

poszczególnych bloków

Symulator logiczny

Programy

do

syntezy

logicznej

Optymalizacja

projektów

generowanych

automatycznie na

podstawie

specyfikacji w

HDL

8

4

Synteza logiczna

Opis układu w

języku HDL

Ograniczenia projektowe:

elektronika, szybkość pracy

i powierzchnia układu

Biblioteka

technologii

Translacja

Reprezentacja

pośrednia

Optymalizacja

wstępna

ustalenie wspólnych

fragmentów opisu

logicznego

połączenia bramek

i elementów

bloki logiczne i ich

połączenia

Optymalizacja

właściwa

Wybór technologii

realizacji

Lista połączeń (ang. netlist)

zastępowanie

AND, OR, NOT

bramkami z danej

technologii

9

Źródło: na podstawie „Podstawy projektowania układów logicznych i komputerów”

Układ cyfrowy

Układ cyfrowy – układ skonstruowany

z układów scalonych

10

5

Układ scalony

Układ scalony – (ang. intergrated circuit, chip)

(potocznie: kość, kostka) – kawałek krzemowej płytki

półprzewodnikowej,

zminiaturyzowany

układ

elektroniczny zawierający w swym wnętrzu od kilku

do setek milionów podstawowych elementów

elektronicznych, takich jak tranzystory, diody,

rezystory, kondensatory.

Zwykle zamknięty w hermetycznej obudowie –

szklanej, metalowej, ceramicznej lub wykonanej z

tworzywa sztucznego, a połączenia zewnętrzne są

wyprowadzona poza obudowę.

11

Układ i struktura

Półprzewodnikowy układ scalony – układ

scalony, którego elementy są wykonane w

objętości

i

na

powierzchni

podłoża

krzemowego.

Struktura półprzewodnikowa – tranzystor,

dioda lub półprzewodnikowy układ scalony bez

obudowy.

12

6

Podział układów scalonych

Ze względu na sposób wykonania rozróżnia się układy:

• monolityczne, w których wszystkie elementy wykonane są w

monokrystalicznej strukturze półprzewodnika

• hybrydowe - na płytki wykonane z izolatora nanoszone są

warstwy przewodnika oraz materiału rezystywnego, które

następnie są wytrawiane, tworząc układ połączeń elektrycznych

oraz rezystory. Do tak utworzonych połączeń dołącza się

indywidualne, miniaturowe elementy elektroniczne (w tym

układy monolityczne).

Ze względu na grubość warstw rozróżnia się układy:

• cienkowarstwowe (warstwy ok. 2 mikrometrów)

• grubowarstwowe (warstwy od 5 do 50 mikrometrów)

13

Podział układów scalonych

Większość stosowanych obecnie układów

scalonych jest wykonana w technologii

monolitycznej.

14

7

Podział układów scalonych

• W układach monolitycznych praktycznie wszystkie elementy wykonuje

się jako tranzystory, odpowiednio tylko przyłączając ich końcówki,

dlatego też często mówi się o gęstości upakowania tranzystorów na mm2.

• W dominującej obecnie technologii wytwarzania monolitycznych

układów scalonych (technologia CMOS) często używanym wskaźnikiem

technicznego zawansowania procesu oraz gęstości upakowania

elementów układów scalonych jest minimalna długość bramki

tranzystora wyrażona w mikrometrach lub nanometrach.

• Im mniejsza jest "liczba technologii”, tym upakowanie tranzystorów oraz

ich szybkość działania jest większe.

• W najnowszych technologiach, w których m.in. produkowane są

procesory firm Intel i AMD, minimalna długość bramki wynosi 45nm.

15

Podział ze względu na stopień

scalenia

• małej skali integracji (SSI – small scale of integration)

liczba bramek jest zwykle mniejsza od 10 i ograniczona liczbą dostępnych

zacisków zewnętrznych

• średniej skali integracji (MSI – medium scale of integr.)

około 10-100 bramek w jednej obudowie

• dużej skali integracji (LSI – large scale of integration)

od 100 do kilku tysięcy bramek; małe procesory, małe pamięci, moduły

programowalne

• wielkiej skali integracji (VLSI – very large scale of int.)

od kilku tysięcy do dziesiątek milionów bramek; mikroprocesory, cyfrowe

procesory sygnałowe

• ultrawielkiej skali integracji (ULSI – ultra large scale of

integration)

16

8

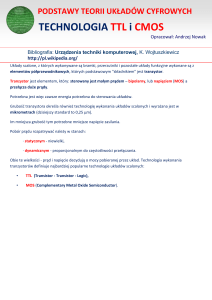

Technologie wytwarzania

• TTL (Transistor-Transistor Logic) – oznacza

technologię, w której do budowy pojedynczego

obwodu logicznego stosuje się wiele tranzystorów

scalonych w jeden układ. Większość układów

TTL ma czternasto- lub szesnastonóżkową

obudowę typu DIL.

• CMOS

(Complementary

Metal

Oxide

Semiconductor) –stosuje się dwa komplementarne

tranzystory polowe MOS; tylko jeden z nich może

być w stanie przewodzenia.

17

Klasy układów cyfrowych

• TTL (Transistor – Transistor - Logic) – układy TTL,

• ECL (Emiter – Coupled Logic) – układy o sprzężeniu

emiterowym,

• MOS (Metal – Oxide - Semiconductor) – układy MOS,

• CMOS

(Complementary

MOS)

–

układy

komplementarne MOS,

• BiCMOS (Bipolar CMOS) – układy ,,mieszane”,

bipolarne CMOS,

• I2L (Integrated Injection Logic) – układy iniekcyjne,

• CTD (Charge Transfer Device) – układy o sprzężeniu

ładunkowym,

18

• GaAs MESFET – układy GaAs.

9

Czas życia różnych technologii

• Układy TTL ustępują miejsca nowszym technologiom

CMOS i BiCMOS, zwłaszcza niskonapięciowym (LV –

19

Low Voltage)

Parametry

• Obciążalność wejściowa bramki

określa liczbę dostępnych wejść bramki, często ograniczona do nie

więcej niż 4 lub 5

• Obciążalność wyjściowa bramki

określa liczbę wejść bramki, które można dołączyć do wyjścia

danej bramki

• Margines zakłóceń

Maksymalne zewnętrzne napięcie, które

niepożądanych zmian na wyjściu układu

nie

spowoduje

• Opóźnienie propagacji

czas przeniesienia sygnału wejściowego na wyjście układu

• Moc rozpraszania

określana przez moc pobieraną ze źródła i traconą przez bramkę

20

10

Obciążalność wejściowa

21

Obciążalność wyjściowa

Każde wejście bramki sterowanej stanowi obciążenie

wyjścia bramki sterującej, mierzone w standardowych

jednostkach

Przykład: Obliczyć obciążenie 4-wejściowej bramki NAND jeżeli

jej wyjście jest połączone z następującymi wejściami bramek:

4-wejściowy NOR – 0,8 standardowego obciążenia

3-wejściowy NAND – 1,0 standardowego obciążenia

inwerter – 1,0 standardowego obciążenia

Suma standardowych

obciążeń sterowanych przez

bramkę

tpd = 0,07 + 0,021 * SL [ns]

tpd = 0,07 + 0,021 * (0,80+1,00+1,00) = 129 ns

22

11

Opóźnienie propagacji

czas propagacji

sygnału do stanu

niskiego na wyjściu

czas propagacji

sygnału

(opóźnienie)

czas propagacji

sygnału do stanu

wysokiego na wyjściu

23

Źródło: na podstawie „Podstawy projektowania układów logicznych i komputerów”

Modele opóźnień

• Opóźnienie transportowe (ang. transport delay – TD)

zmiana sygnału wyjściowego stanowiąca odpowiedź na

zmianę sygnału wejściowego pojawia się po

określonym opóźnieniu propagacji.

• Opóźnienie inercyjne (ang. inertial delay – ID)

podobne do TD, z wyjątkiem sytuacji, gdy zmiana

wejścia powodowałaby konieczność zmiany stanu na

wyjściu dwukrotnie w przedziale czasu mniejszym niż

tzw. czas pochłaniania (ang. rejection time), wówczas

pierwsza z tych zmian nigdy nie wystąpi na wyjściu.

24

12

Modele opóźnień

Opóźnienie

propagacji

Czas

pochłaniania

25

Źródło: „Podstawy projektowania układów logicznych i komputerów”

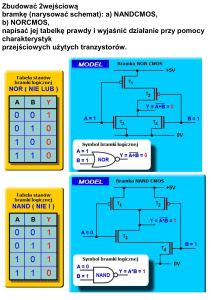

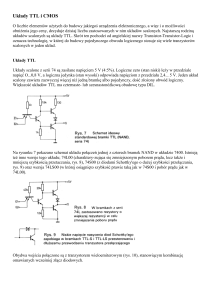

Układy TTL

• Układy TTL (Transistor-Transistor Logic) zbudowane

z bipolarnych tranzystorów, są zasilane napięciem

stałym 5 V.

• Sygnał TTL jest niski (logiczne "0"), gdy potencjał ma

wartość od 0 V do 0,8 V w odniesieniu do masy,

wysoki (logiczna "1") przy wartości potencjału między

2 a 5 V.

• Większość współcześnie produkowanych układów TTL

jest oparta na diodach Schottky'ego, a nie na

tranzystorach i powinna być raczej zaliczana do DTL

(Diode-Transistor Logic).

26

13

Odmiany układów TTL

• L (Low power) – wersja o małym poborze mocy, ale wolniejsza

od standardowej; nigdy nie zyskała popularności, gdyż została

niemal natychmiast zastąpiona układami CMOS serii 4000.

• H (High speed) – wersja szybsza od standardowej, ale o

większym poborze mocy niż standardowa. Większą szybkość

uzyskano przez zastosowanie 2x mniejszych rezystorów, co

spowodowało szybsze przełączanie tranzystorów.

• S (Schottky) – odmiana szybka, której tranzystory zawierają

dodatkową diodę Schottky’ego włączoną równolegle do złącza

kolektor-baza i zabezpieczającą tranzystor przed nasyceniem, co

powoduje dużo szybsze przechodzenie tranzystora ze stanu

przewodzenia do zatkania.

27

Odmiany układów TTL

• AS (Advanced Schottky) – ulepszona seria S,

charakteryzuje się jeszcze większą szybkością

działania.

• LS (Low power Schottky) – wersja S o znacznie

niższym poborze prądu, zbliżonym do standardowej

bramki; główna seria układów TTL, stosowana w

większości zastosowań.

• ALS (Advanced Low power Schottky) –

unowocześniona seria LS, z mniejszym poborem mocy.

• F (Fast) – nowoczesna, najszybsza seria TTL.

28

14

Częstotliwości graniczne układów

cyfrowych

S– bardzo szybka (Schottky)

LS- małej mocy, bardzo szybka

(Low power Schottky)

F– bardzo bardzo szybka (Fast)

AS– ulepszona, bardzo szybka

(Advanced Schottky)

ALS- ulepszona małej mocy,

bardzo szybka

(Advanced Low power Schottky)

29

Odmiany układów

• Układy w technologii CMOS produkowane są zgodnie

końcówkowo z TTL, o takich samych oznaczeniach,

wyróżniane literami C, AC, HCT, HC itp., np.:

74HC00.

• Dodatkowo układy CMOS HCT mają takie same

poziomy stanów logicznych jak TTL, przez co można

je łączyć ze sobą.

Układy TTL mają większy pobór prądu niż układy

wykonane w technologii CMOS

Układy TTL są szybsze od układów CMOS

30

15

Oznaczenia układów CMOS

Przykład: HCA712S34

Pierwsza litera oznaczenia określa sposób wykonania

według następujących reguł:

U - układ półprzewodnikowy, monolityczny, bipolarny,

H - układ hybrydowy,

M - układ półprzewodnikowy, monolityczny, unipolarny.

Druga litera oznaczenia określa rodzaj ogólnej funkcji

układu scalonego:

C - układy cyfrowe,

L - układy analogowe,

R - inne układy scalone.

31

Oznaczenia układów scalonych

Trzecia litera określa przeznaczenie układu scalonego:

A - do zastosowań specjalnych,

Y - do zastosowań profesjonalnych,

T - do zastosowań profesjonalnych o podwyższonej

niezawodności,

Q - do zastosowań specjalnych o podwyższonej

niezawodności,

X - prototypowe, doświadczalne lub na zamówienia.

brak litery do zastosowań w sprzęcie powszechnego

użytku.

32

16

Oznaczenia układów scalonych

Pierwsza cyfra określa zakres dopuszczalnej temperatury

otoczenia podczas pracy w °C:

4 - od -55 do +85

5 - od -35 do +125

6 - od -40 do +85

7 - od 0 do +70

8 - od -25 do +85

33

Oznaczenia układów scalonych

Druga, trzecia, czwarta lub piąta cyfra stanowią liczbę

porządkową określającą dany typ układu.

Po drugiej cyfrze w oznaczeniach monolitycznych

cyfrowych układów scalonych mogą być wprowadzone

litery określające serię układu:

H - seria szybka,

S - seria bardzo szybka,

brak litery - seria standardowa

34

17

Zakłócenia w systemie cyfrowym

• Zakłóceniami nazywamy niepożądane sygnały elektryczne

występujące na połączeniach w systemie.

• Powstają na wskutek przełączania bramek, a przenoszone są

poprzez promieniowanie elektromagnetyczne albo przez związane

z przełączaniem fluktuacje napięcia zasilającego.

• Źródło zakłóceń może być poza systemem.

• Układy cyfrowe muszą być niewrażliwe na zakłócenia o pewnym

poziomie i powinny pracować poprawnie przy ich występowaniu.

• Margines zakłóceń jest wartością zakłóceń, które nie powodują

błędnej pracy elementów systemu. Jest to dopuszczalna wartość

napięcia zakłóceń, wyznaczona z różnicy odpowiednich

gwarantowanych wartości napięć wyjściowych bramki i

akceptowanych dla danych stanów logicznych wartości stanów

35

wejściowych.

Źródła zakłóceń

•

•

•

•

•

napięcia zasilającego,

uziemieniowe,

przesłuchowe w liniach transmisyjnych,

odbiciowe w liniach transmisyjnych,

zewnętrzne.

36

18

Marginesy zakłóceń

Marginesy zakłóceń wskazują, jaki poziom zakłóceń nie spowoduje

błędnego odczytu sygnału wejściowego w najgorszym przypadku.

ULI max -ULO max

UHO min -UHI min

CMOS

UDD = + 5 V

- margines zakłóceń stanu niskiego

- margines zakłóceń stanu wysokiego

ULO

ULI

UHO

UHI

0

1

2

3

4

stany wyjściowe

stany wejściowe

5

37

Napięcia progowe i odporność na

zakłócenia

38

19

Poziomy napięć układów TTL

• Wartości gwarantowane poziomów napięć logicznych na wejściu i

wyjściu układów TTL, UT – próg przełączania bramki

39

Charakterystyki przejściowe

bramek TTL

40

20

Parametry układów CMOS i TTL

41

Zakresy typowych napięć rodziny

CMOS

42

21

Podstawowe układy TTL

43

7400: 4x 2-wejściowe bramki NAND

44

22

7402: 4x 2-wejściowe bramki NOR

45

7404: 6 x inwerter

46

23

7408: 4x 2-wejściowe bramki AND

47

7410: 3x 3-wejściowe bramki NAND

48

24

7411: 3x 3-wejściowe bramki AND

49

7430: 1x 8-wejściowa bramka NAND

50

25

Koniec

Dziękuję za uwagę

51

26

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-768x994.png)