1

Dr Galina Cariowa

Legenda

Podział układów logicznych

Narzędzia projektowania układów cyfrowych:

a) hierarchia projektowa;

b) projektowanie metodą zstępującą;

c) narzędzia komputerowego wspomagania

projektowania;

d) języki opisu sprzętu;

e) synteza logiczna.

Układy cyfrowe, układy scalone

Parametry technologiczne realizacji układu

Układy TTL, CMOS

2

Podział układów

3

Układ kombinacyjny

Układem kombinacyjnym nazywamy taki układ

cyfrowy, w którym stan wejść jednoznacznie

określa stan wyjść układu.

Skład układu kombinacyjnego:

zmienne wejściowe,

zmienne wyjściowe,

bramki logiczne,

połączenia między tymi elementami.

Układ kombinacyjny może być określony za pomocą:

1) tablicy prawdy;

2) m funkcji boolowskich- po jednej dla każdej zmiennej

wyjściowej.

4

Przykłady układów kombinacyjnych

1. Najprostszym przykładem układu

kombinacyjnego są bramki logiczne.

2. Bloki kombinacyjne:

sumatory,

komparatory,

dekodery,

kodery,

multipleksery,

demultipleksery.

5

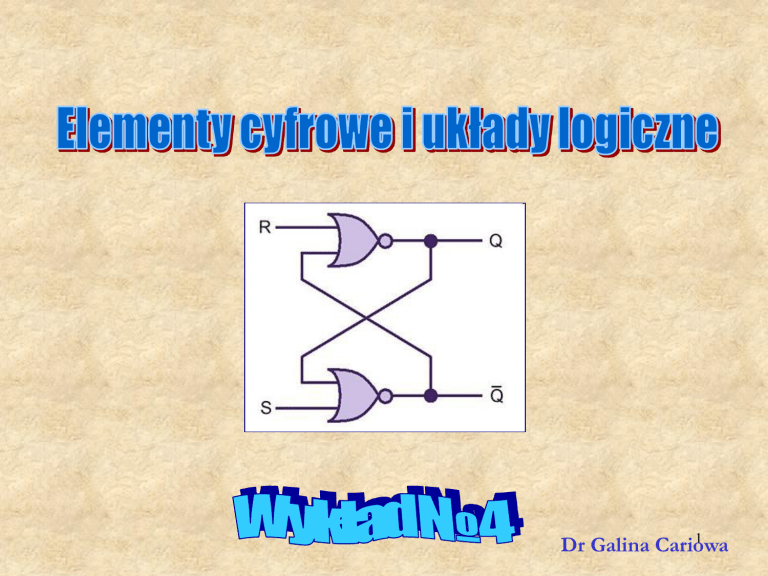

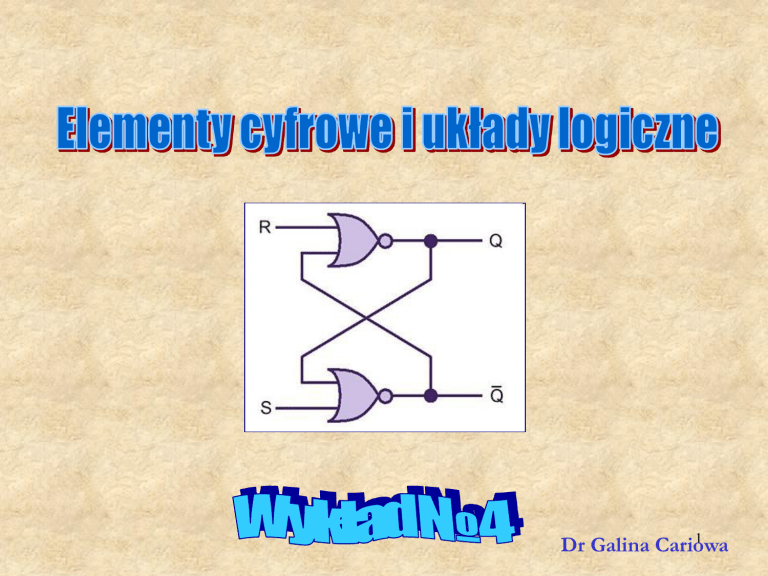

Układ sekwencyjny

Układem sekwencyjnym nazywamy taki układ

cyfrowy, w którym stan wyjść zależy od stanu

wejść oraz od poprzednich stanów układu.

Układy sekwencyjne zawierają elementy,

które zapamiętują wartości bitowe

(zatrzaski, przerzutniki).

6

Metody projektowania

układów logicznych:

Projektowanie hierarchiczne

Zstępująca metoda projektowania

7

Projektowanie hierarchiczne

Złożony system cyfrowy może zawierać

miliony połączonych bramek.

Złożony system nie może być

projektowany przez łączenie

pojedynczych bramek.

Projektowanie układów kombinacyjnych

jest oparte na zasadzie „dziel i rządź”.

8

Hierarchia projektowa

Układ jest dzielony na kawałki (bloki).

Bloki są łączone w taki sposób, że tworzą układ.

Funkcje tych bloków oraz ich interfejsy

są dokładnie zdefiniowane.

Układ utworzony z połączonych ze sobą

bloków jest zgodny ze specyfikacją układu.

Ten proces może być powtórzony

w razie potrzeby.

9

Hierarchia projektowa

Blok EXOR

Blok 3-wejściowej

funkcji kontroli

nieparzystości

Przy przemieszczaniu w dół z wyższego poziomu symbole są

zastępowane schematami, które reprezentują implementację

10

danego symbolu.

Hierarchia projektowa

(drzewiasta)

Strukturę hierarchii można przedstawić

zaznaczania wzajemnych połączeń.

bez

Rozpoczynając od bloku najwyższego poziomu

łączymy z nim każdy z bloków niższego

poziomu, z których jest zbudowany.

11

Hierarchia - diagram

tylko jedna kopia

każdego układu

„Liście” tego drzewa stanowią bramki NAND

(bramki podstawowe).

12

Zalety stosowania hierarchii

1. Uzyskujemy uproszczoną reprezentację

złożonego układu

(zamiast 32 bloków NAND w schemacie

układu tylko 10 symboli użytych w hierarchii).

2. Hierarchia mogłaby kończyć się na blokach

EXOR, które mogą być uważane za bloki

predefiniowane (oznaczone symbolami, lecz

nie schematami logicznymi, ich funkcje można

zdefiniować przy użyciu programu lub

opisu, który służy jako model).

3. Możliwość wielokrotnego wykorzystania bloków.

13

Projektowanie-metoda zstępująca

(ang. top down) „z góry na dół”

14

Synteza ręczna

Synteza układu kombinacyjnego może być

podzielona na następujące etapy:

Określenie funkcji logicznej rozpatrywanego problemu.

Minimalizacja funkcji logicznej.

Sporządzenie schematu układu logicznego

realizującego zminimalizowaną funkcję logiczną.

Weryfikacja schematu układu logicznego.

15

Projektowanie wspomagane

komputerowo

(CAD – computer - aided design)

16

Struktura procesu projektowania na

wysokim poziomie, zawierająca etapy

syntezy logicznej.

17

Układ cyfrowy

Układ cyfrowy- układ skonstruowany z

układów scalonych.

Pierwszy układ

scalony

zbudował Jack

Kilby z Texas

w roku 1958, za

co otrzymał

nagrodę Nobla

z fizyki w 2000.

18

Układ cyfrowy

19

Układy scalony

Układ scalony – (ang.

intergrated circuit, chip) –

kawałek krzemowej płytki

półprzewodnikowej,

zawierający w swym wnętrzu

od kilku do setek milionów

podstawowych elementów

elektronicznych, takich jak

tranzystory, diody, rezystory,

kondensatory.

Zwykle zamknięty w

hermetycznej obudowie –

szklanej, metalowej,

ceramicznej lub wykonanej z

20

tworzywa sztucznego.

Układy scalony

Z zewnątrz układ scalony

przypomina małą kostkę z

wyprowadzonymi metalowymi

końcówkami, do których

doprowadzamy lub z których

pobieramy sygnały

elektryczne.

Wewnątrz układu scalonego

wyprowadzenia są połączone

z małą płytką silikonową, na

której utworzono strukturę

elektroniczną złożoną z setek

lub tysięcy tranzystorów.

21

Układy scalony

Zaciski (nóżki) każdego

układu scalonego są

odpowiednio numerowane.

Na obudowie znajduje się małe

wycięcie lub mała dziurka.

Układ ustawiamy nóżkami w dół

tak, aby wcięcie na obudowie

znalazło się po stronie lewej.

Wtedy numeracja nóżek

rozpoczyna się od lewego

dolnego rogu i biegnie wokół

układu scalonego.

22

Podział układów scalonych

Ze względu na sposób wykonania rozróżnia się układy:

• monolityczne, w których wszystkie elementy wykonane są w

monokrystalicznej strukturze półprzewodnika;

• hybrydowe, w których na płytki wykonane z izolatora

nanoszone są warstwy przewodnika oraz materiału

rezystywnego, które następnie są wytrawiane.

Ze względu na grubość warstw rozróżnia się układy:

• cienkowarstwowe (warstwy ok. 2 mikrometrów);

• grubowarstwowe (warstwy od 5 do 50 mikrometrów).

1m 1mikrometr 106 m

23

Układy scalone

Większość stosowanych obecnie

układów scalonych jest wykonana w

technologii monolitycznej.

W układach monolitycznych wszystkie

elementy wykonuje się jako tranzystory.

gęstość upakowania tranzystorów na mm. kw.

24

Układy monolityczne

W dominującej obecnie technologii wytwarzania

monolitycznych układów scalonych CMOS

wskaźnikiem gęstości upakowania jest minimalna

długość bramki tranzystora wyrażona w

mikrometrach lub nanometrach.

W najnowszych technologiach minimalna

długość bramki wynosi 45nm.

9

1nm 1nanometr 10 m

Im mniejsza jest "liczba technologii”,

tym upakowanie tranzystorów oraz

ich szybkość działania jest większe.

25

Podział układów ze względu

na stopień scalenia

Malej skali integracji (SSI – small scale of integration)

liczba bramek <10 i ograniczona liczbą dostępnych zacisków wewnętrznych

Średniej skali integracji (MSI – medium scale of integr.)

około 10 – 100 bramek w jednej obudowie

Dużej skali integracji (LSI – large scale of integr.)

od 100 do kilku tysięcy bramek:

małe procesory, małe pamięci, moduły programowalne.

Wielkiej skali integracji (VLSI – very large scale of int.)

od kilku tysięcy do dziesiątek milionów bramek:

mikroprocesory, cyfrowe procesory analogowe.

Ultrawielkiej skali integracji (ULSI – ultra large

scale of integration )

26

Układy scalone

Cyfrowe układy scalone są wytwarzane w dwu

zasadniczych odmianach aplikacyjnych –

układy uniwersalne i układy specjalizowane

(ASIC – Application Specific Integrated Circts).

Pierwsze z nich są produkowane we wszystkich

stopniach scalenia do uniwersalnych zastosowań.

Układy grupy ASIC są natomiast wyłącznie układami

LSI i VLSI.

Umożliwiają one zmniejszenie rozmiarów, mocy strat i

27

kosztu projektowanych urządzeń.

Parametry technologiczne

realizacji układu:

28

Parametry technologiczne

realizacji układu:

Wyjścia bramek można łączyć z wejściami innych

` bramek logicznych.

W ten sposób powstaje sieć logiczna realizująca

złożoną funkcję logiczną.

Samych wyjść nie wolno ze sobą łączyć, ponieważ

prowadzi to do zwarcia i w konsekwencji do

uszkodzenia bramki.

29

Obciążalność wejściowa

30

Obciążalność wyjściowa

Każde wejście bramki dołączone do wyjścia innej bramki

pobiera z niej pewien prąd elektryczny.

Wyjścia bramek mogą dostarczyć tylko określoną ilość

prądu. Wynika z tego, iż do typowego wyjścia można

podłączyć ograniczoną ilość wejść innych bramek.

Parametr ten nosi nazwę obciążalności wyjścia bramki.

Zwykle przyjmuje się go na poziomie 10 dla zwykłych

bramek TTL oraz 30 dla bramek o zwiększonej mocy

wyjściowej.

31

Obciążalność wyjściowa

Obciążalności wyjściowej bramki nie należy

przekraczać, gdyż może to spowodować niestabilność

sieci logicznej, a nawet spalenie niektórych jej

elementów.

Do bramek CMOS reguła ta się nie odnosi, ponieważ

pobierają one bardzo mały prąd wejściowy - mówimy, iż

posiadają dużą oporność wejściową.

32

Obciążalność wyjściowa.

Pomiar obciążalności wyjściowej.

Jeden ze sposobów pomiaru polega na

zastosowaniu obciążenia standardowego.

Każde wejście bramki sterowanej stanowi

obciążenie wyjścia bramki sterującej, mierzone

w standardowych jednostkach.

33

Obciążalność wyjściowa

Rzeczywista obciążalność wyjściowa bramki,

określona za pomocą obciążeń standardowych, ma

wpływ na czas propagacji bramki.

Przykład: Obliczyć opóźnienie 4-wejściowej bramki NAND

jeżeli jej wyjście jest połączone z następującymi wejściami

bramek:

4-wejsciowy NOR – 0,8 standardowego obciążenia

3-wejsciowy NAND – 1,0 standardowego obciążenia

inwerter – 1,0 standardowego obciążenia

opóźnienie standardowego

stałe opóżnienie obciążenia

t pd 0,07 0,021 SLns

liczba obciążeń

standardowych na wyjściu

t pd 0,07 0,021 (0,80 1,00 1,00) 0,129ns

(SL - suma standardowych obciążeń sterowanych przez bramkę)

34

Obciążalność wyjściowa

W trakcie etapu procesu projektowego

związanego z wyborem technologii realizacji

zarówno obciążalność wejściowa jak i wyjściowa

muszą być określane..

Bramki o obciążalności wejściowej (wyjściowej)

większej od dopuszczalnej w danej technologii

mogą być zaimplementowane za pomocą większej

liczby bramek.

35

Opóźnienie propagacji

Napięcie na wyjściu nie zmienia się

natychmiast po zmianie poziomu napięć

wejściowych, lecz po pewnym czasie typowo po 10 ns.

Jest to spowodowane tym, iż tranzystory

wewnątrz bramki muszą się odpowiednio

po przełączać, a to wymaga czasu.

36

Opóźnienie propagacji

Czas propagacji bramki logicznej określa po

jakim czasie od zmiany napięć wejściowych

ustali się napięcie na wyjściu.

Im mniejszy czas propagacji, tym szybciej może

pracować bramka.

Czas propagacji dla sieci logicznej jest sumą

czasów propagacji bramek, poprzez które

przechodzi kolejno sygnał logiczny.

37

Opóźnienie propagacji ( dla inwertera)

Sposób określenia czasu opóźnienia propagacji:

38

Modele opóźnień

Czas pochłaniania ma ściśle określoną wartość, nie

mniejszą niż czas propagacji i często mu równą.

39

Modele opóźnień

A

B

A B:

Bez opóźnienia

(ND)

Z opóźnieniem

transportowym(TD)

a b

c d e

Z opóźnieniem

inercyjnym (ID)

0

2

4

6

8

10

12

14

16 Time (ns)

Propagation Delay = 2.0 ns Rejection Time = 1 .0 ns

40

Klasy układów cyfrowych

I

41

Technologie

wytwarzania TTL

Najstarszą rodziną układów scalonych są układy TTL.

Skrót ten pochodzi od angielskiej nazwy

Transistor-Transistor-Logic

i oznacza technologię, w której do budowy

pojedynczego obwodu logicznego stosuje się wiele

tranzystorów bipolarnych w jeden układ.

Układy TTL są zasilane napięciem stałym 5v.

42

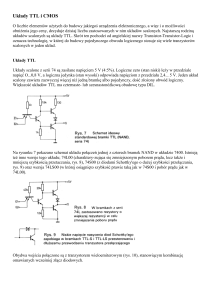

Układy TTL

Poziomy napięć i prądów wejścia i wyjścia

zdefiniowane przez standard.

Charakterystyczne parametry dla tej technologii:

duży pobór prądu (około 10 mW na bramkę);

mała prędkość (10 ns na bramkę);

duża obciążalność wyjścia (możliwość

sterowania 10 bramek TTL).

43

Odmiany układów TTL

Technologia Pobór prądu Prędkość

TTL-L

mały

mała

TTL-S

bardzo duży

duża

TTL-H

duży

bardzo duża

TTL-LS

mały

duża

TTL-F

duży

ekstra duża

44

Odmiany układów TTL

L (Low power) – wersja o małym poborze

mocy, ale wolniejsza od standardowej.

Nie zyskała popularności, natychmiast

zastąpiona układami CMOS serii 4000.

S (Schottky) – odmiana szybka, której

tranzystory zawierają dodatkową diodę

Schottky’ego.

H (High speed) - wersja szybsza od

standardowej, ale o większym poborze mocy

niż standardowa.

45

Odmiany układów TTL

LS (Low power Schottky) – wersja S o znacznie

niższym poborze prądu, zbliżonym do

standardowej bramki. Główna seria układów

TTL, stosowana w większości zastosowań.

F (Fast) – nowoczesna, najszybsza seria TTL.

46

Układy TTL

W praktyce inżynierskiej układy TTL są traktowane

jako układy uniwersalne.

Dzięki dużemu asortymentowi typów i wielu odmian

serii układy TTL dominują w zastosowaniach

sprzętowych, wykorzystujących układy SSI i MSI.

Konkurencyjne do nich są układy CMOS, a zwłaszcza

ich odmiany szybkie (HCMOS i ACL).

47

Technologie CMOS

(ang.

Complementar

Metal

Oxid- Silicium)

Symbol

C oznacza,

że bramki

wykonane

są

techniką komplementarną,

tzn. podstawowym elementem jest komplementarna

para tranzystorów unipolarnych MOS, których

podstawową cechą jest bardzo duża rezystancja

wejściowa.

Oznacza to, że jeden typ tranzystora przełączany jest

napięciem odpowiadającym 0 logicznemu na bramce,

drugi - przy napięciu odpowiadającym 1 logicznej.

Napięcie zasilania układów typu CMOS mieści się w

przedziale 5 ÷ 15 V.

48

Technologie CMOS

Poziomy napięć i prądów wejścia i wyjścia

zdefiniowane przez standard.

Charakterystyczne parametry dla tej technologii:

Ultra mały pobór prądu;

Stosunkowo duża prędkość;

Stosunkowo duża obciążalność wyjścia dla

bramek CMOS (możliwość sterowania 1

bramki TTL - LS).

49

Odmiany układów CMOS

50

Oznaczenia układów CMOS

51

Oznaczenia układów CMOS

Przykład:

HCA712S34

Trzecia litera określa przeznaczenie układu

scalonego:

A - do zastosowań specjalnych,

Y - do zastosowań profesjonalnych,

T - do zastosowań profesjonalnych o podwyższonej

niezawodności,

Q - do zastosowań specjalnych o podwyższonej

niezawodności,

X - prototypowe, doświadczalne lub na zamówienia.

brak litery- do zastosowań w sprzęcie powszechnego użytku.

52

Oznaczenia układów CMOS

Przykład:

HCA712S34

Pierwsza cyfra określa zakres

dopuszczalnej temperatury

otoczenia podczas pracy w °C:

4 - od -55 do +85

5 - od -35 do +125

6 - od -40 do +85

7 - od 0 do +70

8 - od -25 do +85

53

Oznaczenia układów CMOS

Przykład:

HCA712S34

54

Zakłócenia w systemie cyfrowym

Zakłóceniami nazywamy niepożądane sygnały elektryczne

występujące na połączeniach w systemie.

Powstają na wskutek przełączania bramek, a przenoszone

są poprzez promieniowanie elektromagnetyczne.

Źródło zakłóceń może być poza systemem.

Układy cyfrowe muszą być niewrażliwe na zakłócenia o

pewnym poziomie i powinny pracować poprawnie przy ich

występowaniu.

Margines zakłóceń jest wartością zakłóceń, które nie

powodują błędnej pracy elementów systemu. Jest to

dopuszczalna wartość napięcia zakłóceń, wyznaczona z

różnicy odpowiednich gwarantowanych wartości napięć

wyjściowych bramki i akceptowanych dla danych stanów

55

logicznych wartości stanów wejściowych.

Parametry układów CMOS i TTL

56

Podstawowe układy TTL. Seria 74xx.

Seria 74xx była jedną z najważniejszych

historycznie serii monolitycznych

układów scalonych.

Oryginalną serię 74xx stanowiły układy

typu Transistor - Transistor Logic (TTL)

o napięciu zasilania 5V.

Jako pierwsza do masowej produkcji

wprowadziła te układy firma Texas

Instruments w roku 1961.

57

7400: 4x 2-wejściowe bramki NAND

SN 7400 – jeden z pierwszych cyfrowych układów scalonych,

pierwotnie produkowany przez firmę Texas Instruments, wykonany

w technologii TTL. Zawiera cztery dwuwejściowe bramki

58

logiczne NAND. Jest to układ 14-nóżkowy.

7402: 4x2-wejściwe bramki NOR

SN 7402 – jeden z pierwszych cyfrowych układów scalonych zawierający

w swym wnętrzu cztery dwuwejściowe bramki NOR. Układ umieszczany

jest w obudowie o 14 wyprowadzeniach. W czasach dominacji technologii

TTL był to jeden z podstawowych elementów tworzących cyfrowe 59

układy elektroniczne.

7406: 6 x inwerter

7406 − 6−krotny inwerter z wysokonapięciowym

wyjściem (do +30V) typu otwarty kolektor. Obciążalność

każdej bramki wynosi dodatkowo 10 wejść TTL.

60

7408 : 4 x 2-wejściowe bramki AND

61

7410 : 3 x 3-wejściowe bramki NAND

62

7411 : 3 x 3-wejściowe bramki AND

63

7430 : 1 x 8-wejściowa bramka NAND

64

Seria 74XX

W okresie największej popularności układów

TTL, (lata 70. i 80.), seria ta obejmowała

ponad 300 pozycji katalogowych.

W późniejszych czasach część układów serii

74xx pojawiła się w seriach, wykonywanych w

technologiach TTL- LS (o obniżonym poborze

mocy) oraz TTL- S (o podwyższonej szybkości),

opartych o tranzystory Schottky’ego.

W latach 90. układy bipolarne TTL zaczęły

ustępować miejsca układom CMOS.

65

Seria 74XX

W obrębie danej serii, poszczególne układy scalone

mogły być łatwo łączone ze sobą bez dodatkowych

układów dopasowujących.

Było to dużym ułatwieniem dla projektantów, którzy

mogli skoncentrować się na logicznych aspektach

tworzonego układu.

Podczas łączenia układów z różnych serii, należy

dodatkowo rozważyć dopasowanie poziomów

napięć, szybkości pracy, oraz obciążalności wyjść.

66

Układy TTL.

Znane producenty układów z serii TTL :

PHilips

STMicroelectronocs

Fairchild

Texas Instruments

67

Układy TTL

W miarę upływu czasu pewne technologie stają się

przestarzałe i dlatego starzeją się technologicznie

również układy scalone.

Najświeższe serie TTL to: serie ALS, F i AS,

natomiast serie LS, S i w szczególności

standardowa (TTL) stają się już przestarzałe.

Układy TTL generalnie ustępują miejsca nowszym

technologiom CMOS i BiCMOS, zwłaszcza

niskonapięciowym (LV – Low Voltage).

68

Dziękuję

za uwagę

69

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-300x300.png)