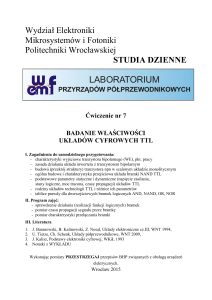

Układy TTL i CMOS

O liczbie elementów użytych do budowy jakiegoś urządzenia elektronicznego, a więc i o możliwości

obniżenia jego ceny, decyduje dzisiaj liczba zastosowanych w nim układów scalonych. Najstarszą rodziną

układów scalonych są układy TTL. Skrót ten pochodzi od angielskiej nazwy Transistor-Transistor-Logic i

oznacza technologię, w której do budowy pojedynczego obwodu logicznego stosuje się wiele tranzystorów

scalonych w jeden układ.

Układy TTL

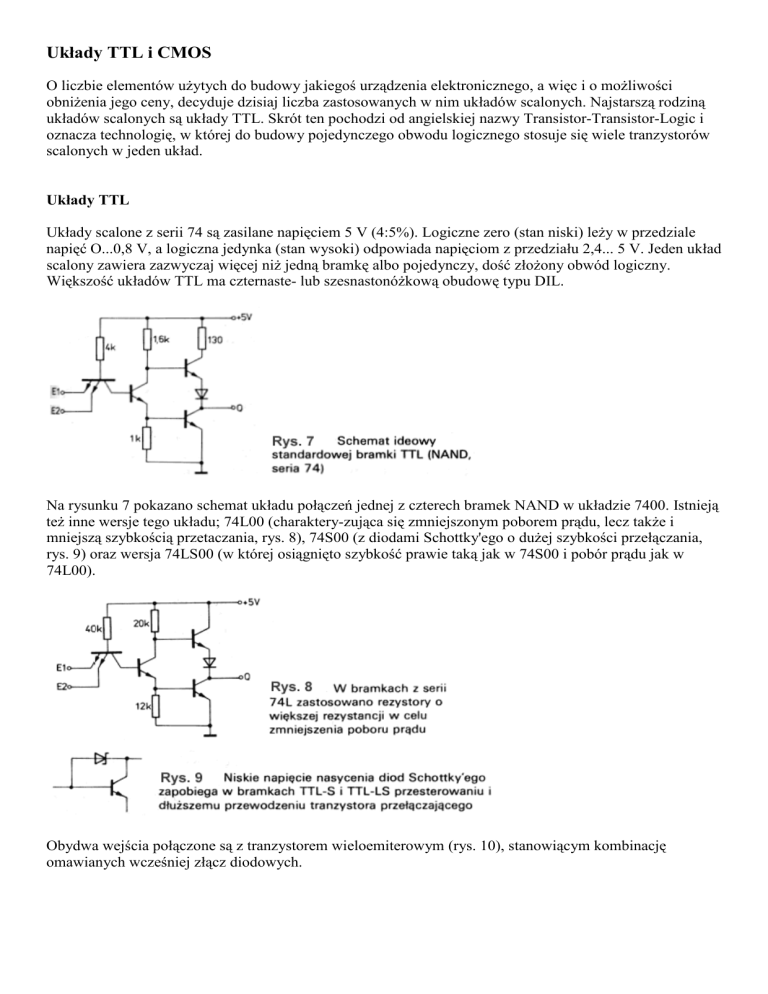

Układy scalone z serii 74 są zasilane napięciem 5 V (4:5%). Logiczne zero (stan niski) leży w przedziale

napięć O...0,8 V, a logiczna jedynka (stan wysoki) odpowiada napięciom z przedziału 2,4... 5 V. Jeden układ

scalony zawiera zazwyczaj więcej niż jedną bramkę albo pojedynczy, dość złożony obwód logiczny.

Większość układów TTL ma czternaste- lub szesnastonóżkową obudowę typu DIL.

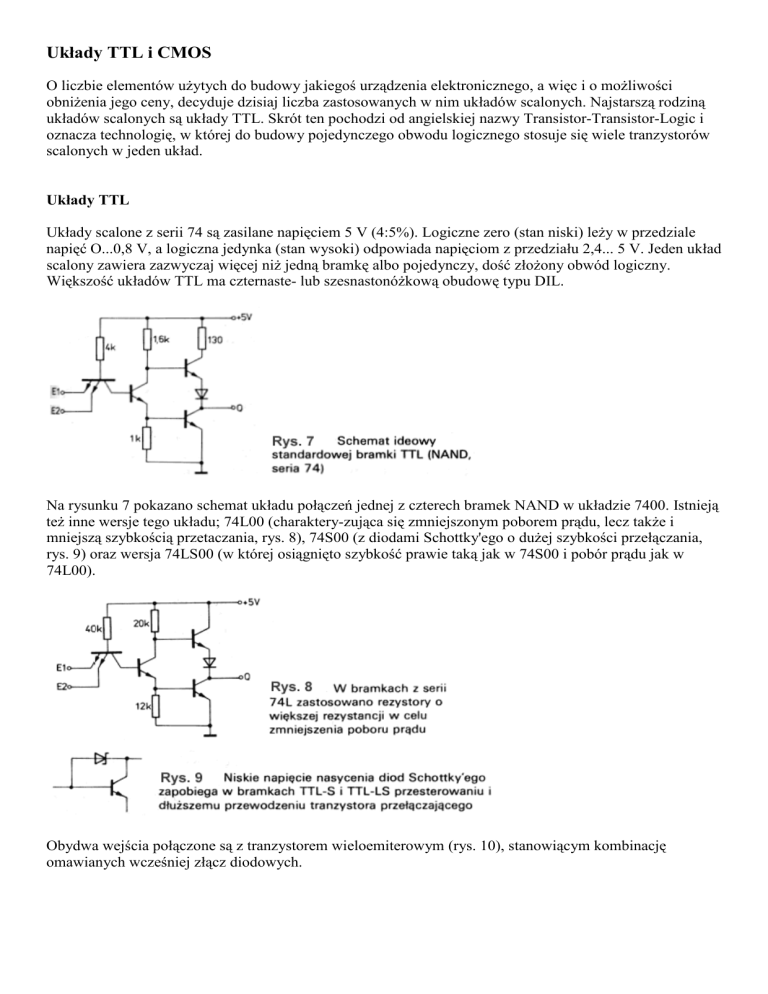

Na rysunku 7 pokazano schemat układu połączeń jednej z czterech bramek NAND w układzie 7400. Istnieją

też inne wersje tego układu; 74L00 (charaktery-zująca się zmniejszonym poborem prądu, lecz także i

mniejszą szybkością przetaczania, rys. 8), 74S00 (z diodami Schottky'ego o dużej szybkości przełączania,

rys. 9) oraz wersja 74LS00 (w której osiągnięto szybkość prawie taką jak w 74S00 i pobór prądu jak w

74L00).

Obydwa wejścia połączone są z tranzystorem wieloemiterowym (rys. 10), stanowiącym kombinację

omawianych wcześniej złącz diodowych.

Kolektor tego tranzystora może być w stanie wysokim tylko wówczas, gdy obydwa wejścia będą w tym

stanie, czyli gdy żadna z końcówek dołączonych do dolnego końca rezystora bazowego nie jest zwarta do

masy. Połączony z tranzystorem inwerter będzie wtedy wysterowany, tak aby dolny tranzystor wyjściowy

(na schemacie) przewodził, a górny był zatkany, co oznacza stan niski na wyjściu.

Istnieją też scalone układy TTL zawierające w obwodzie wyjściowym tylko jeden tranzystor z tzw.

otwartym kolektorem (rys. 11). Możliwe jest wówczas przełączanie napięć wyjściowych wyższych niż 5 V

(np. do 20 V w układzie 7406). Oczywiste jest, że dopóki takie wyjście nie jest nigdzie podłączone, to nie

można zmierzyć na nim żadnego napięcia.

Nigdzie nie podłączone wejścia układu TTL znajdują się w stanie l (w stanie wysokim), co wynika z

zastosowania tranzystora wieloemiterowego. Można więc wykorzystać bramkę NAND jako inwerter,

używając pojedynczego wejścia lub obydwu wejść połączonych ze sobą.

W niezupełnie "cyfrowy" sposób (rozpatrując to od strony wejścia) pracuje tzw. przerzutnik Schmitta:

przekształca on zmieniający się monotonicznie sygnał wejściowy na "czysto" cyfrowy sygnał wyjściowy

(rys. 12).

Uniwibratory (zwane też przerzutnikami monostabilnymi) są wykorzystywane do formowania impulsów o

czasie trwania określonym przez odpowiednio dobrane wartości rezystancji i pojemności. Dla takiego

obwodu obowiązuje zależność:

T=R*C

gdzie:

T - czas trwania wytwarzanego impulsu [s],

R - rezystancja [ohm],

C - pojemność [F].

Przykładowo, dla C = 1 uF i R = 1 M otrzymujemy T = 1 s.

Uniwibratory, w których impuls wejściowy przychodzący w czasie trwania impulsu wyjściowego wydłuża

go odpowiednio, nazywane są uniwibratorami z podtrzymaniem (rys. 13).

Układy CMOS

Układy wykonane w technologii TTL są mało przydatne do budowy urządzeń zasilanych z baterii, gdyż już

jedna bramka pobiera prąd o natężeniu kilku miliamperów, a w przypadku np. dekodera adresów w

komputerze bramek takich jest dość dużo. Wynika stąd również, że nawet w urządzeniach wyposażonych w

zasilacz sieciowy pojawi się problem odprowadzania dużych ilości ciepła wytwa-rzanego przez prąd

płynący w układach TTL.

W technologii CMOS stosuje się dwa komplementarne tranzystory polowe MOS (rys. 14). Jak już

wspomniano wcześniej, elektroda sterująca (bramka) jest całkowicie odizolowana od kanału dren-źródło i

nie pobiera żadnego prądu. Aby przez kanał również nie płynął prąd, łączy się po prostu szeregowo

tranzystor z kanałem typu p z tranzystorem z kanałem typu n. W takim obwodzie tylko jeden z tranzystorów

może być w stanie przewodzenia. Na rysunku 15 pokazano schemat zbudowanego właśnie w ten sposób

inwertera.

Jeżeli na wejściu E pojawi się stan wysoki, to będzie przewodził dolny tranzystor (z kanałem typu n), górny

zaś (z kanałem typu p) będzie zablokowany. Wyjście Q przejdzie więc w stan niski. Sytuacja odwróci się,

jeśli na wejściu E pojawi się stan wysoki: wówczas będzie przewodził tranzystor górny, co prowadzi do

pojawienia się stanu wysokiego na wyjściu.

Prąd w takim obwodzie płynie tylko podczas przełączania (rys. 16) i to tylko wtedy, gdy w pewnym

zakresie napięć wejściowych obydwa tranzystory MOSFET przewodzą (wartości tych napięć zależą od

domieszkowania półprzewodnika i od napięcia zasilania) lub gdy są ładowane różne pojemności

wewnętrzne i zewnętrzne. Ładowanie pojemności wewnątrz układu scalonego i w obwodzie zewnętrznym

prowadzi do tego, że pobór prądu przez bramki CMOS jest, w dobrym przybliżeniu, wprost proporcjonalny

do częstotliwości przełączeń (rys. 17).

Oczywiste jest też, że częstotliwość 1 MHz odpowiada dwom milionom przełączeń na sekundę (w obydwu

kierunkach).

Na rysunku 18 pokazano porównanie poboru prądu w funkcji częstotliwości pracy dla bramek wykonanych

za pomocą różnych technologii: CMOS, TTL i TTL-LS. Pobór prądu przez układy TTL i TTL-LS nie zależy

praktycznie od częstotliwości. Wynika też stąd, że powyżej pewnej wartości częstotliwości (wyróżnionej

przez punkt przecięcia się wykresów), układy CMOS pobierają w rzeczywistości większy prąd niż układy

TTL! Zjawisko to zachodzi jednak przy tak dużych częstotliwościach przełączania, że w komputerach nie

mamy z nim praktycznie do czynienia. Układy CMOS mają też dodatkową zaletę: poziom przełączania jest

w nich równy w przybliżeniu połowie wartości napięcia zasilania, a więc impulsy zakłócające muszą tę

wartość przekroczyć, aby mogły wpływać na pracę układu. Inaczej jest w układach TTL: poziom

przełączania wynosi tu ok. 0,6 V (przy napięciu zasilania równym 5 V). Oprócz tego napięcie zasilające

układy TTL musi zawierać się w przedziale od 4,75 do 5,25 V, a układy CMOS pracują przy napięciach

3...15 V.

Jako wadę logicznych układów CMOS należy podkreślić małą obciążalność ich układu wyjściowego (do

kilku miliamperów), co może stać się czynnikiem krytycznym już przy podłączeniu diody

elektroluminescencyjnej. W przeciwieństwie do tego układy TTL dostarczają prąd o natężeniu 10...40 mA.

Naturalnie, powstaje tu pytanie, czy można łączyć układy CMOS i układy TTL ze sobą? Oczywiście,

można, lecz należy wówczas przestrzegać kilku następujących zasad:

•

•

•

Układy CMOS muszą być zasilane napięciem 5 V, tak jak układy TTL.

Jedno wyjście układu CMOS może sterować jednym wejściem układu TTL.

Do sprzężenia wejścia CMOS z wyjściem TTL najkorzystniej jest stosować układy TTL z otwartym

kolektorem (rys. 18).

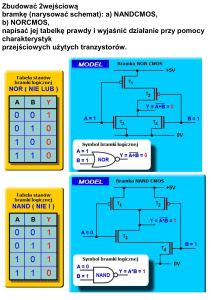

Na rysunku 19 pokazano wewnętrzną budowę bramki NAND wykonanej w technologii CMOS, Jeśli np.

obydwa wejścia znajdą się w stanie wysokim, to będą przewodzić dwa dolne tranzystory z kanałem typu n, a

obydwa górne, połączone równolegle tranzystory z kanałem typu p, będą zablokowane i dlatego wyjście

przejdzie w stan niski. Liniowa zależność rezystancji kanału od napięcia dren-źródło w tranzystorach FET

umożliwia zbudowanie przełączników elektronicznych CMOS, które mogą przełączać bez zniekształceń

również sygnały analogowe. Na rysunku 20 przedstawiono schemat takiego przełącznika analogowego. Jego

rezystancja w stanie wyłączenia jest bardzo duża (rzędu MOhm), natomiast rezystancja wewnętrzna w stanie

włączenia zawiera się na ogól w przedziale 100...300 Ohm.

Literatura:

http://www.forum.invisionresources.pl/topic/315

http://pl.wikipedia.org/wiki/TTL

http://www.arczer.neostrada.pl/cd010.htm

http://pl.wikipedia.org/wiki/CMOS

http://www.i-slownik.pl/1,271,cmos.html

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-300x300.png)