Katalog

układów

scalonych

CMOS

1

Wprowadzenie do układów scalonych

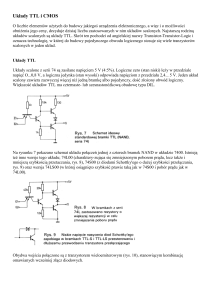

Układy wykonane w technologii TTL są mało przydatne do budowy urządzeń zasilanych z baterii,

gdyż już jedna bramka pobiera prąd o natężeniu kilku miliamperów, a w przypadku np. dekodera adresów w

komputerze bramek takich jest dość dużo. Wynika stąd również, że nawet w urządzeniach wyposażonych w

zasilacz sieciowy pojawi się problem odprowadzania dużych ilości ciepła wytwa-rzanego przez prąd płynący w

układach TTL.

W technologii CMOS stosuje się dwa komplementarne tranzystory polowe MOS (rys. 14). Jak już

wspomniano wcześniej, elektroda sterująca (bramka) jest całkowicie odizolowana od kanału dren-źródło i nie

pobiera żadnego prądu. Aby przez kanał również nie płynął prąd, łączy się po prostu szeregowo tranzystor z

kanałem typu p z tranzystorem z kanałem typu n. W takim obwodzie tylko jeden z tranzystorów może być w

stanie przewodzenia. Na rysunku 15 pokazano schemat zbudowanego właśnie w ten sposób inwertera.

Jeżeli na wejściu E pojawi się stan wysoki, to będzie przewodził dolny tranzystor (z kanałem typu

n), górny zaś (z kanałem typu p) będzie zablokowany. Wyjście Q przejdzie więc w stan niski. Sytuacja odwróci

się, jeśli na wejściu E pojawi się stan wysoki: wówczas będzie przewodził tranzystor górny, co prowadzi do

pojawienia się stanu wysokiego na wyjściu.

2

Prąd w takim obwodzie płynie tylko podczas przełączania (rys. l6) i to tylko wtedy, gdy w

pewnym zakresie napięć wejściowych obydwa tranzystory MOSFET przewodzą (wartości tych napięć zależą od

domieszkowania półprzewodnika i od napięcia zasilania) lub gdy są ładowane różne pojemności wewnętrzne i

zewnętrzne. Ładowanie pojemności wewnątrz układu scalonego i w obwodzie zewnętrznym prowadzi do tego,

że pobór prądu przez bramki CMOS jest, w dobrym przybliżeniu, wprost proporcjonalny do częstotliwości

przełączeń (rys. l7).

Oczywiste jest też, że częstotliwość l MHz odpowiada dwom milionom przełączeń na sekundę (w

obydwu kierunkach).

Na rysunku 18 pokazano porównanie poboru prądu w funkcji częstotliwości pracy dla bramek

wykonanych za pomocą różnych technologii: CMOS, TTL i TTL-LS. Pobór prądu przez układy TTL i TTL-LS

nie zależy praktycznie od częstotliwości. Wynika też stąd, że powyżej pewnej wartości częstotliwości

(wyróżnionej przez punkt przecięcia się wykresów), układy CMOS pobierają w rzeczywistości większy prąd niż

układy TTL! Zjawisko to zachodzi jednak przy tak dużych częstotliwościach przełączania, że w komputerach nie

mamy z nim praktycznie do czynienia. Układy CMOS mają też dodatkową zaletę: poziom przełączania jest w

nich równy w przybliżeniu połowie wartości napięcia zasilania, a więc impulsy zakłócające muszą tę wartość

przekroczyć, aby mogły wpływać na pracę układu. Inaczej jest w układach TTL: poziom przełączania wynosi tu

ok. 0,6 V (przy napięciu zasilania równym 5 V). Oprócz tego napięcie zasilające układy TTL musi zawierać się

w przedziale od 4,75 do 5,25 V, a układy CMOS pracują przy napięciach 3...15 V. Jako wadę logicznych

układów CMOS należy podkreślić małą obciążalność ich układu wyjściowego (do kilku miliamperów), co może

stać się czynnikiem krytycznym już przy podłączeniu diody elektroluminescencyjnej. W przeciwieństwie do

tego

układy

TTL

dostarczają

prąd

o

natężeniu

10...40

mA.

3

Naturalnie, powstaje tu pytanie, czy można łączyć układy CMOS i układy TTL ze sobą?

Oczywiście, można, lecz należy wówczas przestrzegać kilku następujących zasad:

1. Układy CMOS muszą być zasilane napięciem 5 V, tak jak układy TTL.

2. Jedno wyjście układu CMOS może sterować jednym wejściem układu TTL.

3. Do sprzężenia wejścia CMOS z wyjściem TTL najkorzystniej jest stosować układy TTL z otwartym

kolektorem (rys. 18).

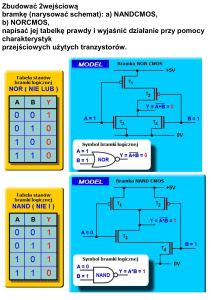

Na rysunku 19 pokazano wewnętrzną budowę bramki NAND wykonanej w technologii CMOS,

Jeśli np. obydwa wejścia znajdą się w stanie wysokim, to będą przewodzić dwa dolne tranzystory z kanałem

typu n, a obydwa górne, połączone równolegle tranzystory z kanałem typu p, będą zablokowane i dlatego

wyjście przejdzie w stan niski. Liniowa zależność rezystancji kanału od napięcia dren-źródło w tranzystorach

FET umożliwia zbudowanie przełączników elektronicznych CMOS, które mogą przełączać bez zniekształceń

również sygnały analogowe. Na rysunku 20 przedstawiono schemat takiego przełącznika analogowego. Jego

rezystancja w stanie wyłączenia jest bardzo duża (rzędu MOhm), natomiast rezystancja wewnętrzna w stanie

włączenia zawiera się na ogól w przedziale 100...300 Ohm.

4

Jak obchodzić się z układami CMOS

5

Charakterystyka i porównanie układów TTL i CMOS

Porównajmy wartości parametrów układów pochodzących z obu rodzin:

Napięcie zasilania. Układy TTL wymagają zasilania + 5 V ± 5%, podczas gdy układy CMOS pracują

poprawnie w szerszym zakresie: od + 2 V do + 6 V - układy serii HC i AC, a od + 3 V do + 15 V - układy serii

4000B i 74C. Serie HCT i ACT z rodziny CMOS, projektowane specjalnie jako zamienniki układów TTL (patrz

dalej), wymagają napięcia zasilania o wartości + 5 V.

Wejście. Wejście bramki TTL utrzymywane w stanie niskim zachowuje się, z punktu widzenia układu

sterującego, jako źródło prądowe (o typowej wydajności 0,25 mA dla układów LS-TTL). Wobec tego, aby

utrzymać stan niski, trzeba odebrać ten prąd z wejścia. Nie sprawia to większych kłopotów wtedy, gdy mamy do

czynienia tylko z układami TTL, ponieważ wyjścia TTL (nasycony tranzystor n-p-n) są w stanie wchłonąć dużo

prądu. Sprawa się komplikuje, jeżeli bramka TTL jest sterowana sygnałem z wyjścia układu innej rodziny.

Inaczej jest z układami CMOS, dla których wartość prądu wejściowego jest równa zeru. Próg przełączania

bramki TTL odpowiada dwóm spadkom napięcia na diodzie (ok. 1,3 V). Próg przełączania bramki CMOS

wynosi około 1/2 napięcia zasilania, ale może ulegać dużym wahaniom (od 1/3 do 2/3 wartości napięcia

zasilania). Układy serii HCT i ACT zaprojektowano tak, aby wartości ich napięć progowych były małe, zgodne z

wartościami napięć progowych układów TTL. Pamiętajmy, że napięcie wyjściowe bipolarnego układu TTL nie

może osiągać wartości równej + 5 V (patrz dalej). Układy CMOS są wrażliwe na zniszczenie przez ładunki

elektrostatyczne w czasie manipulacji. Dla obu rodzin nie wykorzystane wejścia powinny zostać dołączone do

napięcia poziomu wysokiego lub niskiego, zależnie od potrzeby (więcej na ten temat powiemy później).

Wyjście. Stopień wyjściowy bramki TTL w stanie niskim zachowuje się jak nasycony tranzystor

zwierający wyjście do masy, w stanie wysokim jak wtórnik (z napięciem wyjściowym na poziomie około 2

diodowych spadków napięcia poniżej wartości napięcia zasilania). Obwód wyjściowy dowolnego układu CMOS

(dotyczy to również serii HCT i ACT) jest realizowany jako dwa polowe tranzystory MOS, łączące

wyprowadzenie wyjścia z masą lub szyną dodatniego napięcia zasilającego. Oznacza to, że w tym przypadku

wartość napięcia wyjściowego może być dowolna z zakresu od 0 V do U+. Układy szybkie (serie F, AS; AC,

ACT) mają na ogół większą wydajność stopnia wyjściowego niż układy wolniejsze (LS; 4000B, 74C, HC,

HCT).

6

Szybkość i moc. Układy TTL pobierają w stanie statycznym ze źródła zasilania dość dużo prądu.

Wartość pobieranego prądu jest większa dla układów szybszych (serie AS i F). Zakres szybkości układów TTL

rozciąga się od 25 MHz dla serii LS do około 100 MHz dla serii AS i F. Układy rodziny CMOS nie pobierają w

ogóle prądu w stanie statycznym. Niemniej jednak moc zasilania rośnie w nich liniowo wraz ze wzrostem

częstotliwości (przełączanie obciążeń pojemnościowych wymaga sporych prądów) i układy CMOS pracujące

blisko górnej dopuszczalnej częstotliwości pobierają ze źródła zasilania niemal tyle samo mocy co układy TTL

(rys. 8.18). Zakres szybkości układów CMOS rozciąga się od około 2 MHz (dla układów serii 4000B/74C

zasilanych napięciem + 5 V) do około 100 MHz (dla układów serii AC/ACT.)

Rys. 8.18.

Zależność mocy rozpraszanej przez bramę od częstotliwości.

Ogólnie rzecz biorąc, dobre parametry układów CMOS (zerowa wartość spoczynkowego prądu

zasilania, zakres wartości napięcia wyjściowego od 0 V do U+, duża wartość marginesu szumowego) sprawiają,

że są to układy z przyszłością. Polecamy stosowanie układów serii HC w większości nowych projektów. W

układach o dużej szybkości przełączania należy stosować układy serii AC, w układach przeznaczonych do pracy

w szerokim zakresie wartości napięć zasilających, gdzie duża szybkość pracy nie jest konieczna - układy serii

74C lub 4000B. Jeśli jest wymagane ścisłe dostosowanie się do standardu TTL, należy używać układów serii

HCT (lub LS)-dla układów wolniejszych, i układów serii ACT (lub AS bądź F) - dla układów szybszych. W

niektórych zastosowaniach o dużej gęstości upakowania (pamięci, mikroprocesory) preferowane są układy

NMOS, pomimo ich stosunkowo dużego poboru mocy. W zastosowaniach o największych szybkościach (ponad

100 MHz) stosuje się albo układy ECL - gdy częstotliwość pracy nie przekracza 500 MHz - albo układy logiczne

bazujące na GaAs - dla częstotliwości do 4 GHz. W obrębie jednej rodziny obowiązuje zasada, że wyjścia

danego układu przystosowane są do bezpośredniego sterowania wejściami innych układów, więc nie trzeba

martwić się o progi przełączania, prąd wejściowy itp. Na przykład, w przypadku układów TTL lub CMOS z

każdego wyjścia można wysterować jednocześnie co najmniej 10 wejść (obowiązującym terminem określającym

tę cechę jest obciążalność; układy TTL mają obciążalność 10), tak że nie trzeba stosować żadnych specjalnych

środków zapewniających dopasowanie układów. W następnym rozdziale podejmiemy temat łączenia układów z

różnych rodzin oraz łączenia układów logicznych ze światem zewnętrznym.

7

Układy logiczne CMOS serii 4000

9 BRAMKI

Rozkład wyprowadzeń negatorów i buforów.

Przykłady rozwiązań stopni sprzęgających CMOS-TTL i TTL

8

4000: 2 bramki 3-wejściowe NOR oraz inwerter

4001: 2 bramki 4-wejściowe NOR

4002: 2 bramki 4-wejściowe NOR

4011: 4 bramki 2 –wejściowe NAND

9

4012: 2 bramki 4 – wejściowe NAND

4019: 4 bramki AND-OR

4023: 3 bramki 3-wejściowe NAND

4025: 3 bramki 3-wejściowe NOR

10

4030: 4 bramki Ex-OR

4069: 6 inwerterów

4071: 4 bramki 2-wejściowe OR

4072: 2 bramki 4-wejściowe OR

11

4073: 3 bramki 3-wejściowe AND

4075: 3 bramki 3-wejściowe OR

4081: 4 bramki 2-wejściowe AND

4077: 4 bramki 2-wejściowe Ex-NOR

12

4082: 2 bramki 4-wejściowe AND

13

9 DEKODERY

Dekoder 4511: a) rozkład wyprowadzeń, b) schemat wzmacniacza końcowego,

c) tabela stanów

Schemat ideowy sterowania: a) wyświetlaczem fluorescencyjnym

b) wyświetlaczem LED ze wspólną anodą

14

Dekoder 4543: a) rozkład wyprowadzeń , b)tabela stanów

Dekoder 4028: kodu BCD 1 z 10

15

9 LICZNIKI

Rozkład wyprowadzeń podwójnych liczników synchronicznych:

4518 – BCD, 4520 – binarny

Harmonogramy czasowe pracy liczników 4518 i 4520

16

Schemat ideowy kaskady asynchronicznej, oraz przebiegi ilustrujące jej pracę.

Schemat ideowy kaskady synchronicznej

17

Schemat ideowy binarnego licznika rewersyjnego

Schemat licznika o skróconym cyklu zliczania

18

Licznik rewersyjny i harmonogramy czasowe pracy licznika 4029

19

Schematy połączenia kaskadowego liczników 4029

Schemat blokowy licznika 4017

20

Przebiegi czasowe w układach liczników 4017 i 4022

Schemat wyprowadzeń liczników 4017 i 4022

21

Schemat ideowy układu rozdzielacza zbudowanego z kilku liczników 4017

Schemat ideowy układu licznika o skróconym cyklu zliczania

Schemat ideowy układu licznika o skróconym cyklu zliczania z przerzutnikiem RS.

22

Rozkład wyprowadzeń liczników 40102 i 40103 i tabela funkcjonalna.

Harmonogramy czasowe pracy liczników 40102 i 40103

23

Rozkład wyprowadzeń liczników 4510 i 4516

Harmonogramy czasowe pracy liczników 4510 i 4516

24

Rozkład wyprowadzeń liczników 40192 i 40193 wraz z tabelą stanów

Schemat szeregowego połączenia liczników

25

Harmonogramy czasowe pracy liczników 40192 i 40193

26

Rozkład wyprowadzeń liczników asynchronicznych 4020, 4024, 4040. 4060

Harmonogramy czasowe pracy liczników asynchronicznych 4020,4024, 4040, 4060

Schemat ideowy kaskadowego połączenia liczników asynchronicznych 4020, 4024, 4040, 4060

27

Rozkład wyprowadzeń układów 4054, 4055, 4056

Przykłady zasilania układów 4054, 4055, 4056

Tabela stanów układów 4055 i 4056

28

4029: Uniwersalny rewersyjny licznik binarny / dekadowy

8-stanowy, ustawiany, synchroniczny licznik w dół

4102: 2 dekady BCD

4103: 8-bitowy binarny

4518: 2 liczniki BCD

29

4520: 2 4-bitowe liczniki binarne

30

9 PRZERZUTNIKI

Konwersje przerzutników

31

Przerzutniki D: 4013 i JK: 4027, 4095 i 4096

Zastosowanie przerzutników JK i D do podziału częstotliwości przez dwa

Realizacja dzielników przez dwa z wejściem zezwalającym

32

Rozkład wyprowadzeń układów 40174 i 40175

Rozkład wyprowadzeń zatrzasków latch 4042

33

Schematy funkcjonalne przerzutników RS

Zastosowanie przerzutników 4043 i 4044 w układach eliminacji drgań styków

Rozkład wyprowadzeń przerzutników RS 4043 i 4044

34

Rozkład wyprowadzeń układów ośmiobitowych zatrzasków adresowalnych 4099 i 4724

Rozkład wyprowadzeń układu 4-bitowych zatrzasków z wyjściami trójstanowymi 4076

4013: 2 przerzutniki typu D oraz tabela przejść

35

4027: 2 przerzutniki JK Master Slave z wejściami ustawiającymi i kasującymi

4047: Multiwibrator monostabilny/astabilny o małym poborze mocy

4099: 8-bitowy adresowalny zatrzask (latch)

36

4724: 8-bitowy adresowalny przerzutnik typu zatrzask

37

9 WYŚWIETLACZE

Przebiegi sterujące pracą wyświetlacza ciekłokrystalicznego

Połączenie układów 4055 z wyświetlaczem ciekłokrystalicznym

Zastosowanie układu 4054 do sterowania

38

Połączenie układów 4056 z wyświetlaczem ciekłokrystalicznym

Połączenie układów 4054 i 4056 z typowym wyświetlaczem ciekłokrystalicznym 3 i ½ cyfry

Przykład sterowania wyświetlaczem LED: a) ze wspólną anodą, b) ze wspólną katodą

39

Schemat ideowy sterowania:

a) wyświetlaczem LCD

b) wyświetlaczem LED ze wspólną anodą

40

9 SUMATORY , REJESTRY i PLL

4008: 4-bitowy pełny sumator

4035: 4-bitowy rejestr przesuwający z wejściem równoległym i wyjściem równoległym

4046: Pętla synchronizacji fazowej (PLL)

41

42

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-300x300.png)