Technika Cyfrowa 2

wykład 4:

FPGA – odsłona druga

technologie i rodziny układów logicznych

Dr inż. Jacek Mazurkiewicz

Katedra Informatyki Technicznej

e-mail: [email protected]

Elementy poważniejsze

Zegar (1)

Zegar (2)

Bloki wejścia-wyjścia

FPGA jednolite nie są

FPGA kontra ASIC

Zalety i wady FPGA

Proces projektowania

Układ kombinacyjny raczej prosty

Realizacja w AHDL (1)

Realizacja w AHDL (2)

Realizacja w VHDL

Przykład 2 – translator kodu

Opis w VHDL (1)

Opis w VHDL (2)

Tranzystor łącznikiem dwustanowym (1)

Tranzystor łącznikiem dwustanowym (2)

Uzaś

A

YA

RC

We

RB

Wy

NOT

Czas przełączania – ważna rzecz (1)

Czas przełączania – ważna rzecz (2)

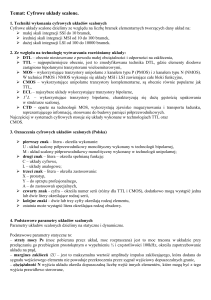

Rodziny układów cyfrowych

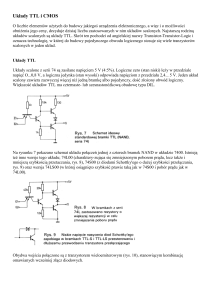

TTL (Transistor – Transistor - Logic) – układy TTL

ECL (Emiter – Coupled Logic) – układy o sprzężeniu emiterowym

MOS (Metal – Oxide - Semiconductor) – układy MOS

CMOS (Complementary MOS) – układy komplementarne MOS

BiCMOS (Bipolar CMOS) – układy „mieszane”, bipolarne CMOS

I2L (Integrated Injection Logic) – układy iniekcyjne

CTD (Charge Transfer Device) – układy o sprzężeniu ładunkowym

GaAs MESFET – układy GaAs

Czas życia technologii

Układy TTL ustępują miejsca nowszym technologiom CMOS

i BiCMOS, zwłaszcza niskonapięciowym (LV – Low Voltage)

Warunki projektowania

Przy projektowaniu urządzeń z cyfrowymi układami

scalonymi istotne są następujące parametry:

∗ szybkość działania,

∗ moc strat,

∗ odporność na zakłócenia,

∗ zgodność łączeniowa i obciążalność

Przy konstrukcji systemów cyfrowych powinny być

znane właściwości obudów oraz niezawodność

cyfrowych układów scalonych.

Układ z obciążeniem

UCC (VCC) - napięcie zasilania

ICC – prąd zasilania

UI (UO) – napięcie wejściowe (wyjściowe)

Proces przełączania bramki TTL

Porównanie szybkości działania

t pHL t pLH

tp

2

TTL do 500MHz,

GaAs do 20GHz,

ECL do 5GHz.

Częstotliwości graniczne pracy

S - bardzo szybka (Schottky)

LS - małej mocy, bardzo szybka

(Low power Schottky)

F

- bardzo bardzo szybka (Fast)

AS - ulepszona, bardzo szybka

(Advanced Schottky)

ALS - ulepszona małej mocy, bardzo szybka

(Advanced Low power Schottky)

Straty mocy w funkcji częstotliwości

Zakłócenia w systemie cyfrowym

•napięcie zasilające

•uziemienie

•przesłuch w liniach transmisyjnych

•odbicia w liniach transmisyjnych

•zewnętrzne

Marginesy zakłóceń

Marginesy zakłóceń wskazują, jaki poziom zakłóceń nie spowoduje

błędnego odczytu sygnału wejściowego w najgorszym przypadku.

ULI max -ULO max - margines zakłóceń stanu niskiego

UHO min -UHI min - margines zakłóceń stanu wysokiego

CMOS

UDD = + 5 V

ULO

ULI

UHO

UHI

0

1

2

3

4

5

stany wyjściowe

stany wejściowe

Serie TTL

W technice TTL są produkowane serie:

TTL

S

LS

F

AS

ALS

– standard TTL 74

– bardzo szybka (Schottky) 74S

- małej mocy bardzo szybka (Low Power Schottky) 74LS

– bardzo bardzo szybka (Fast) 74F,

– ulepszona bardzo szybka (Advanced Schottky) 74AS

- ulepszona małej mocy bardzo szybka

(Advanced Low Power Schottky) 74ALS.

Parametry TTL

• napięcie zasilające +5V (+4,75V do +5,25V),

• sygnał wyjściowy: H > 2,4V L < 0,4V,

• sygnał wejściowy: H > 2,0V L < 0,8V,

• obciążalność 10 – 48,

• współczynnik dobroci: D=tpP; 5-100 [pJ],

• maksymalna częstotliwość pracy:

• TTL (25 MHz),

• TTL-S (125 MHz) diody Schottky'ego 2x pobór mocy,

• TTL-LS (33 MHz) trochę mniejszy pobór mocy,

• TTL-F (150 MHz),

• TTL-AS (200 MHz) 10x mniejszy pobór mocy niż TTL,

• TTL-ALS (50 MHz).

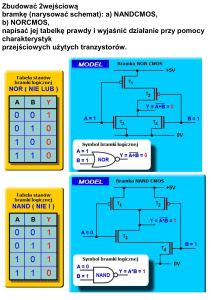

Bramka NAND TTL 7400

A

Y=A*B

B

5V

4k

1,6k 130

A

B

Y=A*B

1k

A

H

L

H

L

B

H

H

L

L

Y

L

H

H

H

Charakterystyka przejściowa NAND TTL

zależność charakterystyki przejściowej od temperatury

Inwerter NOT 7404

symbol

graficzny

Tranzystor Schottky’ego

Bramka NAND TTL Schottky-ego (S)

Korektor charakterystyki

przejściowej

Charakterystyka

przejściowa

bardziej

prostokątna niż

serii

standardowej

Charakterystyki przejściowe TTL

Układy z wejściem Schmitt’a (1)

Własności:

• napięcia progowe oraz histereza,

• duża odporność na zakłócenia.

Zastosowania:

• przekształcanie wolnozmiennych sygnałów

na impulsy o szybkich zboczach,

• przemiana napięcia sinusoidalnego na prostokątne,

• redukcja wpływu zakłóceń,

• proste układy multiwibratorów astabilnych.

Układy z wejściem Schmitt’a (2)

Bramka NAND z otwartym kolektorem OC

Serie 74F38, 74ALS38B

symbol

graficzny

Suma (iloczyn) montażowy

Jeśli wyjścia kilku bramek

z OC zostaną połączone

do wspólnego rezystora

otrzymamy układ realizujący

tzw. sumę montażową

w logice ujemnej (wired-OR):

układ zachowuje jak bramka

NOR; iloczyn montażowy

w logice dodatniej (wired-AND)

• linie przerwań magistrali komputerowych, których zadaniem jest

sygnalizowanie, że co najmniej jedno urządzenie chce zwrócić na

siebie uwagę,

• wyjścia na magistrale zewnętrzne IEC-625 (HPIB, GPIB).

Bipolarna bramka trójstanowa

UCC=5V

R1

R2

R3

T3

T4

T1

A

T2

OE (Output Enable)

wejście zezwalające

D

Y

T5

R6

__

OE

R7

R4

R5

T7

T6

T8

R8

OE=L T6=L, T7,T8=zatkane

OE=H T7,T8=L T2,T4,T5=zatkane

Bramka trójstanowa CMOS

1

0

1 (0)

0

1

0 (1)

1

0 (1)

1 (0)

1 (0)

1

HIGH-Z

zatk

0

stan wysokiej impedancji

zatk

Sterownie szyną danych

Konflikty na magistrali

eliminuje specjalny układ

Rodzina CMOS (1)

• CMOS komplementarne tranzystory PMOS i NMOS

bez rezystorów

• bardzo mała moc strat w stanie statycznym

i przy małych częstotliwościach

• praca przy obniżonym napięciu zasilania 3.3 V (± 0,3 V),

2.5 V (±0,2 V), 1.8V (±0.15V), a nawet 0.8V

• np. straty mocy P=U2/R przy 5V i 3,3 V 52 / 3,32 ≈ 2,3 raza

• większa szybkość działania niż układy pięciowoltowe

• znaczne zmniejszenie moc strat

przy większych częstotliwościach

• niższy poziom generowanych zakłóceń

elektromagnetycznych i elektrycznych

• wyższa niezawodność pracy

Rodzina CMOS (2)

∗ Układy do zastosowań masowych, o niewielkiej

szybkości działania (układy zegarkowe,

nie programowalne układy kalkulatorowe z napięciem

zasilania 0.8 V ÷ 1,5 V).

∗ Układy programowalne (takie jak układy PLD i FPGA)

i specjalizowane (ASIC).

∗ Uniwersalne układy cyfrowe LSI i VLSI, głównie

układy mikroprocesorowe i pamięciowe.

∗ Uniwersalne układy cyfrowe SSI i MSI, stanowiące

funkcjonalne odpowiedniki układów TTL.

Rodzina CMOS (3)

Parametry CMOS i TTL

Parametry CMOS 3V

Inwerter CMOS

Charakterystyki inwertera CMOS

Budowa bramek porównawczo

A B T1 T2 T3 T4 Q

1 1 p z z

p 0

0 1 z p p

z 1

A B T1 T2 T3 T4 X T5 T6 Q

1 1 z z p

p 0 p z 1

0 1 p z z

p 1 z p 0

p – przewodzi, z - zatkany

a) Bramka NAND LS-TTL,

b) bramka AND CMOS

Inne bramki CMOS (1)

Inne bramki CMOS (2)

Charakterystyki przejściowe NOR

Poziomy napięć CMOS i TTL

Bramki BiCMOS

Technologia ECL: NOT (1)

Y=A

Y=A

A

UREF

I

UEE=-5,2V

Technologia ECL: NOR/OR (2)

220

245

907

Y=A+B

A

Y=A+B

B

4,98k

50k

50k

779

6,1k

UEE = -5,2V

Technologia I2L: NOR

1...15V

Y1=A

A

Y2=A+B

B

Y3=B

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-300x300.png)