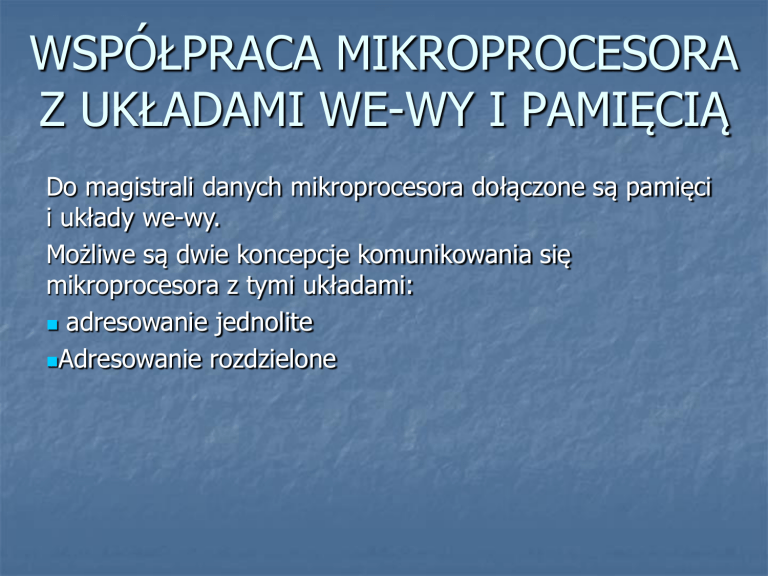

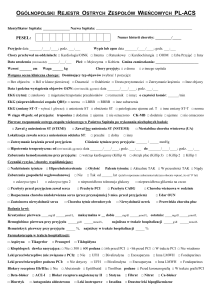

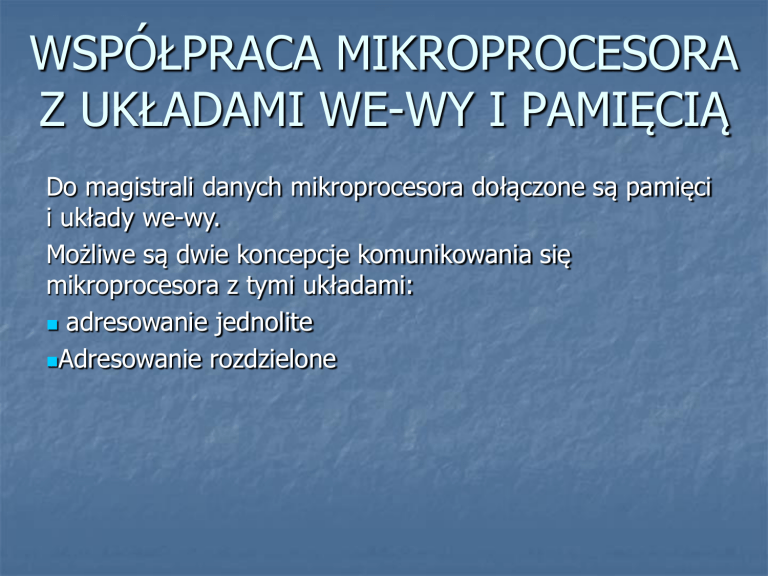

WSPÓŁPRACA MIKROPROCESORA

Z UKŁADAMI WE-WY I PAMIĘCIĄ

Do magistrali danych mikroprocesora dołączone są pamięci

i układy we-wy.

Możliwe są dwie koncepcje komunikowania się

mikroprocesora z tymi układami:

adresowanie jednolite

Adresowanie rozdzielone

ADRESOWANIE JEDNOLITE

Zalety: prostota i brak dodatkowych elementów sterujących

Wady: ograniczanie obszaru adresowego dla pamięci

ADRESOWANIE ROZDZIELONE

Ten typ adresowania może być stosowany tam gdzie mikroprocesory

wyposażone są w specjalne rozkazy we-wy i dodatkowe sygnały sterujące do

adresowania pamięci i ukł. we-wy.

Zalety: możliwość pełnego wykorzystania przestrzeni adresowej dla pamięci

Wady: dodatkowe sygnały sterujące oraz szersza lista rozkazów

obejmujących obsługę ukł. we-wy

ADRESOWANIE UKŁADU WE-WY

Do uaktywnienia układu we-wy stosuje się logiczny układ kombinacyjny zwany

dekoderem adresu. Przy określonej kombinacji sygnałów wejściowych

(adresowych) wytwarza on sygnał wybierający układ we-wy. Sygnał ten

oznacza się CS (chip select).

Bity A0 – A2 doprowadzone są bezpośrednio do układu we-wy i służą do

wyboru rejestrów wewnętrznych ustalających tryb pracy albo zawierających

informację o stanie układu we-wy. Bity A3 – A9 podawane są do dekodera

adresu, który wystawia sygnał CS

Rodzaje układów we-wy i

współpraca z mikroprocesorem

Rys. Komunikacja mikroprocesora z ukł. we-wy

Są trzy podstawowe rodzaje układów we-wy:

- Proste (na poj. tranzystorach lub bramkach przeznaczone np. do sygnalizacji

- uniwersalne (programowalne) – ukł. MSI przewidziane do wyprowadzania danych na

zewnątrz, np. port równoległy 8255 i port szer. 8251

- specjalizowane przewidziane są do obsługi konkretnego urządzenie zewnętrznego.

Wykonane są w postaci układu LSI albo VLSI. Przykładem są karta grafiki. Karta

dźwiękowa czy sieciowa

KOMUNIKACJA ZE SPRAWDZANIEM

GOTOWOŚCI

Zalety – prostota, nie są

wymagane dodatkowe

sygnały sterujące.

Wady – znaczne obciążenie

mikroprocesora

Komunikacja ze sprawdzaniem gotowosci polega na okresowym sprawdzaniu ukladow

we/wy - czy urzadzenia zewnetrzne ,,nie zycza, sobie" obstugi ze strony

mikroprocesora? W tym celu układy we/wy wyposazane sa. w tzw. rejestr stanu.

Poszczegolne bity tego rejestru mają okreslone przeznaczenie. Tzw. bit gotowosci

informuje o przygotowniu urzadzenia zewnetrznego do wspotpracy z mikrokomputerem

(np. podłączenie i wlączenie zasilania drukarki). Bit za.dania obstugi wskazuje natomiast

na potrzebe wspotpracy układu we/wy z mikroprocesorem. Sprawdzanie uktadow

we/wy polega na odczytaniu rejestru stanu i analizie aktywnosci bitu zadania obstugi.

Aktywnosc bitu zadania obslugi wymusza wykonanie podprogramu obsługi układu

we/wy.

Komunikacja z przerwaniami

Rys. Przerwanie

Rys. Wektorowy układ przerwań

Przerwanie jest wejściowym sygnałem sterującym mikroprocesora. Stan wejścia

przerwań jest analizowany wewnętrznie przez mikroprocesor pod koniec każdego

cyklu rozkazowego. Aktywny stan tego wejścia powoduje natychmiastową zmianę

adresu, która wywołuje podprogram obsługi przerwania.

Zalety- mniejsze obciążenie procesora.

Wady – większe skomplikowanie układu

KOMUNIKACJA Z BEZPOŚREDNIM

DOSTĘPEM DO PAMIĘCI

Rys. Bezpośredni dostęp do pamięci

Rys. Podłączenie układu DMA

Sygnały sterujące:

DRQ – DMA Request

DACK – DMA Acknowledge

HLDRQ – Hold Request

HLDA – Hold Acknowledge

Zalety - duża szybkość przesyłania

danych.

Wady – większe skomplikowanie układu

i konieczność stosowania dodatkowych

sygnałów sterujących

WSPÓŁPRACA Z URZĄDZENIAMI

ZEWNĘTRZNYMI

Współpraca mikrokomputera z urządzeniami zewnętrznymi odbywa się za

pomocą tzw. interfejsu. Obejmuje on fizyczne przewody i złącza, oraz

specyfikację styków i sygnałów, poziomy sygnałów (napięcia i prądu) oraz ich

zależności czasowe.

Do transmisji danych, które są sygnałami elektrycznymi, stosuje się linie

transmisyjne przewodowe oraz bezprzewodowe (radiowe i podczerwień).

PRZEWODOWE LINIE TRANSMISYJNE

Linia symetryczna to dwa przewody sygnałowe, po których przekazywany

jest ten sam sygnał, lecz w przeciwnych fazach. Dodatkowo przewody są

skręcone ze sobą. Powoduje to znaczne zredukowanie zakłóceń.

Przykładem takich linii są skrętki stosowane w sieciach komputerowych.

Zasięg – ok.. 1000m

Linia niesymetryczna - składa się z przewodu sygnałowego (gorący) oraz

„masy”. Linia taka jest bardzo podatna na zakłócenia pochodzące od

zewnętrznych pól elektrycznych i magnetycznych i dlatego stosuje się je do

połączeń na niewielkie odległosci, max. Kilka metrów.

TRANSMISJA SZEREGOWA

Rys. Układ transmisji szeregowej

Rys. Układ transmisji równoległej.

Dane mają postać tzw. Słów. Słowo jest sekwencją bitów i zwykle ma długość 8 bitów

czyli 1 Bajta. Transmisja bit po bicie nazywa się szeregową. Wymaga małej ilości

przewodów ale wydłuża czas transmisji.

Inną metodą jest transmisja równoległa, w której całe wszystkie bity słowa przesyłane

jest jednocześnie za pomocą wielu przewodów. Zwiększa to szybkość transmisji ale

jednocześnie przy większych odległościach następuje przenikanie sygnałów między

liniami i występowanie większej liczby błędów.

TRANSMISJA SZEREGOWA

Rys. Transmisja szeregowa

asynchroniczna

Rys. Ramka transmisji

szeregowej synchronicznej.

Przy transmisji asynchronicznej zegary nadajnika i odbiornika nie są synchronizowane oraz nie jest

określony odstęp czasu między kolejnymi słowami. Transmisja każdego słowa poprzedzona jest

bitem startu, a kończona bitem stopu. Dla kontroli poprawności transmisji dołączany jest bit

parzystości. Suma jedynek w słowie i bitu parzystości powinna być parzysta. Przed rozpoczęciem

transmisji powinno się ustalić parametry połączenia: szybkość transmisji w b/s np. 56600, długość

słowa (5-8 bitów), bit parzystości (jest, brak, zanegowany), ilość bitów stopu.

Transmisja synchroniczna wymaga synchronizacji zegarów nadajnika i odbiornika. Można dzięki

temu pozbyć się bitów startu i stopu, co zwiększa efektywność transmisji. Dane pogrupowane są w

bloki zwane ramkami (frame). Bajty synchronizacji umieszcza się na początku ramki. Służą one do

synchronizacji zegara odbiornika

TRANSMISJA RÓWNOLEGŁA

Transmisja równoległa odbywa się z

wykorzystaniem liczby linii

odpowiadającej długości słowa (liczbie

bitów). W jednym takcie przesyłane

jest całe słowo.

Urządzenie zewnętrzne np. drukarka

wykorzystuje sygnał strobujący do

zapisu odebranych danych. Powolne

urządzenia zewnętrzne takie jak

drukarka są wyposażone w tzw. Bufor

(pamięć RAM), w którym zapisywane

są odebrane dane. Uniezależnia to czas

trwania transmisji od czasu

przetwarzania (np. drukowania)

Sygnał strobujacy aktywny poziomem niskim jest wystawiany w wyniku iloczynu

logicznego sygnału gotowości i ustabilizowania danych. Jego zbocze opadające

wykorzystywane jest przez urządzenie zewnętrzne (odbiornik) do odczytu

informacji. Jednoczesnie odczytywane są sygnały ze wszystkich linii danych.

INTERFEJS RS232C

Jest to interfejs szeregowy, który pierwotnie był przeznaczony do podłączenia

modemu. Umożliwia połączenie urządzeń dwojakiego rodzaju:

1.DTE – Data Terminal Equipment – urz. końcowe (komputer, drukarka)

2.DCE – Data Communication Equipment – urz. komunikacyjne – modem.

W pierwotnej wersji korzystał ze złącza 25 – stykowego (DB25 albo D Sub 25). W

komputerach PC wykorzystano 9 sygnałów przez co wystarcza złącze 9-stykowe

(DB9). Najważniejsze dwa sygnały (TxD i RxD) realizują dwukierunkową transmisję

danych. Pozostałe związane są z obsługą modemu. Połączenie urządzeń DTE i DCE

wymaga stosowania przewodu połączeniowego „1:1” – tj. w obu urządzeniach łączy

się styki o tych samych numerach

INTERFEJS RS232C

Poziomy sygnałów interfejsu dla zwiększenia odporności na zakłócenia zawierają się w granicach od

-15V do +15V. W sygnale nadawanym logicznej „1” odpowiada napięcie od -5V do +15V a

logicznemu „0” napięcia +5V do +15V. Sygnał odbierany w zakresie +3 do +15V interpretowany

jest jako „0” a w zakresie -3 do -15V jako „1”. W komputerach PC RS232C stosuje napięcia ±12V.

Max szybkość transmisji 116 kb/s, max. zasięg ok. 10m.

Interfejs RS232 jest praktycznie zrealizowany przy pomocy układów UART np. 8251 lub nowszych i

szybszych 16550. Układy te pracują na sygnałach TTL dlatego dla pełnej realizacji interfejsu

stosuje się tzw. Nadajniki – odbiorniki linii, które transponują sygnały z poziomu TTL na poziom

RS232 . Nowocześniejsze wersje interfejsu szeregowego oznaczone są jako RS422 i RS485.

Pozwalają uzyskać szybkość transmisji ok. 10Mb/s oraz wydłużenie zasięgu do 1200 m. Komputery

PC wymagają do realizacji RS485 specjalnych kart rozszerzeń.

INTERFEJS CENTRONICS

Złącze Centronics jest interfejsem równoległym

przeznaczonym do podłączenia drukarki.

Posiada osiem linii danych i szereg sygnałów

sterujących i statusowych. Sygnały mają

poziom TTL. Zasięg ok.. 10m przy szybkości

transmisji ok. 128kB/s. Od strony komputera

ma postać gniazda DB25(CANON) a od strony

drukarki złącze AMP, 36-stykowe. Może

pracować w 5 trybach:

1. Compatibility Mode – zwykły

jednokierunkowy port równoległy

2. Nibble Mode – mozliwość 4-bitowej

transmisji zwrotnej wykorzystującej linie

statusowe portu

3. Byte Mode transmisja dwukierunkowa

4. EPP Mode – dodatkowa kompresja danych

INTERFEJS USB I JEGO WŁAŚCWOŚCI

Rys. Linie USB

Interfejs USB wykorzystuje tylko 4 przewody. Dwa z

nich +D i –D, są skręcone i służą do przesyłania

danych. Pozostałe dwa to przewód zasilania +5V i

masa. Pobór prądu <0,5 A.

Wykorzystano tu linię symetryczną do przesyłania

danych, adresów i sygnałów sterujących. Posiada

strukturę sieci pozwalającą na podłączenie do 127

urządzeń

Rys. Struktura interfejsu USB

Specyfikacja interfejsu USB 1.0 przewidywała dwie szybkości transmisji:

1. Niską – do 1,5 Mb/s z przewodem o długości do 3m

2. Pełną – 12Mb/s z przewodem ekranowanym o długości do 5m

USB 2.0 pozwala odznacza się znacznie lepszym transferem, nawet do 480Mb/s

W 2007 r przedstawiono specyfikację USB 3.0. Charakteryzuje się ona znacznie większym

transferem aniżeli poprzednie wersje. Max szybkość wynosi ok. 4,8 Gb/s – tzw. Super speed.

INTERFEJS Fire Wire (IEEE 1394)

Bardzo szybki interfejs szeregowy – do 400

Mb/s. Stosowany głównie do podłączenia kamer

cyfrowych do komputera. Pozwala na

podłączenie 63 urządzeń w formie segmentu

sieci o strukturze szynowej (bez

koncentratorów). Liczba segmentów może

wynosić 1024. Połączenie między segmentami

wymagają specjalnych urządzeń tzw. Mostów

(bridge). Wykorzystuje się przy tym jeden wtyk

a każde urządzenie ma co najmniej dwa

gniazda do podłączenia urządzeń sąsiednich. W

najbliższym czasie przewiduje się wzrost

szybkości transmisji do 1,2 Gb/s

Fire wire wykorzystuje dwie linie symetryczne TDA i TDB (cztery przewody) do

przesyłania danych. Umożliwia transmisję duplexową . Dodatkowe dwa przewody

służą do rozprowadzania napięcia zasilania, którego wartosć powinna się

zawierać w przedziale od 8 do 40 V. Max obciążalność 1,5 A.

INTERFEJS IEC 625 (GPIB))

Interfejs równoległy ogólnego przeznaczenia GPIB

lnterfejs l2C

Jest to interfejs wprowadzony przez firmę Philips do sterowania układami sprzętu

elektronicznego powszechnego użytku (radia, telewizory itp.). Interfejs ten znalazł

jednak zastosowanie również w sprzęcie komputerowym. Jest to interfejs szeregowy,

dwukierunkowy o strukturze szynowej. Szybkość transmisji osiąga 100 kb/s przy

częstotliwości zegara 100 kHz. Wersja Fast umożliwia maksymalną szybkość transmisji

400 kb/s. Pozwala na łączenie urządzeń sterujących (mikrokontrolerów) oraz urządzeń

wykonawczych. Urządzenie wymuszające transmisje wystawia także sygnał zegarowy i

nazywane jest Master. Urządzenie podrzędne nazywane jest Slave.

Linia SDA służy do przekazywania danych i adresów urządzeń. Linia SCL jest linią

sygnału zegarowego. Poziomy sygnałów to poziomy TTL. Wyjścia urządzeń

dołączonych do interfejsu są wyjściami typu otwarty kolektor lub otwarty dren.

Wymaga to podłączenia rezystorów podciągających R l i R2 (kilka k?). Suma liczby

układów zarządzających (master) i podporządkowanych (slave) nie może przekroczyć

128. Ograniczeniem jest sumaryczna pojemność magistrali - maksymalnie 400 pF i

maksymalna jej długość - do 4 m.

lnterfejs l2C

Każdy układ posiada adres 7-bitowy i może być nadajnikiem lub odbiornikiem

danych. Stosowana procedura arbitrażu zapobiega utracie informacji w wyniku

próby dostępu do magistrali więcej niż jednego układu zarządzającego. Dane

przesyłane są w bajtach. Możliwe jest przesyłanie danych 16-bitowych. Pierwszy

bajt zawiera adres układu podporządkowanego (7 bitów). Ósmy bit określa kierunek

transmisji. Poprawny odbiór każdego bajtu jest potwierdzany przez odbiornik. Kiedy

magistrala nie jest używana, napięcia, na liniach są zbliżone do +5 V.

Podczas transmisji dane na szynie SDA muszą być stabilne w czasie

wysokiego poziomu sygnału zegarowego. Zmiana danej może następować przy

niskim poziomie sygnału zegarowego.

lnterfejs l2C

Rozpoczęcie transmisji jest sygnalizowane tzw.

warunkiem startu. Poziom sygnału SDA zmienia

się z wysokiego na niski podczas wysokiego

poziomu sygnału SCL. Koniec transmisji

określony jest warunkiem stopu jako zmiana

sygnału SDA z niskiego na wysoki podczas

wysokiego poziomu sygnału SCL. Wymaga to

sprawdzania wartości sygnału danych na

początku i końcu wysokiego stanu linii

zegarowej.

Potwierdzenie prawidłowego odbioru

danej następuje przez wystawienie

poziomu niskiego na linii danych przez

odbiornik podczas dziewiątego impulsu

(wysokiego poziomu) sygnału

zegarowego.

Interfejs ten jest wykorzystywany do sterowania urządzeń za pomocą mikrokontrolera.

Czasami nazywany jest interfejsem 2-przewodowym. Mniejsze znaczenie mają dwa

interfejsy 3-przewodowe. Jeden o nazwie Microwire, a drugi SPI. Posiadają oddzielne

linie dla danych odbieranych i wysyłanych.

Magistrala 1-Wire

Super oszczędna magistrala 1-przewodowa powstała w firmie Dallas (która

niedawno została wchłonięta przez firmę Maxim). Magistrala ta przeznaczona jest

do dwukierunkowego przesyłania informacji między układem nadrzędnym Master i

układami podrzędnymi Slave. W roli układu Master występuje najczęściej

odpowiednio zaprogramowany mikrokontroler. Każde urządzenie dołączone do

magistrali posiada wyjście typu "otwarty dren". Dlatego linia danych wyposażona

jest w rezystor podciągający (5kΩ). Magistrala pełni rolę bramki AND na drucie.

Szybkość transmisji osiąga 16,3kb/s. W trybie "przesterowania" (Overdrive)

polegającym na skróceniu cykli czasowych można uzyskać 142kb/s. Zasięg przy

rezystorze 1kΩ i linii skręcanej osiąga 200m.

Magistrala 1-Wire

Biorąc pod uwagę tzw. przewód powrotny - masę, do realizacji tego interfejsu potrzebne

są dwa przewody. Interfejs ten stosowany jest w urządzeniach miniaturowych, gdzie

oszczędza się na wszystkim, zwłaszcza na poborze energii. Wykorzystywany jest przez

układy identyfikacji, tzw. immobilizery, pamięci EEPROM, termometry, zamki

elektroniczne itp. Istnieje specyficzna rodzina układów w formie metalowego guzika

nazywana iButton, która wykorzystuje ten interfejs. Układy podłączone do magistrali

zwykle zasilane są bezpośrednio z niej, nie posiadają odrębnych źródeł zasilania.

Ulubionym stanem dla tej magistrali jest stan bezczynności (idle) podczas którego

linia DQ znajduje się w stanie wysokim. Każde wstrzymanie transmisji kończy się

przejściem do stanu bezczynności. Wystąpienie stanu niskiego przez czas dłuższy niż

120 μs powoduje wyzerowanie wszystkich układów podłączonych do magistrali.

Transmisja danych opiera się na czterech charakterystycznych

sekwencjach. Są to:

- inicjalizacja (zerowanie i zgłoszenie),

- zapis 0,

- zapis l,

- odczyt bitu.

Magistrala 1-Wire

Inicjalizacja przeprowadzana jest przez układ Master, który w tym celu wystawia poziom

niski na czas 480 - 960 (Is. Następnie przechodzi do odbioru, wystawiając poziom

wysoki. Oczekuje na zgłoszenie układu Slave. Układ Slave informuje o podłączeniu do

magistrali poziomem niskim trwającym 60 - 240 (ls. Dopiero teraz układ master może

przejść do wyboru układu Slave i wysyłania lub odbioru informacji. Zapis i odczyt bitów

odbywa się w tzw. szczelinie czasowej trwającej 60 - 120 μs i wymuszanej przez Master

poziomem niskim. Poziom niski przez czas trwania szczeliny oznacza 0. Zmiana na

poziom wysoki na początku szczeliny odpowiada l.

Skomplikowana jest identyfikacja i wybór urządzeń podłączonych do magistrali.

Każde posiada 64-bitową pamięć ROM, gdzie zapisany jest 8-bitowy numer rodziny

układów, 48-bitowy niepowtarzalny numer identyfikacyjny i 8 bitów sumy kontrolnej

CRC. Dopiero po przeprowadzeniu identyfikacji uzyskuje się dostęp do funkcji

charakterystycznych dla urządzenia. Jeśli podłączony jest tylko jeden układ Slave,

można pominąć procedurę identyfikacji wysłaniem komendy OCCH.

Magistrala 1-Wire

Do obsługi pamięci ROM (identyfikacji wykorzystuje się następujące polecenia:

Read ROM [33h] - odczyt całej zawartości ROM, możliwy tylko w przypadku podłączenia jednego

urządzenia Slave,

Match ROM [55h] - poprzedza wysłanie 64-bitowego adresu urządzenia i pozwala

na szybki wybór urządzenia (wymagana znajomość adresu),

Skip ROM [CCh] - pominięcie identyfikacji, możliwe tylko w przypadku podłączenia

jednego urządzenia Slave,

Search ROM [FOh] - rozpoczyna proces eliminacji w celu identyfikacji 64-bitowego

adresu urządzenia podłączonego do magistrali.

Po komendzie Search ROM rozpoczyna się powtarzanie trzech czynności realizowane przez

program mikrokontrolera dla każdego z 64 bitów: odczyt bitu, odczyt zanegowanej wartości bitu

(obydwa odczyty iloczynu logicznego wyjść wszystkich podłączonych układów) i wysłanie l lub 0.

Wysłanie l lub 0 eliminuje (wprowadza w stan bezczynności) układy, które na tej pozycji adresu

mają inną wartość. Inne wartości odczytywane są jako 00. Jeśli wszystkie układy na tej pozycji

mają wartość l, zostaje odczytana kombinacja 10 i wysłane 1. Jeśli wszystkie mają 0 to zostanie

odczytana kombinacja 01 i wysłane 0. W ten sposób są eliminowane (odłączane) układy oprócz

jednego, którego adres jednocześnie zostanie wystawiony i zapisany w pamięci mikrokontrolera.

Powtarzając instrukcję Search ROM, można znaleźć adresy wszystkich układów podłączonych do

magistrali.

Magistrala 1-Wire pozwala na realizację sieci komputerowej, która nazywana jest Micro LAN. W

tym przypadku niezbędne jest sekwencyjne powtarzanie operacji Search ROM dla wykrycia

podłączanych urządzeń.

Interfejs CAN

Interfejs CAN stosuje transmisję szeregową asynchroniczną, korzystając z linii

symetrycznej. Posiada on strukturę otwartą i liniową, można do niego podłączać kolejne

urządzenia i nie zawiera pętli. Zasadniczym zastosowaniem jest motoryzacja, ale

spotykany jest również w urządzeniach przemysłowych i medycznych.

Symetryczna linia transmisyjna zakończona jest rezystorami zapobiegającymi odbiciom

w linii tzw. terminatorami o rezystancji R=124 Ω. Podłączenie do linii następuje za

pomocą nadajników/odbiorników linii. Realizują one funkcję logiczną „iloczynu na

drucie" (ang. Wired AND). Jeśli nie są przesyłane informacje, szyna znajduje się w

stanie R (l - logiczne). Wymuszenie dostępu odbywa się przez wystawienie poziomu

niskiego D (0). Dane przesyłane są z wykorzystaniem metody NRZ.

Interfejs CAN

Maksymalna szybkość transmisji wynosi l Mb/s przy długości linii do 40 m.

Stosowane identyfikatory 11-bitowe pozwalają na podłączenie 2048 urządzeń.

Najnowsza wersja, tzw. rozszerzony CAN wykorzystuje identyfikator 29-bitowy i

pozwala na zaadresowanie 536 milionów urządzeń. Rozbudowany system

zabezpieczeń przed błędami transmisji sprawia, że jest on jednym z najbardziej

niezawodnych sposobów przesyłania danych w systemach z mikrokontrolerami.

Interfejs bezprzewodowy Bluetooth

Urządzenia łączone za jego pomocą przypominają telefon komórkowy.

Posiadają antenę A wysyłającą lub odbierającą fale radiowe, układ transceivera

(nadajnik-odbiornik) wielkiej częstotliwości RF, układ kodujący i dekodujący sygnał

oraz zapewniający połączenie z mikrokomputerem czy urządzeniem zewnętrznym,

zwany procesorem pasma podstawowego BBP (Base Band Processor). Strukturę

części transmisyjnej interfejsu pokazuje rysunek poniżej:

Tor ten jest łączony za pomocą typowego interfejsu (INT), np. USB z

mikrokomputerem czy urządzeniem zewnętrznym. Rozwiązania techniczne interfejsu

zmierzają w kierunku minimalizacji kosztów dla uzyskania jego powszechnego

stosowania. Tor radiowy (RF) wykorzystuje do transmisji nielicencjonowaną

częstotliwość 2,4 GHz. Pasmo transmisyjne obejmuje 79 kanałów odległych od

siebie co l MHz (od 2,402 GHz do 2,480 GHz). Stosowana jest technika skokowej

automatycznej zmiany częstotliwości. Przy nawiązywaniu łączności wybierane są

wolne kanały z szybkością 1600 skoków/s. Bardzo mała moc wyjściowa (l mW)

umożliwia uzyskanie zasięgu do 10 m. Po zwiększeniu mocy wyjściowej do 100 mW

zasięg może osiągnąć 100 m.

Interfejs IrDA (ang. Infrared Data Association)

Jest to grupa (powstała w 1993 r.), skupiająca kilkudziesięciu producentów sprzętu

komputerowego. Celem jej powstania było stworzenie i kontrolowanie

międzynarodowych standardów transmisji danych w zakresie podczerwieni. Grupa ta

opracowała firmowy system bezprzewodowej transmisji danych cyfrowych z

wykorzystaniem promieniowania podczerwonego. Jego elementy przeznaczone są

przede wszystkim do tworzenia sieci tymczasowych, w których znajdują się komputery

przenośne.

Standard ten charakteryzuje się:

- prostą i tanią implementacją,

- małym poborem mocy,

- połączeniami bezpośrednimi typu punkt-punkt,

- wydajnym i pewnym transferem danych.

Podstawowe usługi, wymienione w opisie systemu obejmują:

- przesył plików między komputerami,

- drukowanie,

- dostęp do zasobów sieci przewodowej,

- transmisja danych i mowy między komputerem a telefonem komórkowym,

- sterowanie urządzeniami telekomunikacyjnymi.

Technologia IrDA wykorzystuje skupioną wiązkę światła w paśmie podczerwonym.

Warunkiem zastosowania IrDA jest posiadanie co najmniej dwóch urządzeń, pomiędzy

którymi nie ma niczego, co by utrudniało ich wzajemną widoczność.

Interfejs IrDA (ang. Infrared Data Association)

Parametry:

1.Długość fali 850 – 900 nm

2. Typ połączenia punkt-punkt

3. Liczba kanałów Jeden – do transmisji danych

4. Prędkość transmisji 9,6 kb/s, opcjonalnie: 19,2; 38,4 ; 57,6; 115,2kb/s (IrDA

1.0 lub 1.1) oraz 0,1576 Mb/s, 1,152 Mb/s, 4 Mb/s (IrDA 1.1)

5. Zasięg i typ transmisji - do 11 m; urządzenia muszą się "widzieć"; kąt wiązki

transmisji 30°

6. Maksymalna liczba aktywnych urządzeń21 połączeń

7. Multipleksacja - przestrzenna

8. Bezpieczeństwo na poziomie łącza

9. Emulacja portu - szeregowy + równoległy

Standard łączności oparty na przesyłaniu danych za pomocą światła podczerwonego

(IrDA), staje się obecnie szeroko dostępnym na komputerach osobistych oraz innych

urządzeniach zewnętrznych, jest to niedroga oraz efektywna łączność między

urządzeniami różnego typu. Standard IrDA rozwijał się bardzo szybko (w

porównywaniu do innych standardów), a informacja dotycząca protokołów Irda znana

jest już i stosowana na całym świecie. Obecnie specyfikacja IrDA uległa przyśpieszeniu

ze względu przystosowanie jej do standardu ISO. Komunikując się przy pomocy

protokołu mamy do czynienia z wieloma zagadnieniami, powszechnie wykorzystuje się

z podstawowe warstwy protokołu. Jeśli jednak chcemy zapewnić bezpieczeństwo oraz

elastyczność w przesyłaniu danych korzysta się także z innych warstw.

Interfejsy dysków twardych

IDE ATA

IDE i ATA, (Integrated Drive Electronic (IDE)

Rodzaj interfejsu, w którym całość logiki sterownika dyskowego przeniesiono do

konstrukcji dysku, ATA zaś to AT Attachment – relacja interfejsu do konstrukcji AT.

Ostatnia wersja - ATA-4 (Ultra ATA) pozwalała na transfer do 33 MB/s

Został wyparty przez SATA

Interfejsy dysków twardych

SATA

SATA (ang. Serial Advanced Technology Attachment) - szeregowa magistrala Serial ATA jest

następcą równoległej magistrali ATA. Do transmisji przewidziane są cieńsze i bardziej elastyczne

kable z mniejszą ilością styków, co pozwala na stosowanie mniejszych złączy na płycie głównej w

porównaniu do równoległej magistrali ATA. Interfejs przeznaczony do komunikacji z

przepływnością 150 MB/s, umożliwiający szeregową transmisję danych między kontrolerem a

dyskiem komputera z przepustowością ok. 1,5 Gb/s.

Dodatkowo budowa kabli upraszcza instalację i prowadzenie ich w obudowie, co poprawia

warunki chłodzenia wewnątrz obudowy.

Obecnie w sprzedaży dostępne są dyski z kontrolerem wyposażonym w magistralę SATA-2, która

umożliwia dwukrotnie większy transfer niż jej poprzednik. Planowana jest też trzecia wersja tego

interfejsu, która ma umożliwić przesyłanie danych z prędkością 600 MB/s.

Wtyczka danych SATA

Wtyczka zasilania

Interfejsy dysków twardych

SATA

Długość przewodu SATA może dochodzić do 1 metra.

Opracowano trzy generacje interfejsu SATA. Pierwsza, najstarsza wersja SATA I umożliwia

szeregową transmisję danych z maksymalną przepustowością 1,5 Gbit/s (ok. 180 MB/s). Druga

generacja (SATA II) oferuje przepustowość 3,0 Gbit/s (ok. 375 MB/s). Trzecia generacja (SATA

3), zaprezentowana oficjalnie po raz pierwszy 27 maja 2009 roku udostępnia przepustowość 6,0

Gbit/s (ok. 750 MB/s).

Złącze eSATA (external SATA) to zewnętrzny port SATA 3

Gbit/s, przeznaczony do podłączania pamięci masowych

zewnętrznych. Główną ideą eSATA jest zapewnienie

identycznej prędkości przesyłania danych w urządzeniach

zewnętrznych, jaka osiągalna jest dla napędów

wewnętrznych. Osiągane przez ten standard prędkości nie

odbiegają od tych oferowanych przez SATA II – maksymalne

przepustowości to 150 MB/s oraz 300 MB/s. Jest to prędkość

znacznie większa niż maksymalna prędkość przesyłania

danych przez port USB 2.0 (480 Mbit/s czyli 57 MB/s), a

porównywalna do prędkości złączy USB 3.0. Maksymalna

Porównanie wtyczek SATA i eSATA

długość kabla eSATA może wynosić 2 metry

xSATA to rozwinięcie standardu eSATA. Jest to zewnętrzne połączenie SATA o długości do 8

metrów przy użyciu ekranowanych kabli i złącz.

mSATA (mini-SATA) to złącza SATA. W związku z wciąż postępującą miniaturyzacją pamięci

masowych oraz elektroniki w komputerach mobilnych, SATA-IO opracowała nową generację złącza

do zastosowań w takich urządzeniach jak netbooki oraz dyski SSD 1.8". Maksymalna

przepustowość mSATA wynosi 3 Gbit/s.

Interfejsy dysków twardych

SCSI

Standard SCSI umożliwia połączenie w łańcuch do jednego kontrolera 7, a w

przypadku wersji rozszerzonej WIDE SCSI nawet do 16 urządzeń (łącznie z

kontrolerem). Dla porównania standard EIDE obsługuje tylko 4 urządzenia dzięki

czemu SCSI jest szczególnie przydatny w przypadku dysków twardych, gdyż

umożliwia jednoczesne połączenie więcej niż 4 takich urządzeń. SCSI oferuje również

szybszy transfer danych między urządzeniami, dochodzący do 80 MB/s (EIDE - 66

MB/s)

Interfejsy dysków twardych

SCSI

Odmiany SCSI

SCSI-1: pierwsza wersja standardu. Pozwalała na

transfer z prędkością 5 MB/s na odległość 6 m,

SCSI-2: kolejna wersja standardu. Składa się z

dwóch wariantów, zwiększających transfer do 10

lub 20 MB/s (odpowiednio Fast SCSI i Wide

SCSI). Maksymalna odległość to około 3 metry,

SCSI-3: znany jako Ultra SCSI, prędkość transferu

20-40 MB/s, teoretycznie maksymalna odległość

zostaje nadal 3 metry,

Ultra2 SCSI: wprowadzono technologię Low

Voltage Differential, pozwalającą na

zwiększenia maksymalnej odległości do ~12 m.

Prędkość transferu 40-80 MB/s,

Ultra3 SCSI (Ultra160 SCSI): maksymalny

transfer 160 MB/s, dodano funkcje wspomagające

wykrywanie i usuwanie przekłamań.

Ultra4 SCSI (Ultra320 SCSI): maksymalny

transfer 320 MB/s.

Ultra 640 SCSI : maksymalny transfer 640 MB/s.

Interfejsy dysków twardych

RAID

RAID (ang. Redundant Array of Independent Disks, Nadmiarowa

macierz niezależnych dysków) - polega na współpracy dwóch

lub więcej dysków twardych w taki sposób, aby zapewnić

dodatkowe możliwości, nieosiągalne przy użyciu jednego dysku.

RAID używa się w następujących celach:

- zwiększenie niezawodności (odporność na awarie)

- przyspieszenie transmisji danych

- powiększenie przestrzeni dostępnej jako jedna całość.

RAID

Standardowe poziomy RAID

Poziom RAID

N = liczba dysków

Dostępna przestrzeń

Odporność na awarię

RAID 0

2

N

0

RAID 1

2+

1

N-1

RAID 2

3+

N - log N

1

RAID 3

3+

N-1

1

RAID 5

3+

N-1

1

RAID 6

4+

N-2

min. 2

RAID 1+0

4+N*2

N /2

min. 1

RAID 0+1

4+N*2

N /2

1

Magistrale I/O

Od czasu wprowadzenia na rynek pierwszego komputera PC opracowano wiele

rodzajów magistral I/O. Wynikało to z oczywistego faktu w celu uzyskania wyższej

wydajności systemu konieczne jest stosowanie szybszych magistral I/O. Potrzeba

zwiększania wydajności jest związana z trzema podstawowymi czynnikami:

• szybszym procesorem,

• rosnącymi wymaganiami aplikacji,

• większymi wymaganiami multimediów.

Każdy z wymienionych wymaga zastosowania jak najszybszej magistrali I/O.

Jednym z głównych powodów niewielkiej szybkości obecnie stosowanych magistral

I/O jest wymóg zachowania kompatybilności, która wiąże przemysł komputerowy z

przeszłością. Jednym z czynników, który zdecydował o sukcesie komputerów,

osobistych była ich standaryzacja. To ona spowodowała, że tysiące niezależnych

firm opracowało swoje karty I/O, z których każda była kompatybilna z oryginalną

specyfikacją magistral zastosowanych w komputerach PC. Jeśli zaprojektowano

nowy typ magistrali systemowej o dużej wydajności, wtedy przeważnie musiała

ona być kompatybilna ze starszymi rozwiązaniami, co wynikało z konieczności

zagwarantowania możliwości instalacji wcześniej wyprodukowanych kart.

Podstawowa różnica pomiędzy poszczególnymi magistralami wynika głównie z

ilości jednocześnie przesyłanych danych, jak również z szybkości działania.

Magistrala ISA

8-bitowa magistrala wykonana zgodnie z architekturą ISA (ang. Industry Standard

Architecture) została zastosowana w 1981 r. w oryginalnym komputerze IBM PC.

W 1984 r. w komputerze IBM PC/AT pojawiła się jej poszerzona, 16-bitowa wersja.

ISA jest podstawową architekturą wykorzystywaną w nowoczesnych komputerach

osobistych i w dalszym ciągu stanowi element składowy większości

produkowanych systemów.

Jeśli za kryterium przyjmiemy ilość danych jednocześnie przesyłanych przez

magistralę ISA, można wtedy wyróżnić jej dwie wersje, 8-bitową, i nowszą, 16bitową. Oryginalna 8-bitowa magistrala ISA zastosowana w komputerach PC i XT

była taktowana zegarem 4,77 MHz, natomiast wersja 16-bitowa użyta w systemie

AT pracowała z częstotliwością 6 MHz, a później 8 MHz. W późniejszym okresie

ustanowiono przemysłowy standard magistrali ISA (8/16-bitowej), w którym

ustalono, że, ze względu na zachowanie kompatybilności wstecz, maksymalna jej

częstotliwość może wynieść 8,33 MHz. W przypadku niektórych systemów istniała

możliwość taktowania magistrali ISA zegarem o wyższej częstotliwości, ale wtedy

nie wszystkie karty działały poprawnie. Przesyłanie danych przez magistralę ISA

wymaga od dwóch do ośmiu cykli. Wynika z tego, że maksymalny teoretyczny

transfer danych przesyłanych przez magistralę ISA wynosi około 8 MB/s.

8-bitowa Magistrala ISA

Architektura 8-bitowej magistrali została zastosowana w oryginalnym komputerze

IBM PC. a następnie przez kilka lat była obecna w projektowanych systemach.

Karta wyposażona w 62 styki położone wzdłuż jej dolnej krawędzi jest instalowana

w gnieździe płyty głównej dysponującym również 62 stykami. Patrząc od strony

zastosowanej elektroniki, gniazdo jest wyposażone w 8 linii danych i 20 linii

adresowych, które pozwalają na obsłużenie pamięci RAM o pojemności 1 MB.

Chociaż budowa magistrali jest dość prosta, to jednak firma IBM czekała aż do

1987 r. na to, aby opublikować pełną specyfikację dotyczącą ustawień linii danych i

adresów. Z tego też powodu, za czasów pierwszych systemów kompatybilnych z

komputerem IBM PC producenci musieli się sporo natrudzić, aby określić, w jaki

sposób wykonać karty instalowane w gniazdach magistrali. Ostatecznie z

problemem się uporano, dzięki czemu systemy kompatybilne z IBM PC zostały

powszechnie zaakceptowane jako standard przemysłowy. W efekcie producenci

dysponowali większą ilością czasu i mieli motywację do projektowania kolejnych

kart poprawnie współpracujących z magistralą.

16-bitowa Magistrala ISA

Firma IBM wraz z wprowadzeniem na rynek w 1984 r. komputera AT wyposażonego

w procesor 286 wywołała spore zamieszanie w świecie komputerów PC. Procesor

286 dysponował 16-bitową magistralą danych, co oznaczało, że teraz komunikacja

pomiędzy procesorem, płytą główną jak również pamięcią mogła się odbywać przez

magistralę o szerokości 16 bitów zamiast ośmiobitowej. W przypadku gdy procesor

286 był też zainstalowany na płycie głównej wyposażonej tylko w 8-bitową

magistralę I/O, to występował ogromny spadek wydajności dowolnej karty lub

innego urządzenia współpracującego z magistralą.

W tamtym okresie firma IBM, zamiast opracowywać nową wersję magistrali I/O,

stworzyła system, który był kompatybilny zarówno z 8-, jak i 16-bitowymi kartami.

Ponadto pozostawiono dotychczas stosowane 8-bitowe gniazda i dodano opcjonalne

16-bitowe złącze rozszerzające. Po raz pierwszy 16-bitowa magistrala ISA pojawiła

się w sierpniu 1984 r. w komputerze PC/AT, dlatego też jest ona określana jako

magistrala AT (ang. AT-bus).

Złącze rozszerzające zastosowane w każdym 16-bitowym gnieździe rozszerzeń

dysponuje 36 dodatkowymi końcówkami (w sumie 96 końcówek) służącymi do

przenoszenia specjalnych sygnałów związanych z szerszą magistralą danych.

Ponadto dokonano modyfikacji dwóch końcówek znajdujących się w 8-bitowej

części złącza, jednak nie były one na tyle poważne, aby zmienić sposób działania

kart 8-bitowych.

Magistrale 32-bitowe

W momencie wprowadzenia do sprzedaży procesorów 32-bitowych nie

istniały jeszcze standardy związane z magistralami 32-bitowymi. Zanim

zaprezentowano specyfikacje magistrali MCA i EISA, niektóre firmy

rozpoczęły projektowanie własnych 32-bitowych magistral, które oparte

były na magistrali ISA. Na szczęście tego typu niestandardowych

magistral było niewiele i pojawiały się w dużych odstępach czasowych.

Dodatkowa część poszerzonej magistrali zazwyczaj była

wykorzystywana przez niestandardowe karty graficzne lub rozszerzające

dostępną pamięć. Ponieważ tego typu rozwiązania ze względu na swoją

niestandardowość nie są udostępniane, nie jest dostępna ich

specyfikacja i schemat rozmieszczenia końcówek.

Magistrala MicroChannel i EISA

Wprowadzenie do sprzedaży procesorów 32-bitowych oznaczało, że

magistrala ISA nie wykorzysta możliwości tkwiących w kolejnej generacji

procesorów. Procesor 386DX był w stanie jednocześnie przesyłać 32 bity

danych, ale magistrala ISA była ograniczona tylko do 16 bitów. Zamiast

ponownie rozszerzać magistralę ISA, firma IBM postanowiła opracować

projekt nowej magistrali. Rezultatem prac była magistrala MCA. Magistrala

MCA (ang. Micro Channel Architecture) jest zupełnie inna niż magistrala

ISA i od strony technicznej przewyższają pod każdym względem.

Firma IBM nie tylko dążyła do zastąpienia starszego standardu ISA, ale

również chciała wymusić na innych producentach zakupienie licencji na

określone elementy nowej technologii. Problemy z udzielaniem licencji i

kontrolą ich przestrzegania doprowadziły ostatecznie do opracowania

konkurencyjnej magistrali EISA, która zmniejszyła szansę odniesienia

sukcesu przez magistralę MCA.

Systemy wyposażone w magistralę MCA charakteryzowały się jeszcze

większą prostotą. Oferowały funkcję Plug and Play, zanim opracowano

oficjalną jej specyfikację. Magistrala MCA nie wymagała zastosowania na

płycie głównej lub na kartach żadnych zworek i przełączników.

Magistrala VESA

Magistrala VESA (ang. Video Electronics Standards Association) Local Bus okazała się najpopularniejszym

typem magistrali lokalnej stosowanym w okresie od sierpnia 1992 r. do 1994 r. Standard VL-Bus został

opracowany przez komitet VESA, organizację non-profit założoną przez firmę NEC.

Początkowo nowa magistrala lokalna była opracowywana z myślą o współpracy z kartami graficznymi. W tym

okresie zwiększenie wydajności podsystemu graficznego dla firmy NEC było sprawą najważniejszą, mającą

pomóc w osiągnięciu lepszych wyników sprzedaży wysokiej jakości monitorów i komputerów PC przez nią

produkowanych. Około roku 1991 wydajność kart graficznych w większości systemów PC okazała się

prawdziwym "wąskim gardłem".

Magistrala VL-Bus pozwala jednocześnie przesłać 32 bity danych, dzięki czemu możliwa jest komunikacja

pomiędzy procesorem a kompatybilnym podsystemem graficznym lub dyskiem twardym odbywająca się przy

wykorzystaniu pełnej 32-bitowej szyny danych procesora 486. Magistrala VL-Bus oferuje maksymalną

przepustowość wynosząca 133 MB/s.

Jej projekt był wyjątkowo prosty. Polegał na przeniesieniu schematu końcówek procesora 486 do gniazda

rozszerzeń magistrali. Wynika z tego, że magistrala VL-Bus tak naprawdę jest magistralą procesora 486. Dzięki

temu, koszt jej wykonania był niewielki. Nie były wymagane żadne dodatkowe chipsety lub interfejsy.

Producent płyt głównych klasy 486 mógł w prosty i tani sposób dodawać do nich gniazda magistrali VL-Bus.

Wraz z wprowadzeniem różnych kart wyposażonych w układy elektroniczne wykorzystujących kondensatory i

w efekcie wprowadzające pojemności do obwodów zaczęły się pojawiać zakłócenia związane z ich

taktowaniem. Ze względu na to, że magistrala VL-Bus pracowała z częstotliwością magistrali procesora,

pojawienie się kolejnego szybszego procesora wiązało się z przyspieszeniem jego magistrali, co sprawiało, że

utrzymanie pełnej kompatybilności obu magistral było zadaniem trudnym do wykonania. Chociaż magistrala

VL-Bus mogła być przystosowana do współpracy z innymi procesorami, takimi jak 386 lub nawet Pentium, to

jednak została zaprojektowana z myślą o układzie 486 i z nim działała najlepiej. Wkrótce po wprowadzeniu na

rynek nowej magistrali PCI, pomimo niskiej ceny magistrala VL-Bus bardzo szybko popadła w niełaskę. Nigdy

nie została zastosowana w systemach opartych na procesorze Pentium, natomiast jej dalszy rozwój był

niewielki lub nawet żaden.

Magistrala PCI

Na początku roku 1992 firma Intel wyszła z inicjatywą utworzenia kolejnej organizacji zrzeszającej

przedstawicieli przemysłu komputerowego. Nowa organizacja miała podobne założenia jak komitet VESA, ale

dotyczyły one magistrali PCI. Powstanie organizacji PCI-SIG (ang. PCI Special Interest Group) wynikało z

potrzeby opracowania nowej magistrali, która będzie pozbawiona wad swoich poprzedników ISA i EISA.

Odkąd w czerwcu 1992 r. pojawiła się specyfikacja standardu PCI w wersji 1.0, opracowano jej kilka

aktualizacji. Umieszczenie kolejnej magistrali PCI pomiędzy procesorem a magistralą I/O wpłynęło na zmianę

standardowej architektury magistral systemowych komputera PC, która wynikała z zastosowania mostków.

Zamiast podłączać nową magistralę, charakteryzującą się, podobnie jak magistrala VL-Bus, specyficznymi

wartościami taktowania, bezpośrednio do magistrali procesora, został opracowany zestaw nowych kontrolerów

rozszerzających możliwości magistrali PCI.

Magistrala PCI pomija zwykłą magistralę I/O, natomiast w celu zwiększenia własnej częstotliwości pracy i

pełnego wykorzystania możliwości magistrali danych procesora komunikuje się z magistralą systemową.

Systemy wyposażone w magistralę PCI pojawiły się w połowie 1993 r. i od tego czasu stanowią jeden z filarów

komputera osobistego.

Zazwyczaj magistrala PCI taktowana zegarem 33 MHz przesyła jednocześnie 32 bity danych. Oferuje

przepustowość wynoszącą 133 MB/s.

Aktualnie 64-bitowa wersja magistrali PCI taktowana zegarem 66 lub 133 MHz jest stosowana tylko w

serwerach lub bardziej zaawansowanych stacjach roboczych. Magistrala PCI charakteryzująca się zwiększoną

wydajnością, może pracować z szybkością oferowaną przez magistralę procesora, ale nie oznacza to, że ją

zastąpi. Obecność obu magistral pozwala przykładowo na to, aby procesor w czasie, gdy magistrala PCI jest

zajęta przesyłaniem danych pomiędzy innymi komponentami systemu, mógł przetwarzać dane znajdujące się

w zewnętrznej pamięci podręcznej. Jest to jedna z podstawowych zalet wynikających z zastosowania

magistrali PCI.

W specyfikacji standardu PCI określono trzy różne konfiguracje gniazd, z których każde zostało przewidziane

do zastosowania w systemie dysponującym określonymi parametrami zasilania. W każdym wariancie

uwzględniono zarówno wersję 32-bitową, jak i dłuższą 64-bitową. Pierwszy wariant konfiguracji dotyczy

gniazda zasilanego napięciem 5 V przeznaczonym dla komputerów stacjonarnych, drugi gniazda zasilanego

napięciem 3,3 V i stosowanym w komputerach przenośnych, natomiast trzeci ma charakter uniwersalny

Magistrala PCI

W specyfikacji standardu PCI określono trzy różne konfiguracje gniazd, z których każde zostało

przewidziane do zastosowania w systemie dysponującym określonymi parametrami zasilania. W każdym

wariancie uwzględniono zarówno wersję 32-bitową, jak i dłuższą 64-bitową. Pierwszy wariant konfiguracji

dotyczy gniazda zasilanego napięciem 5 V przeznaczonym dla komputerów stacjonarnych, drugi gniazda

zasilanego napięciem 3,3 V i stosowanym w komputerach przenośnych, natomiast trzeci ma charakter

uniwersalny przystosowany do współpracy z systemami obu typów. Gniazda PCI w wersji 64-bitowej

zasilanej napięciem 5 V oraz w wersji uniwersalnej spotykane są głównie na płytach głównych serwerów.

Kolejna znacząca korzyść wynikająca z zastosowania magistrali PCI jest związana z tym, że posłużyła za

wzorzec przy opracowywaniu specyfikacji Intel PnP. W związku z tym, karty PCI są pozbawione zworek i

przełączników, a ich konfiguracja jest wykonywana za pomocą oprogramowania. Prawdziwe systemy PnP

potrafią dokonać automatycznej konfiguracji zainstalowanych kart. W przypadku komputerów

pozbawionych funkcji PnP i wyposażonych w karty ISA, w celu ustawienia ich parametrów konieczne jest

zastosowanie programu, który zazwyczaj stanowi część narzędzia konfiguracyjnego CMOS. Pod koniec roku

1995, większość systemów kompatybilnych z komputerem IBM PC była wyposażona w BIOS PnP

pozwalający na automatyczną konfiguracją urządzeń PnP.

Magistrala AGP

Firma Intel opracowała magistralę AGP jako rozwiązanie przeznaczone do współpracy z bardzo szybkimi

kartami graficznymi. Magistrala AGP wzorowana jest na magistrali PCI, ale zawiera kilka dodatków i

ulepszeń. Ponadto, pod względem budowy, zastosowanej elektroniki i logicznej architektury jest zupełnie

niezależna od magistrali PCI. Gniazdo AGP jest podobne do gniazda PCI, ale jest również wyposażone w

dodatkowe końcówki. Poza tym gniazdo AGP inaczej jest usytuowane na płycie głównej. W przeciwieństwie

do magistrali PCI, która zawiera kilka gniazd, magistrala AGP dysponuje tylko jednym bardzo wydajnym

gniazdem umożliwiającym instalację wyłącznie karty graficznej. Ograniczenie to wynika z faktu, że w

systemie może być zainstalowana tylko jedna taka karta. W lipcu 1996 r. firma Intel opracowała pierwszą

wersję specyfikacji AGP 1.0, w której określiła magistralę pracującą z częstotliwością 66 MHz i dysponującą

trybem x1 i x2. Magistrala AGP była zasilana napięciem 3,3 V. W maju 1998 r. pojawiła się wersja 2.0, w

której dodano możliwość pracy magistrali w trybie x4 zasilanej napięciem 1,5 V.

W sierpniu 1998 r. została opracowana nowsza wersja specyfikacji AGP Pro 1.0, a następnie dokonano jej

modyfikacji i w kwietniu 1999 r. pojawiła się wersja 1.1a. Nowa wersja specyfikacji definiuje trochę dłuższe

gniazdo poszerzone o dodatkowe końcówki zasilające umieszczone po obu jej końcach. Ich zadanie

polegało na obsłudze większych i szybszych kart AGP zużywających od ponad 25 do maksymalnie 110 W

energii. Karty AGP Pro najprawdopodobniej będą wykorzystywane w zaawansowanych stacjach graficznych

i raczej nie będą stosowane w typowych komputerach PC. Niezależnie od tego, gniazda AGP Pro są

kompatybilne wstecz, co oznacza, że umożliwiają instalację standardowych kart AGP. W związku z tym

kilku producentów płyt głównych wyposaża swoje najnowsze modele zamiast gniazd AGP x4 w gniazda

AGP Pro. Ze względu na to, że gniazda AGP Pro są dłuższe, instalowane w nich karty AGP x1/x2 mogą być

nieprawidłowo zamonkowane, co w efekcie może doprowadzić do ich uszkodzenia. Z tego też powodu

niektórzy producenci płyt głównych umieszczają z tylnej strony gniazda AGP Pro osłonę, która powinna być

zdejmowana tylko wtedy, gdy zaistnieje potrzeba instalacji karty AGP Pro.

Magistrala AGP

Najnowsza wersja 3.0 specyfikacji standardu AGP przeznaczonego dla komputerów PC określa tryb AGP x8.

AGP x8 pozwala na osiągnięcie przepustowości 2133 MB/s, która dwukrotnie przewyższa możliwości trybu

AGP x4. Specyfikacja AGP x8 po raz pierwszy została oficjalnie zaprezentowana w listopadzie 2000 r.

AGP jest bardzo szybką magistralą pracującą z częstotliwością 66 MHz (dokładnie 66,66 MHz), czyli

dwukrotnie wyższą niż w przypadku magistrali PCI. Magistrala AGP oferująca tryb podstawowy x1 w ciągu

jednego cyklu wykonuje pojedynczą operację przesłania danych. Szerokość magistrali AGP wynosząca 32bity (4 bajty) i częstotliwość 66 MHz (66 miliony razy na sekundę) pozwala na przesyłanie danych przy

przepustowości około 266 MB/s! W oryginalnej wersji specyfikacji standardu AGP określono również tryb x2,

który charakteryzuje się tym, że w każdym cyklu są wykonywane dwie operacje przesłania danych, co

odpowiada przepustowości 533 MB/s. Początkowo większość pierwszych kart AGP pracowała tylko w trybie

x1, ale dość szybko wiele firm rozpoczęło produkcję kart kompatybilnych z trybem x2. W nowszej

specyfikacji AGP 2.0 dodano możliwość pracy w trybie x4, który pozwala na przesyłanie danych cztery razy w

ciągu cyklu, co odpowiada przepustowości 1066 MB/s. Większość obecnie dostępnych kart AGP obsługuje

tryb x4, który jest traktowany jako absolutne minimum. Ponieważ magistrala AGP działa niezależnie od

magistrali PCI, dzięki zastosowaniu karty graficznej AGP magistrala PCI jest odciążona i efektywniej

obsługuje inne urządzenia wejścia-wyjścia, takie jak kontrolery IDE/ATA lub SCSI, kontrolery USB, karty

dźwiękowe itp.

Poza wyższą wydajnością kart graficznych, jednym z podstawowych powodów, dla których firma Intel

opracowała standard AGP, było utworzenie bezpośredniego szybkiego połączenia karty graficznej z pamięcią

RAM, które umożliwiłoby uzyskanie wystarczająco szybkiego i wydajnego podsystemu graficznego

charakteryzującego się niższymi kosztami integracji. Magistrala AGP pozwala karcie graficznej na uzyskanie

bezpośredniego dostępu do pamięci operacyjnej. Dzięki temu możliwe jest umieszczenie tańszych układów

graficznych bezpośrednio na płycie głównej bez konieczności wyposażania ich w dodatkową pamięć RAM lub

pozwolenie karcie AGP na korzystanie z podstawowej pamięci operacyjnej. Bardzo wydajne karty graficzne

prawdopodobnie w dalszym ciągu będą wyposażane w coraz większą ilość bezpośrednio zintegrowanej

pamięci, co ma szczególne znaczenie w przypadku wykorzystywania aplikacji przetwarzających grafikę

trójwymiarową wymagających dużej wydajności.

Magistrala PCI E

W 2001 r. grupa firm działających pod nazwą Arapahoe Work Group (wśród których główną rolę odgrywała

firma Intel) opracowała wstępną wersję specyfikacji bardzo szybkiej magistrali o nazwie kodowej 3GIO

(ang. third-generation I/O). W sierpniu 2001 r. organizacja PCI-SIG (ang. PCI Special Interest

Group) wyraziła zgodę na przejęcie, nadzorowanie i promowanie specyfikacji dotyczącej architektury

3GIO, która miała zastąpić standard PCI. W kwietniu 2002 r. ukończono wstępną wersję 1.0 specyfikacji

3GIO i zmieniono jej nazwę na PCI Express.

. Po przejęciu przez organizację PCI-SIG specyfikacji nowej magistrali PCI Express zostanie ona

przygotowana do tego, aby stać się dominującą na rynku architekturą, która będzie w stanie spełnić

wymagania związane z coraz większą przepustowością i pozostanie obecna w komputerach PC przez

następne 10-15 lat.

Do podstawowych właściwości magistrali PCI Express należy zaliczyć:

kompatybilność z już istniejącymi wersjami standardu PCI oraz sterownikami urządzeń,

możliwość współpracy z różnymi fizycznymi nośnikami danych (miedzianymi, optycznymi) pozwalająca na

implementacją przyszłych układów taktujących,

jak największa przepustowość (w przeliczeniu na jedną końcówkę) pozwalająca na zastosowanie

mniejszych formatów, obniżenie kosztów, uproszczenie budowy kart i ścieżek sygnałowych oraz

wyeliminowanie problemów związanych z obniżoną integralnością sygnału,

wbudowany układ taktujący, który pozwala na prostszą w porównaniu z taktowaniem synchronicznym

modyfikację częstotliwości (szybkości),

uproszczone zwiększanie przepustowości (pasma) wraz ze wzrostem częstotliwości i szerokości szyny,

zmniejszone opóźnienie mające szczególne znaczenie w przypadku aplikacji przesyłających obraz wideo w

trybie strumieniowym wymagających izochronicznego przesyłania danych,

funkcje hot-plug i

hot-swap,

funkcje zarządzania energią.

Magistrala PCI E

Magistrala PCI Express jest kolejnym przykładem przejścia z

interfejsów równoległych na szeregowe. W przypadku

starszych architektur magistral stosowanych w komputerach

PC opierano się na interfejsie równoległym, który

charakteryzuje się tym, że wiele bitów jest jednocześnie

przesyłanych przez kilka równoległych linii. Im więcej

jednocześnie przesłanych bitów, tym większa przepustowość

magistrali. Taktowanie wszystkich zrównoleglonych sygnałów

musi być identyczne, co w przypadku coraz szybszych i

dłuższych połączeń staje się coraz trudniejsze do wykonania.

Magistrala oparta na interfejsie szeregowym jest o wiele

prostsza. Jej działanie polega na jednoczesnym przesłaniu za

pomocą jednej linii 1 bitu. Operacja jest wykonywana ze

znacznie większą szybkością, która jest niemożliwa do

osiągnięcia w przypadku interfejsu równoległego. Dzięki

szeregowemu przesyłaniu bitów, taktowanie kolejnych

wartości lub długość magistrali nie mają już takiego znaczenia.

Poprzez połączenie wielu linii szeregowych możliwe jest

uzyskanie przepustowości, która w znaczący sposób przerasta

możliwości typowych magistral równoległych.

PCI Express jest bardzo szybką magistralą szeregową, która dodatkowo jest kompatybilna wstecz ze sterownikami

aktualnie stosowanej magistrali równoległej PCI. W przypadku magistrali PCI Express dane są przesyłane w trybie

pełnego dupleksu (dane przesyłane jednocześnie jednokierunkowymi liniami) dwuparowymi kablami (zasilanymi

różnymi napięciami) określanymi mianem torów. Tor oferuje początkową przepustowość 250 MB/s w każdym

kierunku. Istnieje możliwość łączenia ze sobą kilku torów w grupy liczące 2, 4, 8, 16 lub 32. Przykładowo,

konfiguracja o dużej wydajności licząca 8 torów umożliwia jednoczesne przesłanie w obu kierunkach danych

odpowiadających maksymalnej przepustowości 2000 MB/s (w jedną stronę

Magistrala PCI E

Aby uzyskać taką przepustowość, wystarczy zaledwie 40

końcówek (32 dla danych i 8 sterujących). Magistrala PCI

Express wykorzystuje opracowany przez firmę IBM schemat

kodowania 8-bitów na 10-bitów. Umożliwia on przesyłanie

sygnałów, które same określają taktowanie, dzięki czemu w

przyszłości znacznie łatwiejsze będzie zwiększanie

częstotliwości magistrali PCI Express. Początkowa wartość

częstotliwości została ustalona na 2,5 GHz, ale w specyfikacji

przewidziano jej zwiększenie w przyszłości do maksymalnie 10

GHz, co jest bliskie ograniczeniom technologii opartej na

połączeniach wykonanych z miedzi. Wskutek połączenia

możliwości zwiększania częstotliwości z użyciem maksymalnie

32 torów, magistrala PCI Express będzie w stanie osiągać w

przyszłości przepustowość rzędu 32 GB/s.

Magistrala PCI Express jest projektowana jako uzupełnienie i

ostatecznie następca aktualnie wykorzystywanych magistral

stosowanych w komputerach PC.

Jej użycie nie ograniczy się tylko do roli dodatku do magistrali PCI (i ostatecznie następcy), ale również zastąpi

obecnie wykorzystywane interfejsy Intel Hub lub AMD Hypertransport łączące elementy składowe chipsetu

płyty głównej. Ponadto magistrala PCI Express zastąpi interfejsy graficzne takie jak AGP i będzie pełnić funkcję

magistrali współpracującej z innymi interfejsami takimi jak Serial ATA, USB 2.0, 1394b (FireWire lub iLink) oraz

Gigabit Ethernet.