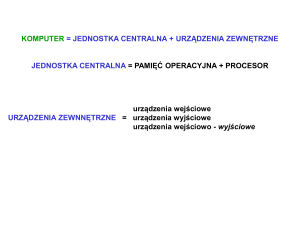

1) Wstęp

Chipset AMD-760™ to układ logiki systemowej o wysokiej skali integracji, który

zapewnia wzrost wydajności procesora AMD Athlon oraz innych procesorów AMD

kompatybilnych z magistralą systemową dla AMD Athlon. Chipset AMD-760

składa się ze sterownika systemowego AMD-761™ umieszczonego w obudowie

PBGA (plastic ball-grid array) z 569 wyprowadzeniami oraz sterownika magistrali

urządzeń peryferyjnych AMD-766™ umieszczonego w obudowie PBGA z 272

wyprowadzeniami.

Schemat blokowy chipsetu zawiera rysunek 1:

Rys.1 Schemat blokowy chipsetu AMD760

Sterownik systemowy AMD761 obsługuje:

AMD Athlon System Bus - magistrala systemowa Athlon, zezwalająca na

odseparowaną transmisję danych(odczyt/zapisz). Magistrala ta jest taktowana z

prędkościami 100/200MHz lub 133/266Mhz

sterownik magistrali (PCI 2.2) łączącej go z mostkiem dla urządzeń

peryferyjnych – z arbitrażem

sterownik AGP – obsługujący tryby pracy 1x,2x,4x (zgodność z wersją 2.0)

sterownik pamięci systemowej DDR-SDRAM

1.1 ASB – Athlon System Bus

Magistrala systemowa Athlon jest wewnętrzną magistralą służącą do przesyłu informacji

między procesorem a pamięcią, za pośrednictwem kontrolera AMD-761. Magistrala

wykonana jest w technologii punkt-do-punktu (point-to-point) – co gwarantuje wysoką

prędkość transmisji danych. Główną jednak zaletą układu jest nie tyle zastosowanie wyżej

wymienionej topologii ile zastosowanie tzw. „split transaction” – czyli podziału operacji

zapisu/odczytu na instrukcje oraz dane rozsyłane odrębnymi kanałami dystrybucyjnymi

(magistralami). I tak w przypadku odczytu, cała transakcja rozpoczyna się od wysłania

żądania przesłania danych przez procesor. Żądanie takie jest kierowane przez CPU na

magistralę SADDOUT. W momencie, gdy kontroler pamięci jest gotowy do realizacji żądania

informuje procesor za pomocą magistrali STDDIN o wysyłaniu danych magistralą SDATA.

Wraz z danymi wysyłany jest identyfikator pierwotnego żądania, tak aby procesor mógł

upewnić się, iż otrzymuje dane o które prosił.

Analogicznie rozwiązywana jest transakcja zapisu: wpierw wysyłany jest komunikat o

potrzebie zapisu za pomocą magistrali SADDOUT, chipset akceptuje żądanie za pomocą

magistrali SADDIN a następnie magistralą SDATA dokonywany jest faktyczny przesył

danych.

Magistrala ASB odznacza się następującymi cechami:

wysoko wydajna topologia typu punkt-do-punktu (point-to-point)

synchronizacja źródeł danych w celu zwiększenie efektywności przepływu

informacji

magistrala pracuje z prędkością 200 lub 266Mhz

zastosowanie mechanizmu „split transaction”

maksymalny transfer na magistrali wynosi 1.6GB/s (100/200Mhz) 2.1GB

(133/266MHz)

64-bitowa transmisja danych

1.2 Sterownik pamięci systemowej.

Głównym zadaniem sterownika jest rozstrzyganie oraz optymalizacja żądań przychodzących

do pamięci, obsługa ECC oraz GART(Graphics Address Remaping Table) oraz zarządzanie

do 4 modułów pamięci SDRAM/DDR. Układ AMD-761 jest dostosowany do obsługi dwóch

typów pamięci:

rejestrowaną pamięć DDR

niebuforowana pamięć DDR

Rejestrowana pamięć DDR różni się od niebuforowanej pamięci DDR tym, że

płyty główne obsługujące pamięć niebuforowaną są przeznaczone na rynek

konsumencki i mogą być wyposażone maksymalnie w 2GB pamięci, podczas gdy

płyty obsługujące rejestrowane moduły DIMM są przeznaczone na rynek

biznesowy i mogą zapewnić do 4GB pamięci DDR. Chipset AMD-760 obsługuje

zarówno rejestrowane, jak i niebuforowane układy DDR DIMM, przy czym

możliwe jest obłożenie do 2 modułów pamięci niebuforowanej oraz do 4 modułów

pamięci rejestrowanej, przy czym nie jest możliwe wymieszanie obu typów

pamięci na jednej płycie głównej.

Wszystkie parametry czasowe pamięci DDR są programowalne i zapamiętywane

przez wewnętrzne rejestry układu AMD-761. Sam proces odświeżania pamięci

również jest ustawiany programowo i pozwala na wybranie jednego z czterech

możliwych prędkości odświeżania. Para zegarów taktujących pamięci może być

selektywnie wyłączona dla niewykorzystywanych slotów pamięci DIMM przez

odpowiednie bity rejestrów kontrolnych sterownika. Sterownik pamięci zezwala

na dostęp do 4 stron pamięci na raz przy jednym aktywnym sygnale CS (chip

select). Wszystkie strony w pamięci układu są automatycznie zamykane w

przypadku wybrania innego układu, prze sygnał CS. Operacje na stronach

pamięci mogą być później optymalizowane programowo przez ustawienie liczby

bezczynnych cykli po których następuje automatyczne odświeżenie banku

pamięci.

W przypadku wykorzystywania niebuforowanej pamięci układ sterownika AMD761 potrzebuje tylko 4 sygnałów CS obsługujących dwa sloty DIMM – stąd w

przypadku wykorzystywania tego typu pamięci obsługiwane są jedynie dwa sloty

pamięci DIMM – dla każdego z nich sterownik pamięci wykorzystuje 3 różnorodne

układy czasowe do jego taktowania, co prezentuje rysunek:

Akceptowalne przez sterownik rozmiary pamięci zawiera poniższa tabela:

W przypadku wykorzystywania pamięci rejestrowanej wykorzystywanych jest do ośmiu

pinów CS pozwalających na wybór jednego z dwóch modułów DIMM, co prezentuje

rysunek:

Jak widać na powyższym rysunku, każdy z modułów DIMM składa się z 2 banków pamięci, a

sam kontroler używa pary zegarów do każdego z modułów DIMM. Zastosowanie tego typu

pamięci pozwala na zaadresowanie maksymalnej przestrzeni adresowej obsługiwanej przez

kontroler tj. 4GB, co przedstawia tabela:

Podsumowując kontroler pamięci zastosowany w AMD-761, realizuje następujące zadania:

obsługa i transfer informacji do/z pamięci, z różnych źródeł, takich jak:

o procesor

o magistrala PCI

o magistrala AGP

obsługa ECC ( error correcting code ) pamięci

obsługa DRAM:

o do 2 niebuforowanych modułów pamięci DIMM

o do 4 rejstrowanych modułów pamięci DIMM

o obsługa 64-bitowych pamięci + 8b ECC

możliwość zaadresowania do 4GB pamięci

do 4 otwartych storn pamięci przy jednym aktywnym chipie(CS)

konfigurowalne przez BIOS parametry czasowe pamięci

możliwość jednoczesnego zapisu oraz odczytu pamięci

1.3 Sterownik magistrali PCI

Układ AMD-761 obsługuje 32-bitowe magistrale PCI zgodne ze standardem PCI 2.2.

Podstawowym zadaniem sterownika jest konwertowanie 64-bitowych danych wysyłanych ze

strony procesora na akceptowane przez magistralę PCI 32-biotwe paczki z zachowaniem

ważności komend. Do tego celu używa się dwóch niezależnych buforów, jednego dla każdej

ze stron komunikacji(PCI-DRAM i DRAM-PCI), przy czym możliwy jest jednoczesny dostęp

do obu buforów zarówno przez procesor jak i magistralę PCI.. Poza obsługą przesyłu danych

między procesorem a magistralą PCI układ sterownika zajmuje się również logicznym

arbitrażem w dostępie do zasobów sprzętowych przez poszczególne urządzenia przypięte do

magistral PCI oraz Souhtbidge’a i procesora. Stosowany jest następujący algorytm arbitrażu:

1. Southbridge

2. CPU

3. Southbridge

4. Magistrala PCI(jedno z 7 urządzeń)

5. powrót do 1

Ponadto układ sterownika magistrali PCI stosuje algorytm korekcji błędów ECC do

wszystkich danych wysyłanych z pamięci – w przypadku stwierdzenia błędu, informacja o

błędzie jest przekazywana do Southbridge’a..

Żądanie odczytu z magistrali PCI są realizowane w specjalny sposób. W przypadku

otrzymania pierwszej porcji danych kontroler może od razu zaciągnąć następną porcję

danych, gdyż z reguły urządzenie przyłączone do magistrali PCI potrafią zabuforować

większą ilość informacji niż można jednorazowo wypchnąć na samą magistralę – co pozwala

efektywnie wykorzystywać szerszą magistralę pamięci w komunikacji.

Podsumowując sterownik magistrali PCI, zawiera:

zgodność ze specyfikacją PCI Local Bus v.2.2

obsługa do 7 urządzeń PCI+obsługa żądań sterownika magistrali urządzeń

peryferyjnych AMD-766

32-bitowy interfejs, kompatybilny z urządzeniami PCI 3,3V i 5V

synchroniczna obsługa magistrali PCI z częstotliwością 33MHz

maksymalny transfer danych z PCI do DRAM z prędkością 132MB/s

optymalizacja komend PCI takich jak MRM(Memory Read Multiple), MWI(MemoryWrite-and-Invalidate)

1.4 Sterownik magistrali AGP

AGP (Accelerated Grpahics Port) jest wewnętrzną magistralą łączącą kartę grafiki z

kontrolerem pamięci AMD-761, która zezwala na przechowywanie danych odnoszących się

do grafiki bezpośrednio w pamięci głównej. Jak wszystkie wewnętrzne magistrale, również ta

została wykonana w technologii point-to-point i jej głównym zadaniem jest odciążenie

magistrali PCI do wymiany danych graficznych z pamięcią. Sterownik magistrali AGP

zastosowany w układzie AMD-761 jest w pełni kompatybilny z specyfikacją Accelerated

Graphics Port Interface w wersji 2.0

Zastosowanie magistrali AGP do przesyłu danych graficznych i odciążenie od tego zadania

magistrali PCI niesie za sobą następujące korzyści:

rozdzielenie żądania odczytu/zapisu od transmisji danych (split transactions)

kolejkowanie żądań – żądania mogą zostać zabuforowane w wewnętrznej kolejce

żądań sterownika – kolejka ta ma wyższy priorytet niż żądań pochodzące z magistral

PCI

priorytetowanie – żądania zapisu i odczytu mogą mieć swoje własne priorytety

(wysoki/niski)

DLR(Defined-Length Request) – strumień danych, jego rozmiar, jest zdefiniowany w

komendzie i nie jest on sztywno ograniczony jak w przypadku PCI(przez tzw. Ramkę

PCI)

minimalny rozmiar przesyłanych danych wynosi 8B

zastosowanie oddzielnej magistrali SBA(SideBand Address) – pozwala na

jednoczesną transmisję danych oraz żądań

GART - Graphics Address Remapping Table

Magistrala AGP oferuje dwie kolejki żądań: jedną dla żądań odczytu i jedną dla żądań zapisu.

Ponieważ żądania te mogą posiadać różne priorytety, które zaburzają naturalną kolejność

FIFO, kolejki te nie mogą być zbyt duże. Żądania z obu kolejek mogą jednak następować w

tym samym czasie. Reguły priorytetowania na magistrali AGP zakładają, że żądania zapisu są

ważniejsze od żądań odczytu. Odczyt jest realizowany jedynie w przypadku gdy wszystkie

potrzebne dane zostaną zapisane do pamięci, ale dotyczy to jedynie wywołań niskiego

priorytetu. Kiedy w kolejce znajduje się żądanie odczytu niskiego priorytetu, ustawiana jest

odpowiednia flaga i sprawdzane jest czy nie ma jakiś żądań w kolejce zapisu. Jeśli takowe

istnieją żądanie odczytu jest blokowane do czasu wykonania zapisu.

Ogólnie kolejkowanie zapisu/odczytu stosuje się do następujących reguł:

wszystkie żądania danego poziomu(niski/wysoki priorytet) i rodzaju (zapis/odczyt) są

realizowane w kolejności ich przybycia(FIFO)

żądania odczytu niskiego priorytetu, zawsze ustępują żądaniom zapisu niskiego

priorytetu

nie istnieją żadne reguły priorytetowania w przypdaku komunikacji między

magistralami PCI a AGP

żądania o podwyższonym priorytecie są wykonywane przed żądaniami niskiego

priorytetu(zaburzenie FIFO)

nie ma żadnych zależności między żądaniami zapisu i odczytu wysokiego priorytetu

- co oznacza, iż tego typu żądania są wykonwywane w kolejności ich wystąpienia

1.5 Układy czasowe

Układ AMD-761™ wyposażony jest w następujący układy zegarowe:

- SYSCLK – służy do taktowania magistrali Athlon System Bus oraz

pamięci – standardowo działa z prędkościami 100 lub 133MHz

- AGPCLK – do taktowania magistrali AGP – 66MHz

- PCICLK – do taktowania magistrali PCI – 33MHz

1.6 System zarządzania energią.

System zarządzania energią wbudowany w układ AMD-761 jest w pełni zgodny z

specyfikacją ACPI(Advanced Configuration Power Interface). Poniższy schemat wyjaśnia

sposób komunikacji miedzy procesorem a sterownikiem zarządzającym energią:

Procesor i kontroler komunikują się wzajemnie za pomocą magistrali Athlon Processor

System Bus (APSB) w wykorzystaniem specjalnych sygnałów za pomocą predefiniowanego

protokołu służącego do włączania/wyłączanie zasilania. Zazwyczaj to procesor wysyła

żądanie obniżenia poboru mocy do kontrolera, a ten w zależności od sytuacji może od razu

wyłączyć procesor, bądź dokonać tego z odpowiednim opóźnieniem. Kontroler realizuje

polecenia protokołu jako pewien stan opisany w ACPI. Najczęściej wykorzystywane są dwa

polecenia:

HALT – żądanie wysyłane przez procesor, jako odpowiedź na instrukcję HALT. W

takiej w sytuacji kontroler generuje sygnał HALT i przesyła go do magistrali PCI i w

zależności od potrzeb, rozpoczyna procedurę rozłączania magistrali APSB od

procesora.

STOP GRANT – żądanie generowane przez procesor w wyniku odpowiedzi na

sygnał STPCLK#. Podobnie jak w przypadku sygnału HALT kontroler „przepuszcza

ten sygnał na magistralę PCI i rozpoczyna sekwencję określaną mianem STOP

GRANT:

o wyłącza arbitraż na magistralach PCI/AGP, oraz opróżnia bufory (czeka na

ich opróżnienie) związane z kolejkami żądań

o rozpoczyna odłączanie procesora od ASPB wraz z automatycznym

odświeżeniem pamięci

o wysyła informację do kontrolera urządzeń zewnętrznych AMD-766, który z

kolei ustanawia odpowiedni poziom zasilania

Układ AMD-761 rozpoznaje i obsługuje następujące poziomy/stany zasilania:

ACPI C0 – full on

ACPI C1 – halt

ACPI C2 – stop grant

ACPI S1 – power-on suspend

ACPI S3 – suspend to RAM

C0 – Full-on

W tym stanie kontroler jest w tzw. pełnym trybie pracy: uruchomione są wszystkie układy

czasowe, podłączone są wszystkie zasilania do układów, w sposób normalny odświeżana jest

pamięć DRAM

C1 – Halt

W tym trybie pracy(o sposobie jego wywołania pisałem wcześniej) następuje odcięcie

procesora od magistrali ASPB, przy czym wszystkie urządzenia przyłączone do magistrali

PCI i AGP pracują normalnie. W przypadku wykrycia potrzeby sięgnięcia przez te

urządzenia do pamięci podręcznej procesora, sterownik AMD-761 dokonuje próby

aktywowania procesora wysyłając na magistrale ASPB odpowiedni sygnał. Sygnały te są

ponawiana do skutku aż do czasu otrzymania potwierdzenia ze strony procesora o gotowości

do pracy. W momencie zakończenie transmisji żądanych danych przez procesor układ

AMD-761 automatycznie przywraca procesor do stanu uśpienia, chyba że procesor zażąda

przejścia w stan C0 informując o tym kontroler odpowiednią sekwencją,

C2 – Stop Grant

W tym trybie pracy, po otrzymaniu sygnału Stop Grant kontroler automatycznie przestawia

procesor w tryb uśpienia oraz w czasie pzrekierowywania sygnału na magistralę PCI już

dokonuje przełączenia pamięci na tryb autoodświeżania. W momencie wykrycie potrzeby

sięgnięcia do procesora lub pamięci układa automatycznie przywraca łączność z procesorem

oraz przejmuje kontrolę nad procesem odświeżania pamięci. Jeśli po wykonaniu zadani

kontroler AMD-761 nie potrzyma odpowiedniej sekwencji przełączające tryb na C0

automatycznie wraca do stanu C2.

S1 – Power on-Suspend

Ten tryb pracy odznacza się niskim poborem mocy spowodowany odłączeniem procesora,

przejściem na autoodświerzanie pamięci oraz wyłączeniem większości układów zegarowych

w sterowniku W tym stanie pracuję jedynie układy czasowe pracujące przy pamięciach

rejestrowanych, ale np. układy czasowe pamięci niebuforowanej są wyłączone. Procedura

przejścia do tego stanu jest następująca:

system operacyjny wysyła do wszystkich urządzeń żądanie mające na celu

zablokowanie wywołań DMA od urządzeń peryferyjnych – aktualnie zgłoszone

żądania zostaną jeszcze obsłużone, ale założona jest blokada na nowe żądania

mostek południowy wysyła sygnał STPCLK# do procesora

w odpowiedzi na sygnał STPCLK# procesor opróżnia swoje bufory i zgłasza żądanie

przejścia do stanu C2(wysyła sygnał Stop Grant)

AMD-761 – opróżnia wszystkie swoje wewnętrzne kolejki i rozpoczyna procedurę

odłączania procesora

po wyczyszczeniu kolejek sterownik włącza pamięć w tryb autoodświerzania

wysyłany jest sygnał StopGran na magistrale PCI

Southbridge wykrywa sygnał Stop Grant i w momencie otrzymania potwierdzenia z

magistrali PCI odsyła informację do AMD-761

układ AMD-761 wyłącza większość swoich układów zegarowych

S3 – Suspend to RAM

Stan S3 jest bardzo podobny do stanu S1, przy czym w tym stanie dodatkowo jest odłączane

zasilanie do wszystkich układów znajdujących się na płycie głównej za wyjątkiem AMD-761,

układów pamięci oraz niewielkiej części sterownika urządzeń peryferyjnych AMD-766. Stan

S# jest stanem najniższego zapotrzebowania na energię i pozwala na szybkie wznowienie

pracy systemu, gdyż aktualny wątek(kontekst) systemu jest przechowywany w pamięci a nie

jest zrzucany na dysk. W przypadku przejścia do stanu S3 zachowywana jest podobna

procedura co przy S1 z tym że do samej sekwencji dodano jeden punkt:

Wyłączenie zasilania dla układów znajdujących się na płcie głównej.