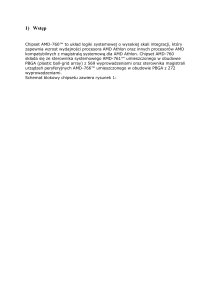

Magistrale równoległe

(systemowe)

Magistrale

2/24

pamięci

zewn.

ukł.obsługi

PAO

dekodery

adresów

kontrolery

przerwań

timery

RTC

magistrala

systemowa

procesor

pamięć

programu

(ROM)

pamięć

danych

(RAM)

urz.

operatorskie

urz.

komunikacyjne

urz.

obiektowe

magistrale

komunikacyjne

inne systemy

panel operatorski

urządzenia

kontr-pomiar.

Magistrale systemowe - MUBUS

3/24

Magistrala MUBUS

D0..D15 - 16 linii danych;

A0..A15 - 16 linii adresowych;

ADMEMLOW, ADPERLOW - stroby odwołania do pamięci i I/O

REFRESHLOW - strob adresu odświeŜania

NOTREADYLOW - brak gotowości

WRITELOW - strob wpisu

NODALOW - waŜność danych na D0..D15

RESETLOW - zerowanie systemu

INTREQLOW, INTACKLOW - zgłoszenie przerwania i jego potwierdzenie

INTIN, INTOUT - sygnały łańcucha urządzeń przerywających

NMILOW - przerwanie niemaskowalne

HOLDREQLOW, HOLDACKLOW - Ŝądanie DMA i jego potwierdzenie

HOLDIN, HOLDOUT - łańcuch urządzeń DMA

PROCREQLOW - Ŝądanie dostępu do magistrali w systemie wieloprocesorowym

SYSTEMCLOCK, USERCLOCK - sygnały zegarowe;

-12V,-5V,0V,5V,12V - wewnętrzne linie zasilające;

-15V,0V,15V oraz 0V,5V - zewnętrzne linie zasilające, odizolowane

galwanicznie od wewnętrznych linii zasilających.

Magistrale systemowe - MUBUS

cykl odczytu pamięci

4/24

cykl odczytu urz. zewnętrznego

A15..A0

A15..A0

ADMEMLOW

ADPERLOW

NOTREADYLOW

NOTREADYLOW

WRITELOW

WRITELOW

D15..D0

D15..D0

cykl zapisu pamięci

cykl zapisu urz. zewnętrznego

A15..A0

A15..A0

ADMEMLOW

ADPERLOW

NOTREADYLOW

NOTREADYLOW

WRITELOW

WRITELOW

D15..D0

D15..D0

Magistrale systemowe - MULTIBUS

Magistrala MULTIBUS Intela

DAT0..DAT15 - linie danych;

ADR0..ADR15 - linie adresowe;

MRDC, MWTC - stroby odczytu i zapisu pamięci

IORC, IOWC - stroby odczytu i zapisu peryferii

XACK, AACK - sygnały potwierdzenia zapisu/odczytu przez pamięć lub I/O

INH1 - linia zakazu dla pamięci RAM

INH2 - linia zakazu dla pamięci ROM

INIT - zerowanie systemu

INT0..INT7 - wejścia przerwań

BREQ - sygnał Ŝądania dostępu do magistrali

BUSY - sygnał zajętości magistrali

BPRN, BPRO - wejście i wyjście szeregowego łańcucha priorytetów

BCLK, CCLK - sygnały zegarowe magistrali zmienny i stały (max.10MHz);

-12V,-10V,-5V,0V,5V,12V - linie zasilające

5/24

Magistrale systemowe - MULTIBUS

cykl odczytu pamięci

6/24

cykl odczytu urz. zewnętrznego

ADR15..ADR0

ADR15..ADR0

MRDC

IORC

XACK

XACK

D15..D0

D15..D0

cykl zapisu pamięci

cykl zapisu urz. zewnętrznego

ADR15..ADR0

ADR15..ADR0

MWTC

IOWC

XACK

XACK

D15..D0

D15..D0

Magistrale systemowe - MULTIBUS II

Magistrala MULTIBUS II Intela

dla dowolnego typu mikroprocesora, takŜe systemów wieloprocesorowych,

szybkość transmisji do 40MB/s

MULITIBUS II - to standard całego systemu wieloprocesorowego:

architektury, magistral, elektryczny, mechaniczny

Standard przewiduje 5 magistral do wymiany informacji:

⇒ wielokanałowa (multichannel DMA bus);

⇒ prywatna iSBX (intel IO expansion bus);

⇒ lokalna iLBX (Intel local bus extension);

⇒ szeregowa iSSB (intel serial system bus);

⇒ równoległa iPSB (intel parallel system bus)

7/24

Magistrale systemowe - MULTIBUS II

iPSB

ma strukturę 5-szynową:

⇒szyna danych i adresów:

multipleksowane AD0..AD31 oraz PAR0..PAR3

(kontrolne bity parzystości po jednym na kaŜdy bajt szyny);

⇒szyna sygnałów arbitraŜu: BREQ i 6 linii ARBx na numer priorytetu;

⇒szyna sterowania systemem: linie SC0..SC9,

których znaczenie zaleŜy od realizowanego cyklu magistrali;

⇒szyna sygnałów błędów: BUSRER - błąd parzystości na ADx lub SCx,

TIMEOUT - przekroczenie limitu czasu na potwierdzenie przyjęcia

transmisji;

⇒szyna sterowań centralnych: RST, RSTNC, DCLOW, PROT,

BCLK, CCLK, LACHn

8/24

Magistrale systemowe - MULTIBUS II

9/24

Protokół magistrali iPSB składa się z trzech cykli:

cykl arbitraŜu = faza rozstrzygania o dostępie do magistrali

+ faza przekazywania magistrali wybranemu procesorowi;

cykl przesłania = faza Ŝądania (wysłanie adresu i rozkazu)

+ faza odpowiedzi (dane i ich stroby)

cykl komunikatu o wykrytym błędzie = faza sygnalizacji

+ faza powrotu

Magistrale systemowe - VME

10/24

Magistrala VME (Versa Module Eurocard - Mostek, Motorola, Signetics)

1981 - wersja A: połączenie standardu VERSAbus ze standardem płyt Eurokarty

1982 - wersja B

1985 - wersja C: wynik prac komisji IEC i IEEE

obecna wersja D: dostosowanie do mikroprocesorów 64-bitowych

Systemy modułowe z VME królują na rynku zastosowań przemysłowych

i militarnych.

Cechy:

• asynchroniczna,

• 32 linie danych (wersja C), 64 (wersja D);

• 32 linie adresów (wersja C), 64 (wersja D);

• niemultipleksowana (do wersji C), multipleksowana w wersji D;

• 7 poziomów przerwań;

• moŜliwa praca wieloprocesorowa

• szeroka oferta rynkowa kaset i modułów w tym standardzie,

dostarczanych przez wielu producentów;

Magistrale systemowe - VME

11/24

Cechy c.d.

• występują 2 typy modułów: master - inicjator transmisji i slave - podrzędne;

• do jednej magistrali moŜna dołączyć wiele masterów - ich Ŝądania dostępu

do magistrali rozstrzyga centralny arbiter wchodzący w skład obligatoryjnego

sterownika magistrali, rezydującego w skrajnym lewym gnieździe;

• sterownik magistrali zawiera moduły funkcjonalne:

sterownik magistrali

nadajnik

zegara

systemu

czasomierz

magistrali

nadajnik

sygnału

IACK*

VMEbus

arbiter

monitor

stanu

zasilania

Magistrale systemowe - VME

12/24

Cechy c.d.

• maksymalna prędkość do 40MB/s;

• maksymalna długość 50cm;

• płyta magistrali zawiera od 2 do 21 gniazd;

• sygnały magistrali tworzą 4 szyny:

⇒szynę transmisji danych (dane, adresy i podstawowe sterowania z potwierdzeniem);

⇒szynę arbitraŜu transmisji danych (wykorzystywana przez mastery

i moduły obsługi przerwań do przejmowania kontroli nad szyną transmisji danych);

⇒szynę przerwań priorytetowych (7 linii przerwań priorytetowych,

potwierdzenie przyjęcia przerwania zwykłe i łańcuchowe);

⇒szynę sygnałów pomocniczych

(zerowanie systemu, zegary, zasilania +5V, +12V, -12V, itp.);

• sygnały magistrali są podzielone na dwa złącza J1 i J2 (opcjonalne),

kaŜde po 32x3 styki, J2 zawiera 8 st. linii adresowych, 16 st. linii danych,

powtórzone zasilania, 64 linii uŜytkownika;

• moduły VME mają wysokość 3U i tylko J1 albo 6U i oba złącza J1 i J2;

Magistrale systemowe - VME

13/24

Przykładowa konstrukcja pakietu JC z magistralą VME:

pakiet JC

właściwa JC

monitor

adresów

moduł

master

moduł

Ŝądania

dostępu do

magistrali

VMEbus

moduł

obsługi

przerwań

moduł

zgłaszający

przerwanie

Magistrale systemowe - VME

14/24

Przykładowa konstrukcja pakietu we/wy lub pamięci:

pakiet typu slave

porty we/wy lub pamięć

moduł

zgłaszający

przerwanie

moduł slave

VMEbus

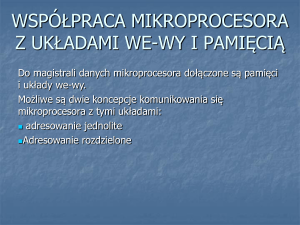

Magistrale systemowe - PC-ty

15/24

Magistrale równoległe PC-tów

8086/88

286

386

386

386

386

486

486

486

486

486

P5

P5

P5

ISA

P6 (Pro)

PCI

MCA

EISA

20Mb/s

33Mb/s 12,5Mb/s 132/264Mb/s

ISA - Industry Standard Architecture

EISA - Extended Industry Standard Architecture

MCA - Micro Channel Architecture

VLB - VESA Local Bus (Video Electronic Standards Association)

PCI - Peripheral Component Interconnect

VLB

120Mb/s

Magistrale systemowe - MCA i VLB

16/24

MCA- wymyślona przez IBM na potrzeby PS/2; po 32 linie danych i adresów;

ukierunkowana na wielozadaniowe S.O. i procesory 386/86;

do 16 mikroprocesorów na kartach rozszerzeń; kanały DMA 32-bitowe;

rozbudowana pamięć konfiguracji; karty rozszerzeń mają identyfikatory;

konfigurowanie kart tylko programowe; karty mogą być programowo włączane

i wyłączane; szybkość transmisji do 20MB/s.

VLB - 32-bitowa magistrala lokalna dedykowana dla sterowników dysków

i kart wideo; oparta na magistrali lokalnej procesorów 386/486;

złącze VLB umieszczane na przedłuŜeniu gniazda ISA; szybkość transmisji do

120MB/s.

Magistrale systemowe - ISA

ISA

17/24

tył obudowy

GND

RESET

+5V

IRQ2

-5V

DRQ2

-12V

/0WS

+12V

GND

/SMEMW

/SMEMR

/IOW

/IOR

/DACK3

DRQ3

/DACK1

DRQ1

/REF

CLK

IRQ7

IRQ6

IRQ5

IRQ4

IRQ3

/DACK2

T/C

ALE

+5V

OSC

GND

B1

B10

B20

B31

/IOCHK

D7

D6

D5

D4

D3

D2

D1

D0

A10 IOCHRDY

AEN

A19

A18

A17

A16

A15

A14

A13

A12

A20 A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A31 A0

A1

szybkość transmisji

do 10MB/s

/MEMCS16 D1

/IOCS16

IRQ10

IRQ11

IRQ12

IRQ15

IRQ14

/DACK0

DRQ0

/DACK5 D10

DRQ5

/DACK6

DRQ6

/DACK7

DRQ7

Vcc

/MASTER

GND D18

SBHE

LA23

LA22

LA21

LA20

LA19

LA18

LA17

/MEMR

C10 /MEMW

SD08

SD09

SD10

SD11

SD12

SD13

SD14

C18 SD15

C1

Magistrale systemowe - EISA

18/24

EISA (Extended Industry Standard Architecture)

Cechy odróŜniające od ISA:

poziom

ISA

• po 32 linie adresów i danych;

• dodano w sumie 90 nowych sygnałów do ISA;

poziom

EISA

• umoŜliwia pełne wykorzystanie 32-bitowych procesorów;

• zachowuje zgodność elektryczną i mechaniczną z ISA;

• dopuszcza wieloprocesorowość z hierarchiczno-priorytetowym dostępem

do wspólnych zasobów, dodatkowe procesory na kartach rozszerzeń;

• zwiększone moŜliwości DMA:

−bloki do 4GB (w ISA do 64/128kB);

−7 kanałów 8/16/32-bitowych (automatycznie dobierana “szerokość kanału”);

−rotacyjny zamiast stałego system przydziału kanałów urządzeniom;

Magistrale systemowe - EISA

Cechy odróŜniające EISA od ISA, c.d.:

• przerwania zgłaszane poziomem a nie zboczem jak w ISA,

co jest bardziej odporne na zakłócenia;

• 4kB pamięci konfiguracji (dane płyty głównej i zainstalowanych kart);

• konfigurowanie kart wyłącznie programowe;

• rozbudowany kontroler magistrali, realizujący między innymi tryb burst,

łamanie i składanie bajtów przy dostępie do obiektów 8- i 16-bitowych,

rozróŜniający cykle ISA i EISA;

• szybkość transmisji do 33MB/s.

Zastosowania:

przemysłowe systemy mikrokomputerowe;

19/24

Magistrale systemowe - PCI

20/24

PCI

Opracowana przez Intela jako odmiana 32-bitowej magistrali lokalnej,

niezaleŜnej od typu procesora.

UmoŜliwia budowę bardzo duŜych systemów:

• do 256 magistral PCI w jednym systemie;

• kaŜda z magistral moŜe obsługiwać do 32 urządzeń;

• kaŜde urządzenie moŜe spełniać do 8 funkcji.

Typowe płyty główne mają 1 magistralę PCI obsługującą do 10 urządzeń.

Częstotliwość pracy: 33MHz (66MHz) ⇒ szybkość transmisji 132MB/s (264MB/s).

64-bitowe rozszerzenie ma dwukrotnie większą szybkość transmisji.

Magistrale systemowe - PCI

21/24

Typowa konfiguracja PCI w komputerze typu PC

µP

cache

sterownik PAO

sterownik PCI-arbiter

RAM

k.dźwiękowa

k.grafiki

k.wideo

PCI

interfejs

magistrali

zewnętrznej

mag.

ISA

EISA

MCA

k.sieciowa

karty

rozszerzeń

k.HDC/FDC

interfejs

magistrali

SCSI

mag.

SCSI

urządzenia

SCSI

Magistrale systemowe - PCI

22/24

Pamięć konfiguracji PCI

KaŜde z urządzeń ma 256B pamięci konfiguracji, które zawierają:

• 64B nagłówka o standardowym formacie:

Nagłówek zawiera między innymi dane: identyfikatory producenta

i urządzenia, rejestr komend, rejestr stanu, numer wersji urządzenia,

kod klasy urządzenia, rozmiar linii pamięci cache,

minimalny czas transmisji, itd.

• 192B specyficznych danych danego urządzenia.

Konfigurowanie magistrali i urządzeń PCI jest automatyczne/programowe.

Magistrale systemowe - PCI

23/24

Są dwa typy urządzeń dołączanych do PCI:

•inicjatory (I), mogące przejmować sterowanie magistralą;

•slave-y (S), tylko reagują na Ŝądania transmisji (nadają/odbierają).

MoŜliwe są dwa warianty komunikacji: I ↔ I oraz I ↔ S.

tył obudowy

Spotyka się 4 warianty gniazd

magistrali PCI, zaleŜnie od

podstawowe

120 styków

szerokości szyny danych

i napięcia zasilającego:

3,3V

5V

32b

64 styków

rozszerzenia

3,3V

5V

64b

Magistrale systemowe - PCI

24/24

Przerwania na PCI

Magistrala udostępnia tylko 4 kanały przerwań, ale mogą one być współuŜywalne

przez większą liczbę urządzeń. Arbiter magistrali PCI zawiera układ

programowalnego routera przerwań (PRP) sprzętowych.

IRQ8

INTA

urz.

X

8259A

slave

INTB

INTC

PRP

IRQ15

INTD

urz.

Y

urz.

Z

IRQ0

8259A

master

IRQ7