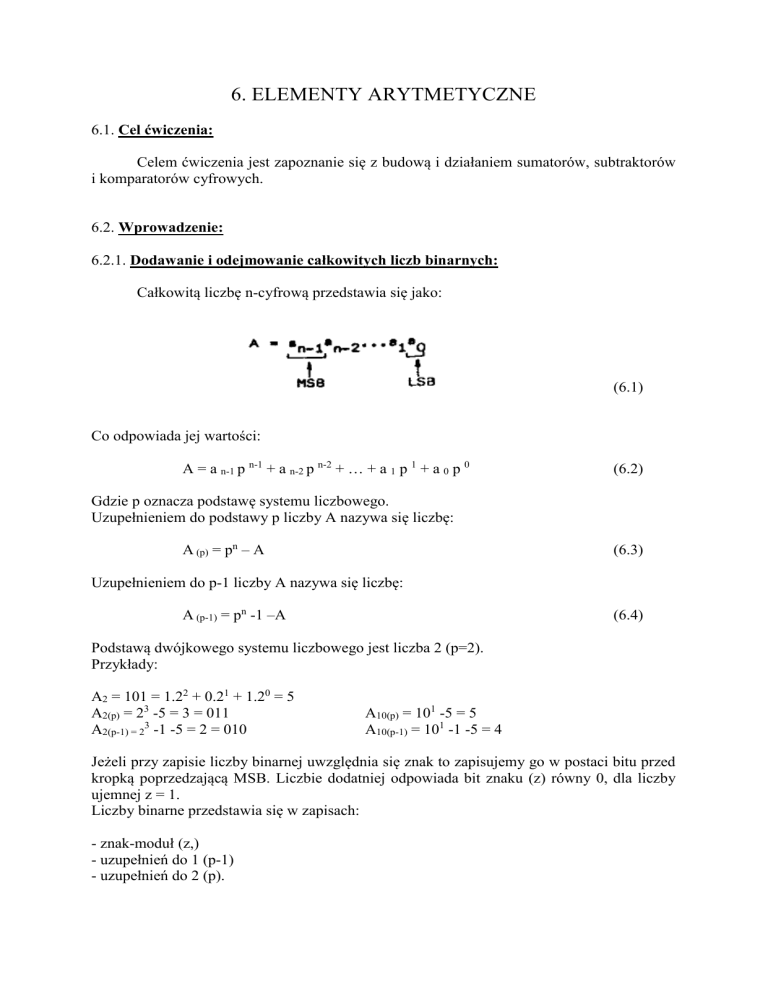

6. ELEMENTY ARYTMETYCZNE

6.1. Cel ćwiczenia:

Celem ćwiczenia jest zapoznanie się z budową i działaniem sumatorów, subtraktorów

i komparatorów cyfrowych.

6.2. Wprowadzenie:

6.2.1. Dodawanie i odejmowanie całkowitych liczb binarnych:

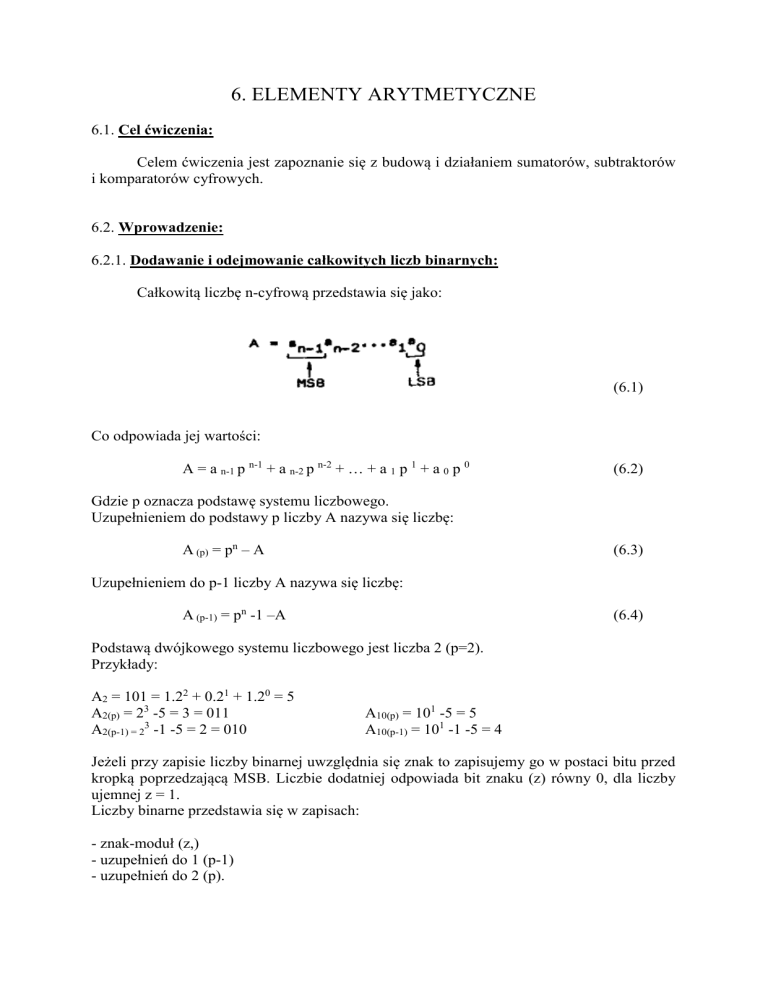

Całkowitą liczbę n-cyfrową przedstawia się jako:

(6.1)

Co odpowiada jej wartości:

A = a n-1 p n-1 + a n-2 p n-2 + … + a 1 p 1 + a 0 p 0

(6.2)

Gdzie p oznacza podstawę systemu liczbowego.

Uzupełnieniem do podstawy p liczby A nazywa się liczbę:

A (p) = pn – A

(6.3)

Uzupełnieniem do p-1 liczby A nazywa się liczbę:

A (p-1) = pn -1 –A

(6.4)

Podstawą dwójkowego systemu liczbowego jest liczba 2 (p=2).

Przykłady:

A2 = 101 = 1.22 + 0.21 + 1.20 = 5

A2(p) = 23 -5 = 3 = 011

A2(p-1) = 23 -1 -5 = 2 = 010

A10(p) = 101 -5 = 5

A10(p-1) = 101 -1 -5 = 4

Jeżeli przy zapisie liczby binarnej uwzględnia się znak to zapisujemy go w postaci bitu przed

kropką poprzedzającą MSB. Liczbie dodatniej odpowiada bit znaku (z) równy 0, dla liczby

ujemnej z = 1.

Liczby binarne przedstawia się w zapisach:

- znak-moduł (z,)

- uzupełnień do 1 (p-1)

- uzupełnień do 2 (p).

Liczba dodatnia ma w tych zapisach taką samą postać, liczba ujemna w każdym zapisie jest

odmienna.

Przykłady:

6 = 0.1102 we wszystkich podanych zapisach ma jednakową postać.

-6 = 1.1102(zm) = 1.0012(p-1) = 1.0102(p)

Dalej dla zapisów uzupełnień liczb będą używane także oznaczenia z gwiazdką np.: 1* uzupełnienie liczby binarnej do 1.

6.2.1.1. Zapis znak-moduł.

W zapisie zm liczby o równych wartościach bezwzględnych różnią się wyłącznie

bitem znaku. Liczba 0 ma tutaj podwójną postać:

+0 = 0.02(zm)

-0 = 1.02(zm).

W operacjach arytmetycznych nie biorą udziału bity znaków składników. Przy jednakowych

znakach składników sumowane są moduły a znak wyniku przyjmuje znak składników.

Przykłady:

Przy różnych znakach składników do modułu dodanej dodaje się uzupełnienie do 1 dodajnika

i jeżeli wystąpi przeniesienie cykliczne dodaje się je do ostatniego wyniku, jeżeli

przeniesienie cykliczne nie wystąpi należy wyznaczyć uzupełnienie do 1 otrzymanego

wyniku. Znak wyniku przyjmuje wartość równą znakowi składnika o większym module.

Przykłady:

6.2.1.2. Zapis uzupełnień do 1.

W zapisie uzupełnień do 1 każdą liczbę ujemną przedstawia się jako 1 a operację

dodawania przeprowadza się wraz z bitem znaku. Jeżeli występuje przeniesienie cykliczne to

dodajemy go do ostatniego wyniku. Przy ujemnym wyniku końcowym rezultatem jest 1*

modułu otrzymanego wyniku z zachowaniem bitu znaku.

W zapisie uzupełnień do 1 istnieją dwie interpretacje liczby 0:

+0 = 0.02(p-1)

Przykłady:

-0 = 1.12(p-1)

Z ostatniego przykładu wynika, że ujemne zero występuje w tym zapisie tylko przejściowo a

przy końcowej operacji tworzenia 1* należy także zmienić wartość bitu znaku z na 0, co jest

odstępstwem od reguł podanych na początku niniejszego podpunktu.

6.2.1.3. Zapis uzupełnień do 2.

Jest to w przypadku liczb binarnych zapis uzupełnienia do podstawy. W układach

sumatorów pracujących w zapisie uzupełnień do 2 wykorzystuje się równoważność 2* i sumy

1* tej liczby plus 1.

A2(p) = A2(p-1) + 1

(6.5)

Działania arytmetyczne przeprowadza się w tym zapisie wraz z bitem znaku, przeniesienie

cykliczne pomija się. Liczby ujemne przedstawia się jako 2*. Przy ujemnym wyniku

końcowym rezultatem jest 2* modułu otrzymanego wyniku z zachowaniem bitu znaku. W

zapisie uzupełnień do 2 liczba 0 przedstawiona jest jako 0.02(p).

Przykłady:

6.2.2. Działania dodawania i odejmowania arytmetycznego całkowitych liczb

dziesiętnych kodowanych dwójkowo:

Ograniczono się tutaj do rozważenia problemu dodawania i odejmowania liczb

dziesiętnych BCD przedstawionych w naturalnym kodzie o wagach 8421.

Zasadniczo działania dodawania i odejmowania liczb BCD 8421 przeprowadza się

w zapisach:

- znak-moduł

- uzupełnień do 9 (p-1)

- uzupełnień do 10 (p)

Istnieje również zapis wynikający z 4 bitowego przedstawienia cyfry BCD i nosi on nazwę

- uzupełnień do 15.

Dla otrzymania prawidłowego wyniku dodawania dwu liczb BCD stosuje się poprawkę w

każdej dekadzie, której wartość przekroczy 9. Poprawka ta polega na dodaniu cyfry 6 do

danej dekady z jednoczesnym przeniesieniem przepełnienia do następnej dekady.

Przykłady:

Odejmowanie liczb BCD 8421 zastępuje się dodawaniem uzupełnienia do (p) lub (p-1)

odjemnika. W tym przypadku jest to 10* lub 9*. Dla liczb BCD, odmiennie niż w przypadku

liczb BIN, bit znaku z równy 1 określa liczbę dodatnią a gdy z = 0 liczbę – ujemną.

Operacje odejmowania przeprowadza się podobnie jak dla liczb binarnych (por.

punkt 6.2.1).

Dla lepszego zrozumienia reguł rządzących operacjami dodawania i odejmowania

liczb BCD 8421, przykłady w większości przypadków przedstawiono dla liczb jedno i

dwucyfrowych.

6.2.2.1. Zapis znak – moduł.

Zapis zm liczb BCD 8421 odpowiada zapisowi zm liczb BIN (patrz p. 6.2.1.1).

Zmiana dotyczy zastąpienia uzupełnienia do 1 (BIN) uzupełnieniem do 9 (BCD).

Przykłady:

Wykonanie działania -5 -6 = -11 jest analogiczne, jedynie wynik przyjmuje znak „ – ” (bit

znaku sumy zS przyjmuje wartość 0).

Wykonanie działania -9 + 3 = -6 jest analogiczne, zS = 0.

6.2.2.2. Zapis uzupełnień do 9.

Zapis uzupełnień do 9 odpowiada zapisowi uzupełnień do 1 – patrz p. 6.2.1.2.

Różnica w stosunku do zapisu 1* polega na dodawaniu przeniesienia cyklicznego z

sumowania dekad a nie po zsumowaniu dekad i bitów znaku.

Przykłady:

6.2.2.3. Zapis uzupełnień do 10.

Zapis uzupełnień do 10 odpowiada zapisowi uzupełnień do 2 – patrz p. 6.2.1.3.

Uzupełnienie 10* liczby BCD tworzy się na podstawie wzoru (6.5):

A10(p) = A10(p-1) + 1

Przykłady:

A10 = 9

A10 = 12

A10 = 100

A10 = 0

A10(p) = 0 + 1 = 1

A10(p) = 87+1 = 88

A10(p) = 899+1 = 900

A10(p) = 9+1 = (1 ←) 0 przeniesienie pomija się

Powyższa interpretacja matematyczna liczby 0 jest zgodna z jej przedstawieniem jako

1.0000 w zapisie 10.

Dla liczb poprzedzonych zerami zapis wygląda następująco:

Przykłady:

6.2.2.4. Zapis uzupełnień do 15.

Zapis uzupełnień do 15 nosi również nazwę zapisu uzupełnień do 1 dla liczb BCD,

ponieważ 15 otrzymuje się przez zanegowanie wszystkich bitów liczby ujemnej. Nazwa

uzupełnienia do 15 wynika z czterobitowego przedstawienia liczby dziesiętnej, dla którego

maksymalna wartość wynosi 1111 = 15.

Przykłady:

A = 9 = 1001

A = 73 = 0111 0011

A = 05 = 0000 0101

ABCD(15*) = 0110 = 616 = 15 - 9

ABCD(15*) = 1000 1100 = 8C16 = (15-7)(15-3)

ABCD(15*) = 1111 1010 = FA16 = (15-0)(15-5)

Ze względu na duża komplikację algorytmu układu dodająco – odejmującego dla zapisu 15

rozpatrzony zostanie tylko przypadek układu odejmującego, wykonującego działanie

S = A – B. Operacja odejmowania jest w tym zapisie sprowadzona do dwustopniowego

dodawania. Pierwsza suma powstaje w wyniku dodania kolejnych bitów liczby, będącej

odjemną oraz uzupełnienia do 15 odjemnika z uwzględnieniem przeniesień i przeniesienia

cyklicznego. Jest to sumowanie analogiczne jak w zapisie uzupełnień do 1 liczb BIN, z tym,

że wynik podzielony jest na tetrady. Bit przeniesienia cyklicznego określa znak końcowego

wyniku i składnik drugiej sumy, którym jest pierwsza suma gdy zS = 1 (lub negacja jej bitów

gdy zS = 0). Druga suma zawiera również składnik korekcji dla tetrad, których wartość

przekroczyła liczbę 9.

Korekcja ta przyjmuje wartość +10 = 1010, co odpowiada uzupełnieniu do 2 liczby 6.

Przeniesienia w sumowaniu korekcyjnym pomija się.

Przykłady:

Z ostatniego przykładu wynika, że liczba 0 w zapisie uzupełnień do 15 przyjmuje znak „ – ”.

6.2.3. Sumator:

Sumator jest układem wykonującym dodawanie dwu liczb. W przypadku

sumowania liczb binarnych podstawowy element sumatora liczb wielobitowych spełnia

funkcje logiczne zgodnie z tablicą 6.1, gdzie:

Ci-1 – przeniesienie z niższej pozycji,

Ai – bit dodajnej,

Bi – bit dodajnika,

Si – bit sumy,

Ci – przeniesienie do wyższej pozycji

Tablica 6.1

Tablica stanów sumatora

Ci - 1

Ai

Bi

Si

Ci

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

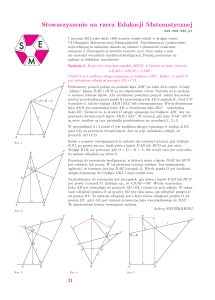

Rys. 6.1. Sumator 1-bitowy

a) siatki Karnaugha , b) symbol , c) schemat

Na rys. 6.1a przedstawiono siatki Karnaugha dla sumy Si i przeniesienia Ci wg których

otrzymujemy funkcje:

Zależność (6.6) spełnia układ kombinacyjny z rys. 6.1c, przy czym możliwe są również inne

praktyczne realizacje sumatora, wynikające z różnorodnych przekształceń wzorów (6.6).

Uproszczoną postacią sumatora jest półsumator, który nie posiada wejścia Ci-1.

Podstawiając we wzorach (6.6) Ci-1 = 0 otrzymujemy:

Zależność (6.7) spełnia układ z rys. 6.2a.

Rys. 6.2. Półsumator a) schemat , b) realizacja sumatora z 2 półsumatorów

Sumatory wielobitowe można podzielić na:

- dwójkowe (sumowanie liczb binarnych),

- dziesiętne (sumowanie liczb dziesiętnych kodowanych dwójkowo).

Działanie sumatora może odbywać się szeregowo – rys. 6.3 (sumowane są kolejne bity

dodajnej i dodajnika) lub równolegle – rys. 6.3 (wszystkie bity sumowane są jednocześnie).

Rys. 6.3. Sumator szeregowy

Rys.6.4. Sumator równoległy z przeniesieniami szeregowymi

Z układu sumatora szeregowego można wyeliminować rejestr sumy przez szeregowe

adresowanie rejestru jednego ze składników kolejnymi, częściowymi wynikami dodawania.

W wielobitowych sumatorach równoległych przeniesienia mogą być dokonywane

szeregowo lub równolegle. W tym ostatnim przypadku znacznie wzrasta szybkość działania

sumatora.

Sumator akumulujący jest układem, który zamiast dodajnika wprowadza do

sumatora wynik poprzedniego dodawania (rys. 6.5). Dodatkowy element sumatora

akumulującego, spełniający funkcję pamięci (np. rejestr, zespół przerzutników) nosi nazwę

akumulatora.

Rys. 6.5. Sumator akumulujący a) szeregowy , b) równoległy

W klasie TTL produkowane są sumatory 1,2 i 4-bitowe (patrz Dodatek B).

6.2.4. Subtraktor:

Odejmowanie dwu liczb binarnych realizuje układ zwany subtraktorem.

Tablica 6.2

Tablica stanów subtraktora

Vi - 1

Ai

Bi

Di

Vi

0

0

0

0

0

0

0

1

1

1

0

1

0

1

0

0

1

1

0

0

1

0

0

1

1

1

0

1

0

1

1

1

0

0

0

1

1

1

1

1

W tablicy 6.2 oznaczono:

Vi-1 – pożyczka dla niższej pozycji,

Ai – bit odjemnej,

Bi – bit odjemnika,

Di – bit różnicy,

Vi – pożyczka z wyższej pozycji.

Rys. 6.6. Subtraktor 1-bitowy a)siatki Karnaugha , b) symbol

Na podstawie siatek Karnaugha z rys. 6.6 można napisać:

Porównując wzory (6.8) i (6.7) można stwierdzić, że dla Vi-1 = Ci-1 wyrażenie dla różnicy i

sumy są równoważne, tj. Di = Si ; w wyrażeniach dla pożyczki i przeniesienia różnica tkwi w

negacji argumentu Ai.

Subtraktor można więc nazwać pewnym przypadkiem sumatora ze zmianą Ai najej

negację w funkcji pożyczki.

Jeżeli we wzorach (6.8) przyjmiemy Vi-1 = 0 to otrzymamy wyrażenie opisujące

półsubtraktor:

Rys. 6.7. Schematy funkcjonalne sumatorów – subtraktorów liczb BIN a) dla zapisu znak –

modół , b) dla zapisu uzupełnień do 1 , c) dla zapisu uzupełnień do 2

Układy wielobitowych subtraktorów budowane są analogicznie jak odpowiednie sumatory –

por. rys. 6.3 i 6.4. Praktycznie do budowy wielobitowych układów odejmujących

wykorzystuje się scalone sumatory uzupełnione dodatkowymi układami wejściowymi,

wyjściowymi i generującymi znak wyniku.

Analizując kolejne kroki podczas operacji dodawania i odejmowania liczb binarnych

(patrz p. 6.2.1) można narysować schematy funkcjonalne układów realizujących działania

S = ±A±B dla poszczególnych zapisów – rys. 6.7. Linią przerywaną zaznaczono bloki nie

występujące w układach uproszczonych, wykonujących działanie S = A±B. Z porównania

rysunków 6.7a, b i c widać, że największe komplikacje w budowie posiada układ dodająco –

odejmujący dla zapisu znak – moduł, dlatego też jest on bardzo rzadko realizowany.

6.2.5. Sumator dziesiętny kodowany dwójkowo:

W przypadku dodawania i odejmowania liczb binarnych mamy zazwyczaj kłopoty z

szybką interpretacją wyniku, tzn. przetworzeniem go na powszechnie używany dziesiętny

system liczbowy. Rozwiązaniem tego zagadnienia jest albo budowa konwertera BIN → BCD

dla wyniku, albo bezpośrednie działania arytmetyczne na liczbach dziesiętnych kodowanych

dwójkowo.

W układach arytmetycznych stosuje się najczęściej następujące kody BCD:

- naturalny kod dziesiętny o wagach 8421,

- kod z nadmiarem 3 (”+3”),

- kod Aikena o wagach 2421

Ograniczmy się tutaj do najpopularniejszego kodu BCD 8421. Dodając do siebie

dwie liczby BCD i uwzględniając przeniesienie z poprzedniej dekady Cm-1 = 1 możemy co

najwyżej otrzymać liczbę 9+9+1 = 19. Sumator BCD będzie się więc różnił od sumatora liczb

binarnych wprowadzonym dodatkowo układem kombinacyjnym dla przeniesienia do

następnej dekady Cm oraz arytmetycznym układem korekcji (sterowanym z układu

przeniesienia) dodającym odpowiednią poprawkę, gdy wynik dla danej dekady przekroczy 9.

Z powyższego wynika schemat funkcjonalny sumatora BCD, przedstawiony na rys. 6.8.

Wszystkie możliwe wyniki występujące przy sumowaniu dwu liczb BCD i przeniesienia C M-1

ilustruje tablica 6.3.

Tablica 6.3

Suma

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

C’m

S’m3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

BIN

S’m2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

S’m1

S’m0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Cm

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

BCD 8421

Sm3

Sm2

Sm1

0

0

0

00

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

1

0

0

1

1

0

1

1

1

0

0

1

0

0

Uwagi

Sm0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Nie

wymaga

korekcji

Wymaga

korekcji

+6

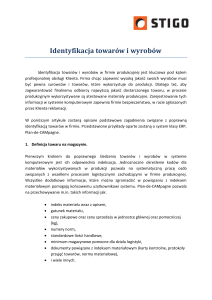

Rys. 6.8. Schemat funkcjonalny jednodekadowego sumatora dziesiętnego.

Z tablicy tej wynika, że dla wyniku większego niż 9 przeniesienie Cm sumatora BCD powinno

przyjąć wartość 1, a wtedy do wyniku Sm należy dodać poprawkę +6.

Rys. 6.9. Jednodekadowy sumator BCD 8421 , a) siatka Karnaugha , b) schemat sumatora

zbudowanego z 2 sumatorów 4 - bitowych

Na podstawie siatki Karnaugha z rys. 6.9a można napisać funkcję jaką musi spełniać

przeniesienie Cm

Cm = C’m + S’m3 S’m2 + S’m3 S’m1

(6.10)

Schemat dekady sumatora BCD 8421 zbudowany w oparciu o sumatory 4-bitowe przedstawia

rys. 6.9b.

Wielodekadowy sumator BCD buduje się łącząc odpowiednio ze sobą

jednodekadowe sumatory BCD np. w sumator równoległy z przeniesieniami szeregowymi

(por. rys. 6.4) lub przyłączając do dekady sumatora BCD zespół rejestrów 4-bitowych (por.

rys. 6.3). W tym drugim przypadku otrzymany sumator szeregowo – równoległy ze względu

na równoległe sumowanie liczb w każdej dekadzie i szeregowe podawanie przeniesienia.

Budowa dziesiętnego sumatora akumulującego jest analogiczna jak w przypadku

równoległego sumatora akumulującego przedstawionego na rys. 6.5b.

6.2.6. Subtraktor dziesiętny kodowany dwójkowo:

Istnieje możliwość zbudowania jednodekadowego subtraktora BCD, realizującego

odejmowanie bezpośrednie, jednak ze względu na jego skomplikowaną budowę nie stosuje

się praktycznie tego typu układów.

Operacja odejmowania, podobnie jak dla liczb BIN, sprowadzana jest do dodawania

odjemnej i odpowiedniego uzupełnienia odjemnika, przy zachowaniu reguł dotyczących

przeniesienia opisanych w p.6.2.2 (rys. 6.10).

W praktyce do budowy wielodekadowych układów odejmujących wykorzystuje się scalone

sumatory binarne oraz kombinacyjne lub arytmetyczne bloki uzupełnień i generowania znaku

wyniku.

6.2.7. Komparator:

Komparator jest układem porównującym wartości dwu lub więcej liczb binarnych.

Komparator uniwersalny posiada wyjścia odpowiadające relacjom:

A < B, A = B, A > B. Komparator uproszczony daje nam zwykle informację wyjściową w

postaci: A = B, A ≠ B. Ze względu na sposób działania komparatory można podzielić na

równoległe i szeregowe, przy czym komparacji liczb można dokonywać poczynając od MSB

lub LSB. Komparatory równoległe mogą być budowane w postaci układów kombinacyjnych i

wtedy ich wyjścia realizują wielowymiarową funkcję logiczną wynikającą z metod

minimalizacji, bądź w postaci układów iteracyjnych, będących złożeniami komparatorów 1bitowych z elementami blokady następnych stopni i elementami wyjściowymi. Schematy

funkcjonalne komparatorów szeregowych i równoległych przedstawiają rys. 6.11 i 6.12.

Komparatory mogą być również budowane w oparciu o elementy arytmetyczne. Przykład

takiego komparatora, działającego na zasadzie badania wyniku odejmowania, przedstawia

rys. 6.13.

Najprostszym rodzajem komparatora jest komparator 1-bitowy, nie uwzględniający

przeniesień komparacji z wyższej pozycji. Taki komparator stanowi w powiązaniu z dwoma

przerzutnikami komparator szeregowy por. rys. 6.11 i rys. 6.14b. Funkcje komparatora 1bitowego przedstawia tablica 6.4.

Na podstawie siatek Karnaugha (rys. 6.14a)

Przekształcając wzór 6.11b) otrzymujemy zależność:

Realizację komparatora według wzorów (6.11) przedstawia rys. 6.14b. Podstawowym

elementem wielobitowego komparatora iteracyjnego (patrz rys. 6.12b) jest komparator

iteracyjny 1-bitowy. Posiada on jedynie wejścia i wyjścia dla relacji większości i mniejszości

a relacja równości generowana jest w dodatkowym członie wyjściowym na podstawie

(6.11d). Komparator iteracyjny 1-bitowy spełnia funkcje logiczne zgodnie z tablicą 6.5.

Rys.6.11. Komparator szeregowy

a) porównujący liczby od MSB, b) porównujący liczby od LSB

Tablica 6.5

Tablica stanów jednobitowego komparatora iteracyjnego

Rys.6.12 Komparator równoległy: a) kombinacyjny , b) iteracyjny

Rys.6.13 Układ odejmujący jako komparator

Według siatek Karnaugha z rys . 6.15 a otrzymujemy zależności:

Schemat 1-bitowego komparatora iteracyjnego przedstawia rys. 6.15b.

Zasadę konstruowania komparatorów kombinacyjnych (patrz rys. 6.12a) przedstawiono na

przykładzie komparatora 2-bitowego. Komparator taki spełnia funkcje logiczne opisane w

tablicy 6.6.

Rys.6.14 Komparator 1-bitowy : a) siatki Karnaugha, b) schemat

Rys. 6.15. Komparator iteracyjny 1-bitowy: a) siatki Karnaugha, b) schemat

Schemat 1-bitowego komparatora iteracyjnego przedstawia rys 6.15 b. Zasadę konstruowania

komparatorów kombinacyjnych ( patrz rys. 6.12 a) przedstawiono na przykładzie

komparatora 2-bitowego . Komparator taki spełnia funkcje logiczne opisane w tablicy 6.6.

Tablica 6.6

Tablica stanów kombinacyjnego komparatora 2-bitowego

Rys.6.16. Komparator kombinacyjny 2-bitowy: a) siatki Karnaugha, b)schemat

Na podstawie niepełnej minimalizacji siatek Karnaugha z rys. 6.16a otrzymujemy po

przekształceniach:

Powyższe zależności spełnia układ z rys. 6.16b.

W klasie TTL produkowany jest uniwersalny komparator kombinacyjny 4-bitowy (układ

7485 – patrz Dodatek B), który praktycznie służy do budowy komparatorów wielobitowych.

6.3. Pytania sprawdzające:

1. Przedstawić liczby 3, 9, 10, 22, 39 oraz ich wszystkie uzupełnienia w zapisach BIN i

BCD 8421.

2. Przeprowadzić we wszystkich zapisach BIN i BCD 8421 następujące działania

arytmetyczne: 3+5, 7+11, 6-9, 9-6, 10-12, -7 -5.

3. Zbudować półsumator: a) z bramek NAND, b) z bramek NOR.

4. Dokonać klasyfikacji sumatorów i omówić działania poszczególnych grup.

5. W jaki sposób może być dokonywana operacja odejmowania liczb BIN oraz BCD

8421?

6. Dokonać syntezy subtraktora BCD wykonującego bezpośrednie odejmowanie liczb

BCD 8421, przedstawić jego realizację.

7. Dokonać syntezy kombinacyjnych oraz arytmetycznych układów wytwarzania

uzupełnień do 9 i do 10 dla jednodekadowej liczby BCD 8421 oraz przedstawić ich

realizację.

8. Jak można sklasyfikować komparatory pod względem szybkości działania?

9. Dokonać syntezy komparatora kombinacyjnego 3-bitowego, przedstawić jego

realizację.

6.4.2. Sumator – subtraktor szeregowy (SSz), szeregowy sumator akumulacyjny

(AkSSz):

Sumator i subtraktor szeregowy został zbudowany na podstawie schematu blokowego z rys.

6.3. Jako rejestry R1, R2 składników zastosowano uniwersalne rejestry 4-bitowe (które

wykorzystuje się także do badania komparatora szeregowego). Przełączenie zestyków

przycisku PKS (WPISYWANIE) powoduje przeniesienie stanów wejść równoległych

rejestrów R1, R2 na wyjścia. Operacja dodawania lub odejmowania odbywa się krokami

(wyznaczonymi impulsami taktującymi) i rozpoczyna się od bitów o najniższych wagach –

przełącznik PK4 powinien znajdować się w pozycji PRZESUWANIE W PRAWO. Rejestr

sumy R3 jest w tym przypadku rejestrem 8-bitowym, co umożliwia wielokrotne sumowanie

liczb 4-bitowych w układzie szeregowego sumatora akumulującego. Przerzutnik P1 typu D

daje opóźnienie o 1 takt przeniesienia Ci lub pożyczki Vi.

Szeregowy sumator akumulujący uzyskuje się łącząc ostatnie wyjście Q7 rejestru

sumy R3 z wejściem Bi sumatora 1-bitowego – patrz rys. 6.5a.

Kolejność operacji dla dokonania działania arytmetycznego w układzie SSz jest

następująca: zerowanie, wpisanie składników do rejestrów, taktowanie. Dla układu AkSSz

zerowanie poprzedza szereg kolejnych cykli wpisywania i taktowania. W przypadku SSz

wynik uzyskuje się po 5 impulsach taktujących, dla AkSSz po 8 impulsach.

6.4.3. Sumator – subtraktor równoległy (SR):

Równoległy układ sumatora – subtraktora realizujący działanie S = ±A±B

przedstawia rys. 6.20. Układ liczy w zapisie uzupełnień do 1 a w jego skład wchodzą

wejściowe i wyjściowy układ liczba / uzupełnienie do 1 oraz sumator. Jako elementy dające

na wyjściu liczbę lub jej uzupełnienie do 1 zastosowano bramki XIR sterowane bitem znaku

danej liczby. Do bezbłędnego przeprowadzenia operacji dodawania i odejmowania dwóch

liczb 4-bitowych niezbędne jest zarezerwowanie piątego bitu sumatora dla przeniesienia C4 i

szóstego bitu dla operacji na znakach. W tym przypadku do realizacji układu użyto dwa

sumatory 4-bitowe połączone szeregowo. Na bity 3 i 4 sumatora S2 wprowadzono stany 0 i 1

tak, aby prawidłowo działało przeniesienie cykliczne z C4 sumatora S2 na C0 sumatora S1.

Tak więc pięć pierwszych bitów sumowania stanowi liczbę lub jej uzupełnienie do 1 a bit

szósty jest bitem znaku zS. Bit znaku steruje wyjściowym układem liczba / uzupełnienie do 1,

skąd otrzymuje się poprawną postać wyniku.

6.4.4. Sumator – subtraktor dziesiętny (SD):

Jednodekadowy, równoległy sumator – subtraktor dziesiętny przedstawiony na rys.

6.21 jest układem liczącym w kodzie BCD 8421 w zapisie uzupełnienia odjemnika do 9.

Sumator BCD zbudowany jest na podstawie rys. 6.9b (sumatory S4, S5 oraz układ

kombinacyjny dla przeniesienia). Sumator S3 wraz z bramkami XOR tworzy układ liczba /

uzupełnienie do 9 sterowany bitem znaku liczby B. W przypadku wykonywania przez układ

sumatora działania S = A + B na wejście C-1 należy podać 0 lub 1. Dla układu subtraktora (S

= A – B) przeniesienie C0 powinno być połączone z wejściem C-1 przy czym wynik S jest

poprawny dla S > 0 (C0 = 1) oraz jest uzupełnieniem do 9 dla s < 0 (C0 = 0). Sumator ten nie

zawiera bowiem wyjściowego układu liczba / uzupełnienie do 9.

6.4.5. Komparator szeregowy (KSz):

Komparator szeregowy zbudowano z przerzutników P2, P3 typu JK. Dla

uproszczenia układu wykorzystano tutaj funkcję iloczynu realizowanego na wejściach J

elementu 7472 (por. rys. 6.11a).

KSz współpracuje z rejestrami R1, R2 oraz układami taktowania i zerowania

wspólnymi dla SSz – patrz rys. 6.19. Komparator porównuje liczby od bitów o najwyższych

wagach (MSB) – przełącznik PK4 ustawiony w pozycji PRZESUWANIE W LEWO. Kolejne

operacje przy porównywaniu dwu liczb 4-bitowych to zerowanie i taktowanie (max. 4

impulsy taktujące). KSz zmienia odpowiednio stan wyjść gdy będzie spełniony którykolwiek

iloczyn J1 J2 J3 = 1, czyli gdy Ai ≠ Bi i dzięki sprzężeniom międzyprzerzutnikami stan ten

będzie stabilny.

6.4.6. Komparator równoległy (KR):

Komparator równoległy jest 4-bitowym komparatorem iteracyjnym. Komparator ten

zbudowano odmiennie do opisanego w p. 6.2.7 modelu komparatora iteracyjnego.

Podstawowa komórka KR dokonuje porównań Ai > Bi, Ai < Bi, a jednobitowe przeniesienie

do następnego stopnia określa relację Ai = Bi. Członem wyjściowym są w tym przypadku

bramki NAND. Jeżeli na którymkolwiek stopniu komparatora iteracyjnego, poczynając od

stopnia dla MSB, wystąpi nierówność bitów Ai ≠ Bi to wygenerowanie przeniesienia

spowoduje blokadę wszystkich następnych stopni; jednocześnie sygnałem 0 sterowana jest

jedna z bramek wyjściowych NAND określająca relację większości.

6.5. Program ćwiczenia:

6.5.1. Badanie sumatora i subtraktora 1-bitowego:

Połączyć układ pomiarowy sumatora – subtraktora 1-bitowego wykorzystując

odpowiednie elementy rys. 6.24. Wcisnąć klawisz SSz przełącznika wyboru układu. Do

rejestrów A i B wpisać z zadajnika liczby A = 1100, B = 1010.

Przeanalizować działanie układu (stany wyjść Si (Di), Ci (Vi)) podając na wejście Ci-1 (Vi-1)

stan 0 a następnie stan 1. Na wejścia Ai i Bi sumatora / subtraktora dostarczana jest kolejno (z

rejestrów – TAKT) pełna kombinacja dwu bitów.

Rys. 6.24. Schemat pomiarowy dla : subtraktora-subtraktora 1 –bitowego, sumatorasubtraktora szeregowego i szeregowego sumatora akumulującego

6.5.2. Badanie sumatora - subtraktora szeregowego (SSz):

Na podstawie rys. 6.3 połączyć układ pomiarowy sumatora – subtraktora

szeregowego – patrz rys. 6.24. Sprawdzić działanie SSz wpisując do rejestrów A i B dowolne

4-bitowe liczby BIN. Wynika odczytać w rejestrze sumy S po odpowiedniej liczbie (5 lub 8)

impulsów taktujących (TAKT). Z kolei ustalając odpowiednie położenie przełącznika

SUMATOR/SUBTRAKTOR przeprowadzić następujące działania arytmetyczne: A + 0 = A,

A+B=8, A-0=A, A-B=0, A-B=S>0, A-B=S<0, 0-B = -B.

Przed wykonaniem każdego działania sumator szeregowy należy wyzerować.

6.5.3. Badanie szeregowego sumatora akumulującego (AkSSz):

Na podstawie rys. 6.5a połączyć układ pomiarowy szeregowego sumatora

akumulującego – patrz rys. 6.24. Wpisując do rejestru A kolejne 4-bitowe składniki

sumowania oraz ustalając odpowiednie położenie przełącznika SUMATOR –

SUBTRAKTOR przeprowadzić następujące działania: A+A+A = 3A, A1+A2+A3=S A1A2+A3=S>0, (A1>|A2|), A1+A2+...+An=S<29.

Szeregowy sumator akumulujący należy zerować przed każdą operacją

wielokrotnego sumowania. W przypadku AkSSz ulość impulsów taktujących (TAKT.) dla

każdego dodawania częściowego wynosi 8.

6.5.4. Badanie sumatora - subtraktora równoległego (SR):

Przy pomocy układu sumatora – subtraktora równoległego, przedstawionego na rys. 6.25,

przeprowadzić na liczbach BIN 4-bitowych następujące działania arytmetyczne: A+0=A,

A+B = S, A-B=S > 0, -A+B=S<0, -A-B=S, A-B=0, 0-B = -B

6.5.5. Badanie sumatora - subtraktora dziesiętnego (SD):

Sprawdzić działanie układu sumatora – subtraktora dziesiętnego (rys. 6.26) przez

wykonanie następujących obliczeń na dwu jednodekadowych liczbach BCD 8421. Dla układu

sumatora: A+0=A, A+B=S<10, A+B = S >10 z uwzględnieniem obu przypadków

podłączenia wejścia C-1, następnie zmieniając konfigurację na subtraktor (por. rys. 6.10b)

wykonać działania: A-B = S>0 (S<10), A-B = S<0 (|S| <10 ).

Rys. 6.26. Schemat pomiarowy sumatora-subtraktora BCD 8421

6.5.6. Badanie komparatora szeregowego (KSz):

Połączyć układ komparatora szeregowego zgodnie z rys. 6.27. Przeanalizować

kolejne kroki działania KSz wpisując do rejestrów A i B 4-bitowe liczby BIN o relacji A = B

oraz liczby o relacji A≠B, różniące się kolejno bitami od MSB do LSB.

Rys. 6.27. Schemat pomiarowy komparatora szeregowego

6.5.7. Badanie komparatora równoległego (KR):

Przy pomocy układu komparatora równoległego, przedstawionego na rys. 6.28,

sprawdzić otrzymane w punkcie 5.6.5 wyniki.

Rys.6.28. Schemat pomiarowy kompensatora równoległego

6.6. Tematy do opracowania:

6.6.1. Narysować tablice stanów sumatora i subtraktora 1-bitowego, porównać je z tablicami

6.1 i 6.2.

6.6.2. Na podstawie przykładów podanych w p. 6.2.1.2 [rzedstawić działania arytmetyczne

wykonane w p. 6.5.2, 6.5.1 i 6.5.4. W przypadku układu subtraktora szeregowego

zaznaczyć fakt otrzymania nieprawidłowego wyniku odejmowania jako niepełnego

uzupełnienia do 2 (por. wzór (6.5)). Podać sposób znalezienia prawidłowego wyniku.

6.6.3. Na podstawie przykładów podanych w p. 6.2.2.2. przedstawić działania arytmetyczne

wykonane przez układ sumatora – subtraktora dziesiętnego. W przypadku układu

subtraktora dziesiętnego zaznaczyć fakt otrzymania wyniku jako uzupełnienia do 9.

6.2.4. Dla układów komparatora szeregowego i równoległego wypełnić podaną niżej tablicę.

W przypadku komparatora szeregowego zaznaczyć numer taktu, w którym uzyskuje się

już poprawny wynik.

Tablica 6.

Analiza działania komparatora szeregowego i równoległego

6.7. Literatura:

1. Kalisz J.: Podstawy elektroniki cyfrowej, WKŁ , Warszawa 1998.

2. Lisiecka-Frąszczak J: Synteza układów cyfrowych, Wydawnictwa Politechniki

Poznańskiej , Poznań 2000.

3. Majewski W.: Układy logiczne, WNT, Warszawa 1976

4. Misiurewicz P, H. Grzybek: Półprzewodnikowe układy logiczne, WNT, Warszawa

1975, str. 83-177.

5. Pieńkos J, Turczyński J : Układy scalone TTL w systemach cyfrowych, WKŁ,

Warszawa 1980.

6. Traczyk W. :Układy cyfrowe. Podstawy teoretyczne i metody syntezy, WNT

Warszawa 1986.

7. Zieliński C. :Podstawy projektowania układów cyfrowych, PWN, Warszawa 2003.

8. Gryś S.: Arytmetyka komputerów – w praktyce, PWN, Warszawa, 2007.