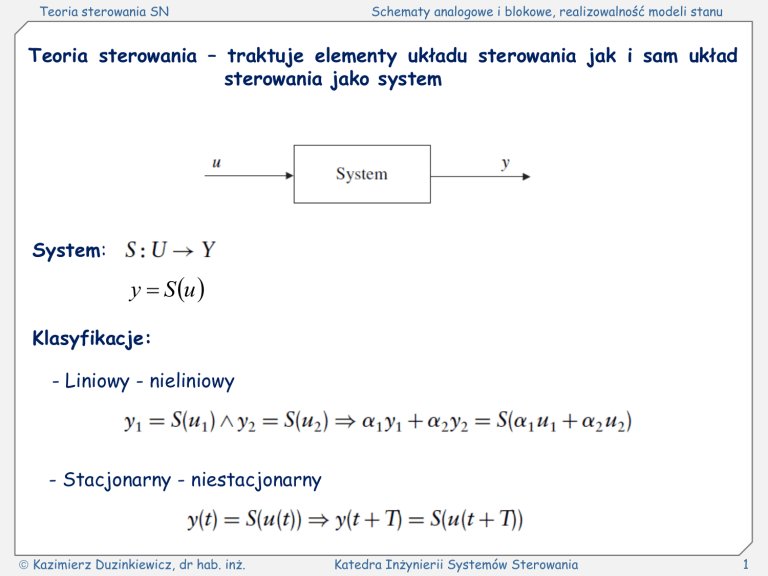

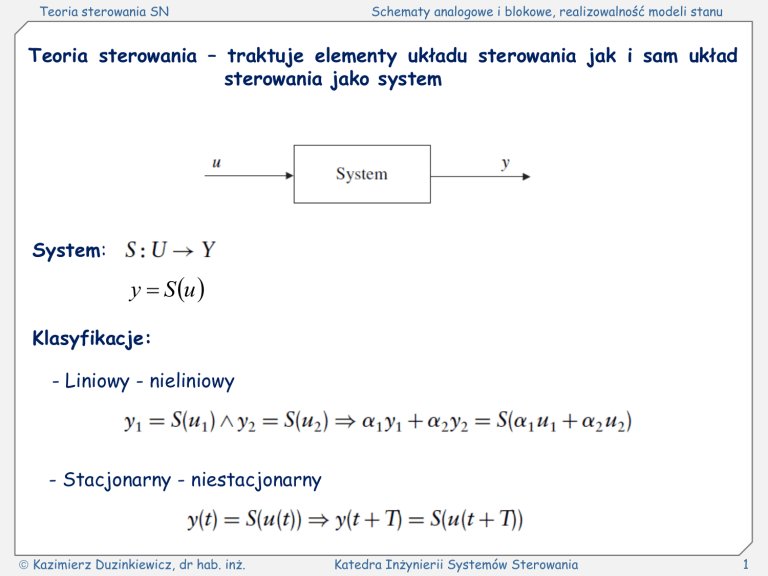

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Teoria sterowania – traktuje elementy układu sterowania jak i sam układ

sterowania jako system

System:

y S u

Klasyfikacje:

- Liniowy - nieliniowy

- Stacjonarny - niestacjonarny

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

1

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Klasyfikacje: c.d.

- Jednowymiarowy (SISO) – wielowymiarowy (MIMO)

Klasyfikacja w odniesieniu do liczby zmiennych wejścia - wyjścia

- Czasu ciągłego – czasu dyskretnego

Klasyfikacja w odniesieniu charakteru sygnałów wejścia i wyjścia

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

2

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Wybrane elementy wprowadzenia do teorii

sterowania

Systemy liniowe, stacjonarne,

ze sprzężeniem zwrotnym

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

3

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Jak możemy traktować modele obiektów dynamicznych?

Przedstawiają one prawo przetwarzania sygnału wejściowego obiektu u(t) w sygnał

wyjściowy obiektu y(t) bezpośrednio lub z wykorzystaniem zmiennych stanu x(t)

Prawo to umożliwia dla danego kształtu u(t) i znanych odpowiednich wartości

początkowych określić kształt y(t)

Czy to trudne zadanie? Dla układów liniowych ze stałymi współczynnikami – nie

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

4

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Rozważamy najpierw równanie modelu wejście – wyjście w którym nie występują

pochodne sygnału wejścia

dny

d n 1 y

dy

an n an 1 n 1 a1

a0 y u t

dt

dt

dt

(1)

z warunkami początkowymi:

y0 y0 , y 0 y0 , , y n 1 0 y0 n 1

(2)

Czy potrafilibyśmy zbudować urządzenie, które rozwiązywałoby takie równanie?

Schematy analogowe

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

5

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Taką samą strukturę mają poszczególne równania stanu w modelu stanu

dxi

i A x i B u 0

dt

(3)

lub:

dxi

ai 1 x1 aii xi ain xn bi 1u1 b ip u p 0

dt

z warunkiem początkowym:

xi 0 xi ,0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

(4)

6

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Czy potrafimy zbudować sumator (układ elektroniczny)?

Uf

R1

Uwe1

if

i1

Uwe2

R2

ig

i2

Uwe2

Rf

i 1

Ri

uwy t

Rf

eg - K

+

n

Uwy

u1(t)

u2(t)

un(t)

uwe ,i t

k1

y(t)

k2

...

Uwe1

kn

n

y t ki ui t

i 1

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

7

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Czy potrafimy zbudować integrator (układ elektroniczny)?

uf

uwe

R

uwe

if

iwe ig

eg

Cf

-

-K

Rwe, Rwy

+

1

uwy t

RC f

t

u

we

d uwy 0

0

uwy

y0

u(t)

y(t)

k

t

yt u d y0

0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

8

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dla równania modelu wejście – wyjście

Zapiszmy:

an 1 d n 1 y

dny 1

a1 dy a0

u

t

y

n

n 1

dt

an

an dt

an dt an

(1a)

oraz warunki początkowe:

y0 y0 , y 0 y0 , , y n 1 0 y0 n 1

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

(2a)

9

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

- uzyskiwanie pochodnych niższych rzędów – idea całkowania równania

y(n-1) (t)

(n)

y (t)

- zadawanie warunków

początkowych

y(n-2) (t)

.

y(t)

y (t)

- uzyskiwanie najwyższej pochodnej

u(t)

1

an

k

y0

u(k)(t)

y k 1 t

y· (t)

y(n-1) (t)

Kazimierz Duzinkiewicz, dr hab. inż.

a0

an

y(n)(t)

a1

an

...

y(t)

a n 1

an

Katedra Inżynierii Systemów Sterowania

10

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

u (t)

y(t)

y0 n2

y0

a0

an

a

1

an

y(n)(t)

y(n-1) (t)

y(n-2) (t)

.

y(t)

y (t)

...

y· (t)

y0 n1

1

an

y(n-1) (t)

a n 1

an

Schemat analogowy rozwiązywania równania różniczkowego

dny

d n 1 y

dy

an n an 1 n 1 a1

a0 y u t

dt

dt

dt

(1)

z warunkami początkowymi:

y0 y0 , y 0 y0 , , y n 1 0 y0 n 1

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

(2)

11

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dla równania stanu modelu przestrzeni stanu

Zapiszmy:

dxi

ai 1 x1 aii xi ain xn bi 1u1 b ip u p

dt

(3a)

oraz warunek początkowy:

xi 0 xi ,0

Kazimierz Duzinkiewicz, dr hab. inż.

(4a)

Katedra Inżynierii Systemów Sterowania

12

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

A jeżeli występują pochodne sygnału wejścia?

Przykład

Równanie:

d 3 yt

d 2 yt

dyt

d 2u t

du t

3

.

5

3

.

5

y

t

1

.

2

0.35u t

3

2

2

dt

dt

dt

dt

dt

Warunki początkowe

d 2 y0

dy0

du 0

0

.

8

,

0

.

2

,

y

0

0

.

1

;

0.7 ,u 0 1.0

2

dt

dt

dt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

13

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zapiszmy równanie:

d 3 y d 2u

d2y

du

dy

3

.

5

1

.

2

3

.

5

0.35u y

3

2

2

dt

dt

dt

dt

dt

Scałkujmy je jednokrotnie:

t

d 2 y du

dy

3.5 1.2u 3.5 y 0.35u y d C2

2

dt

dt

dt

0

C2 wyznaczymy kładąc t=0 i korzystając z warunków początkowych

d 2 y 0 du 0

dy 0

C2

3

.

5

1.2u 0 3.5 y 0

2

dt

dt

dt

0.8 0.7 3.5 0.2 1.2 1.0 3.5 0.1

0.8 0.0 0.85 0.05

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

14

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Powtórzmy operację całkowania:

t

t t

dy

u 3.5 y 1.2u 3.5 y d 0.35u y d C1

dt

0

0 0

C1 wyznaczymy kładąc t=0 i korzystając z warunków początkowych

dy 0

C1

u 0 3.5 y 0 0.2 1.0 3.5 0.1

dt

0.2 0.65 0.45

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

15

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Wykonajmy operacje całkowania po raz trzeci

t

t t

t t t

0

0 0

0 0 0

yt u 3.5 y d 1.2u 3.5 y d 0.35u y d C0

C0 wyznaczymy kładąc t=0 i korzystając z warunków początkowych

C0 y0 0.1

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

16

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

d 3 y d 2u

d2y

du

dy

2 3.5 2 1.2 3.5 0.35u y

3

dt

dt

dt

dt

dt

t

t t

t t t

0

0 0

0 0 0

yt u 3.5 y d 1.2u 3.5 y d 0.35u y d C0

u (t)

C1

C2

0.35

1.2

C0

1.0

y (t)

Poznaliśmy metodę

kolejnych całkowań

– metodę postaci

kanonicznej

Kazimierz Duzinkiewicz, dr hab. inż.

-1.0

-3.5

-3.5

Katedra Inżynierii Systemów Sterowania

17

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Jeżeli występują pochodne sygnału wejścia a warunki początkowe są

zerowe dogodniejsza jest metoda zmiennej pomocniczej

Przykład

Równanie:

d 2 yt

dy

du t

3

2

y

t

2

u t

2

dt

dt

dt

Warunki początkowe

dy 0

0 , y 0 0; u 0 0

dt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

18

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Transformacja Laplace’a i transmitancja operatorowa

Rozważaliśmy dotychczas w dziedzinie czasu zachowanie się obiektu

dynamicznego w przedziale czasu od t0 do t opisywanego równaniem

różniczkowym

Przykład 1 – czwórnik RC

R

t=0

uR(t)

uwe(t)

duwy t

dt

Przykład 2 – dwójnik RL

iobc(t)

iR(t)

iC(t)

uC(t)

C

uwy(t)

z warunkiem początkowym:

u wy 0 uC 0 uC 0

iR(t)

uR(t)

uwe(t)

1

1

uwy t

uwe t

R C

R C

Kazimierz Duzinkiewicz, dr hab. inż.

R

t=0

uL(t)

iL(t)

L

diL t

R

1

iL t u we t

dt

L

L

z warunkiem początkowym:

iL 0 iL0

Katedra Inżynierii Systemów Sterowania

19

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Ogólna struktura:

dy

a yt b u t (1a)

dt

(1b)

yt0 y0

u(t)

Obiekt

y(t)

Dla dowolnego wejścia u(t) określonego w przedziale [t0,t] pełna odpowiedź

obiektu

t

yt y0e a t t0 u b e a t d

t0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

20

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dokonamy przejścia do dziedziny zmiennej zespolonej s

Załóżmy, że zarówno funkcja (reprezentacja matematyczna sygnału) u(t) –

wejście, jak i y(t) – wyjście, spełnia warunki pozwalające poddać je

przekształceniu Laplace’a

U s Lut

Y s Lyt

Pamiętać powinniśmy o warunkach jakie muszą spełniać funkcje f(t)

(funkcje czasu) poddawane transformacji Laplace’a

Transformację Laplace’a możemy stosować do systemów liniowych (czyli

spełniających zasadę superpozycji) i stacjonarnych (czyli spełniających

zasadę niezmienniczości w czasie)

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

21

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Funkcja f(t) musi spełniać

f t 0 dla t 0

(L1)

Całka

F s f t e st dt

musi istnieć (być zbieżna)

(L2)

0

Poddając transformacji Laplace’a obydwie strony (1a) i uwzględniając

znajomość (1b) otrzymamy

sY s y0 a Y s

d

L y t

dt

Kazimierz Duzinkiewicz, dr hab. inż.

La yt

bU s

(2)

Lb ut

Katedra Inżynierii Systemów Sterowania

22

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

sY s y0 a Y s bU s

Rozwiązując (2) ze względu na Y(s)

s aY s y0 bU s

Y s

1

b

y0

U s

s a

s a

Składowa

swobodna

odpowiedzi

Składowa

wymuszona

odpowiedzi

Składowa swobodna:

y 0

yZI t L1 Y s u t 0 L1

s a

Składowa wymuszona:

yZS t L Y s y 0 0

1

Kazimierz Duzinkiewicz, dr hab. inż.

b

L

U s

s a

1

Katedra Inżynierii Systemów Sterowania

23

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Transformata Laplace’a składowej wymuszonej:

YZS s

b

U s G s U s

s a

G s

Y s

b

ZS

s a U s

gdzie,

- Transmitancja operatorowa

obiektu dynamicznego

I definicja transmitancji obiektu dynamicznego

Transmitancją operatorowa obiektu dynamicznego (liniowego, stacjonarnego)

nazywamy stosunek transformaty Laplace’a składowej wymuszonej odpowiedzi

tego obiektu na wymuszenie do transformaty Laplace’a tego wymuszenia

lub inaczej:

Transmitancją operatorowa obiektu dynamicznego (liniowego, stacjonarnego)

nazywamy stosunek transformaty Laplace’a odpowiedzi tego obiektu na

wymuszenie uzyskanej przy zerowym warunku początkowym, do transformaty

Laplace’a tego wymuszenia

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

24

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Transmitancja obiektu dynamicznego – na przykładzie obiektu rzędu

pierwszego, np. czwórnika RC, dwójnika RL

YZS s

b

G s

s a U s

Właściwości:

(i) G(s) – wzmocnienie dynamiczne obiektu w dziedzinie s

(ii) G(s) – nie ma stałej wartości, lecz jest funkcją zmiennej s

(iii) G(s) – nie zależy od sygnału wejściowego – jest zatem

charakterystyką obiektu

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

25

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Transmitancja obiektu opisuje dynamikę obiektu w dziedzinie

zmiennej zespolonej s

Odpowiedź impulsowa obiektu opisuje dynamikę obiektu w

dziedzinie czasu t

Związek pomiędzy nimi?

YZS s Gs U s

Transformata Laplace’a impulsu jednostkowego:

ut t Lut U s 1

YZS s u t t G s L t G s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

26

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Otrzymaliśmy:

g t L1Gs lub

Składowa

wymuszona

odpowiedzi na

impuls jednostkowy

Gs Lg t

Transmitancja

obiektu

dynamicznego

II definicja transmitancji obiektu dynamicznego

Transmitancją operatorowa obiektu dynamicznego (liniowego,

stacjonarnego)

nazywamy transformatę Laplace’a składowej

wymuszonej odpowiedzi tego obiektu na wymuszenie impulsem

jednostkowym

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

27

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

W rozważanym przykładzie – obiekt pierwszego rzędu

yZS t b S e a t t0 - odpowiedź dla ut t t0 i intensywności S

Dla t0 = 0 i S = 1:

yZS t b e at

Otrzymamy:

L b e at

b

sa

Kazimierz Duzinkiewicz, dr hab. inż.

(porównać z wynikami z poprzednich slajdów)

Katedra Inżynierii Systemów Sterowania

28

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Przykład 1 – czwórnik RC

R

t=0

uR(t)

uwe(t)

iobc(t)

iR(t)

iC(t)

uC(t)

C

uwy(t)

duC

1

1

uC t

uwe t

dt

RC

RC

uC t0 0

Kazimierz Duzinkiewicz, dr hab. inż.

1

1

sU C s

U C s

U we s

RC

RC

1

U s

1

RC

G s C

U we s

1 1 RCs

s

RC

Katedra Inżynierii Systemów Sterowania

29

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Przykład 2 – dwójnik RL

R

t=0

uR(t)

uwe(t)

iR(t)

uL(t)

iL(t)

L

diL t

R

1

iL t u we t

dt

L

L

iL 0 0

Kazimierz Duzinkiewicz, dr hab. inż.

R

1

sI L s I L s U we s

L

L

1

1

I s

L

G s L

R

U we s

R 1 L s

s

R

L

Katedra Inżynierii Systemów Sterowania

30

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Odpowiedź wymuszona na sygnał skokowy o amplitudzie U

ut

u t U 1t t0

U

0

LU 1t t0

U t 0 s

e

s

t

s

t0

dla t0 =0:

LU 1t

U

s

Odpowiedź wymuszona w dziedzinie s:

b U t 0 s

YZS s Gs U s

e

sa s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

31

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Odpowiedź wymuszona w dziedzinie t:

b U t 0 s

1

t0 s

1

yZS t L YZS s L

e bU L

e

s a s

ss a

1

1

Zastosujemy dla znalezienia L-1 metodę rozkładu na ułamki proste:

1

B

1 A

L

L

s

s

a

s

s

a

1

1

A B 0 A a

As a Bs 1 A B s Aa 1

1

Aa 1

B A

a

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

32

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Stąd:

1

1 1 1 1 t 0 s

t0 s

1

e bU L

y ZS t bU L

e

a s a s a

s s a

1

1 t0 s b

1

b

a t t 0

1

e

t

t

1

U

e

U L

0

a

a

s s a

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

33

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Parametry transmitancji obiektu rzędu pierwszego inercyjnego

b

yZS t U 1t t0 e a t t0

a

yZS t

b

U

a

dla rozważanego przykładu

t

0

Wielkość

t0

y ZS t ustalona wartosc

b

K

u t ustalona wartosc

a

nazywamy statycznym współczynnikiem wzmocnienia

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

34

Teoria sterowania SN

Przykład 1 – czwórnik RC

1

b

K RC 1

1

a

RC

Kazimierz Duzinkiewicz, dr hab. inż.

Schematy analogowe i blokowe, realizowalność modeli stanu

Przykład 2 – dwójnik RL

1

b

1

L

K

R

a

R

L

Katedra Inżynierii Systemów Sterowania

35

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Określanie wzmocnienia statycznego – wykorzystanie transmitancji

ut

yt

Obiekt

ut

yt

A

yust

t

0

yust

K

A

Kazimierz Duzinkiewicz, dr hab. inż.

0

t

- wzmocnienie statyczne

Katedra Inżynierii Systemów Sterowania

36

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Określanie wzmocnienia statycznego – wykorzystanie transmitancji

ut

yt

Obiekt

ut

yt

A

yust

t

0

yust

K

A

Kazimierz Duzinkiewicz, dr hab. inż.

0

t

- wzmocnienie statyczne

Katedra Inżynierii Systemów Sterowania

37

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

oraz

K

yust

lim G s

s 0

A

Przykład 3

Wyznaczyć wzmocnienie statyczne obiektu o transmitancji

s 4 3s 2 s 5

G s 10

s 12s 6 6s 3 2

W dziedzinie czasu opis równaniem różniczkowym:

Y s s 4 3s 2 s 5

Gs

U s s10 12s 6 6s 3 2

Y s s10 12Y s s 6 6Y s s 3 2Y s U s s 4 3U s s 2 U s s 5U s

d 10 yt

d 6 yt

dy 3 t

d 4u t

d 2u t du t

12

6

2 yt

3

5u t

10

6

3

4

2

dt

dt

dt

dt

dt

dt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

38

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

W dziedzinie czasu należałoby teraz rozwiązać równanie różniczkowe

dla wymuszenia

ut A 1t

Mając y(t) należałoby obliczyć

lim y t

t

i ostatecznie wyznaczyć K

Korzystając z transmitancji:

s 4 3s 2 s 5

5

K lim Gs lim 10

s 0

s 0 s 12 s 6 6 s 3 2

2

Dla np. A = 3 odpowiedź ustalona:

yust K A

Kazimierz Duzinkiewicz, dr hab. inż.

5

15

3

2

2

Katedra Inżynierii Systemów Sterowania

39

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

W dziedzinie czasu należałoby teraz rozwiązać równanie różniczkowe

dla wymuszenia

ut A 1t

Mając y(t) należałoby obliczyć

lim y t

t

i ostatecznie wyznaczyć K

Korzystając z transmitancji:

s 4 3s 2 s 5

5

K lim Gs lim 10

s 0

s 0 s 12 s 6 6 s 3 2

2

Dla np. A = 3 odpowiedź ustalona:

yust K A

Kazimierz Duzinkiewicz, dr hab. inż.

5

15

3

2

2

Katedra Inżynierii Systemów Sterowania

40

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Przedstawmy odpowiedź wymuszoną:

b

yZS t U 1t t0 e a t t0

a

b

yZS t U 1 e a t t0 ; t t0

a

dla rozważanego przykładu

yZS t

1

T

Wielkość

a

b

U

a

1

T - nazywamy stałą

a czasową bezwładności

(inercji)

0

Policzmy:

t

t0

d

b

yZS t U a e a t t0 t t0

dt

a

t t 0

Kazimierz Duzinkiewicz, dr hab. inż.

b

U

bU a tg

1

a

Katedra Inżynierii Systemów Sterowania

41

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Podsumowanie:

W automatyce wyróżniamy pewne tzw. człony elementarne liniowe i

stacjonarne, stanowiące części obiektu sterowanego lub układu

sterującego charakteryzujące się określoną transmitancją

operatorową

Poznaliśmy już jeden z takich członów:

Przykład 1 – czwórnik RC

R

t=0

uR(t)

uwe(t)

Przykład 2 – dwójnik RL

iobc(t)

iR(t)

iC(t)

uC(t)

C

U s

1

G s C

U we s 1 RCs

Kazimierz Duzinkiewicz, dr hab. inż.

R

t=0

uwy(t)

uR(t)

uwe(t)

iR(t)

uL(t)

1

I s

G s L

R

U we s 1 L s

R

Katedra Inżynierii Systemów Sterowania

iL(t)

L

42

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Standardowa postać transmitancji tych układów:

G s

Y s

K

U s 1 Tb s

Parametry:

K

- współczynnik wzmocnienia statycznego

Tb - stała czasowa bezwładności

Nazwa członu:

Człon inercyjny pierwszego rzędu

Inne człony poznamy w dalszej części wykładu i podczas ćwiczeń !

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

43

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Wróćmy do tematu schematów analogowych

Równanie poddajemy obustronnie transformacji Laplace’a:

s

2

3s 2 Y s 2s 1U s

Wprowadzamy zmienną pomocniczą spełniającą równanie:

s

Wówczas:

s

2

2

3s 2 YP s U s

3s 2 Y s 2s 1 s 2 3s 2 YP s

Zamiast pierwotnego równania modelujemy dwa równania:

s

2

3s 2 YP s U s

Y s 2s 1YP s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

44

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

W dziedzinie czasu dwa modelowane równania:

d 2 yp

dt

2

3

2

dy p

dt

dy p

dt

2 yp u

- równanie zmiennej pomocniczej

yp y

- równanie wyjścia

Zróżniczkujemy równanie wyjścia:

dy 2p

dy p

dy

2 2

dt

dt

dt

d 2 y p 0

Dla t=0 otrzymamy:

dt

2

3

dy p 0

2

2

Kazimierz Duzinkiewicz, dr hab. inż.

dy 2p 0

dt 2

2 y p 0 u 0

dt

dy p 0

dt

dy p 0

dt

y p 0 y0

Katedra Inżynierii Systemów Sterowania

dy 0

dt

45

Teoria sterowania SN

d 2 yp

dt

2

3

2

dy p

dt

dy p

dt

Schematy analogowe i blokowe, realizowalność modeli stanu

2 yp u

- równanie zmiennej pomocniczej

yp y

- równanie wyjścia

0.0

u (t)

0.0

1.0

2.0

y (t)

-2.0

-3.0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

46

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Przykład modelu silnika prądu stałego obcowzbudnego

Spróbujemy najpierw zbudować schemat blokowy dla modelu

nieliniowego stacjonarnego rozważanego silnika

d t

J

Giw t it t D t M oz t

dt

diw t

Lw

u w t Rwiw t

dt

dit t

Lt

ut t Rt it t Giw t t

dt

Poszukujemy zachowania się rozważanego systemu w przedziale

czasu [0,t), dla warunków początkowych

0 0 , iw 0 iw0 it 0 it 0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

47

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy pierwsze równanie

d t

J

Giw t it t D t M oz t

dt

i w t

it t

M oz t

Kazimierz Duzinkiewicz, dr hab. inż.

0 0

0 0

Transformacja

sygnałów w części

mechanicznej

systemu

t

Katedra Inżynierii Systemów Sterowania

48

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Podstawowy element: całkowanie funkcji w przedziale [0,t] z warunkiem

początkowym

iW E 0

iW E

iW E

Transformację sygnałów w części mechanicznej możemy przedstawić:

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

49

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

d t 1

Giw t it t D t M oz t

dt

J

0 0

0 0

iw t

it t

G

M oz t

- -

1 t

J

t

D

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

50

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy drugie równanie

diw t 1

uw t Rwiw t

dt

Lw

i w 0 iw 0

i w 0 iw 0

uw t

Transformacja

sygnałów w części

elektrycznej –

obwód wzbudzenia

systemu

uw t

iw t

i w 0 iw 0

-

1 iw t

Lw

iw t

Rw

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

51

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy trzecie równanie

dit t 1

ut t Rt it t Giw t t

dt

Lt

it 0 it 0

u t t

iw t

t

Kazimierz Duzinkiewicz, dr hab. inż.

it 0 it 0

Transformacja

sygnałów w części

elektrycznej –

obwód twornika

systemu

it t

Katedra Inżynierii Systemów Sterowania

52

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

dit t 1

ut t Rt it t Giw t t

dt

Lt

it 0 it 0

it 0 it 0

iw t

t

G

ut t

-

-

1

Lt

itt

it t

Rt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

53

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zestawimy schemat całego modelu

i w 0 iw 0

uw t

-

iw t

iw t

1 iw t

Lw

Rw

it 0 it 0

ut t

iw t

t

-

-

G

it t

it t

1 itt

Lt

Rt

0 0

M oz t

iw t

it t

Kazimierz Duzinkiewicz, dr hab. inż.

G

-

1

J

t

t

t

D

Katedra Inżynierii Systemów Sterowania

54

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Silnik – obiekt/system sterowany

Cel sterowania – np. utrzymanie określonej prędkości kątowej silnika,

określonej wcześniej: stałej – sterowanie stałowartościowe, zmiennej w

czasie – sterowanie programowe, nie znanej wcześniej, podawanej na

bieżąco – sterowanie nadążne

Wielkości wyjściowe obiektu

Wielkość sterowana – należy do jednej z klas wielkości wyjściowych

obiektu sterowanego

Przyjmijmy: wielkość sterowana – prędkość kątowa silnika

Pozostałe obserwowane wielkości wyjściowe – wielkości pomocnicze

Zatem: wielkości pomocnicze – prąd wzbudzenia, prąd twornika

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

55

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Silnik – obiekt/system sterowany – c.d.

Wielkości wejściowe obiektu

Poszukiwanie wielkości sterującej; jakie wielkości wejściowe wpływają na

prędkość kątową silnika

Moment oporowy zewnętrzny – wielkość zakłócająca

Napięcie twornika, napięcie wzbudzenia? – kandydaci na wielkość

sterującą

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

56

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Graficzna reprezentacja systemów dynamicznych –

schematy blokowe

Poglądowym narzędziem przedstawiania systemów dynamicznych są

schematy blokowe – dotyczy to szczególnie systemów stacjonarnych,

zarówno liniowych jak i nieliniowych

Schemat

blokowy

obrazuje

informacji/sygnałów w systemie

przepływ

i

transformacje

Budowa schematu blokowego korzysta z kilku symboli podstawowych,

a zbudowany schemat może być narzędziem pomocniczym w analizie

systemu

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

57

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Graficzna reprezentacja systemów dynamicznych –

schematy blokowe

Symbole podstawowe:

iWE

Opis sposobu

przetwarzania

iWY

iP

Element systemu: przetwarzanie

informacji wejściowej w informację

wyjściową

Droga przesyłania informacji

iP

iP

iP

Kazimierz Duzinkiewicz, dr hab. inż.

Węzeł zaczepowy: rozsyłanie tej

samej informacji do różnych

elementów systemu lub do

otoczenia

Katedra Inżynierii Systemów Sterowania

58

Teoria sterowania SN

iA

Schematy analogowe i blokowe, realizowalność modeli stanu

iC

-

iB

Węzeł sumacyjny: sumowanie

algebraiczne sygnałów dochodzących z

różnych elementów systemu lub z

otoczenia

iC i A iB

iA

iC

-

Węzeł mnożący: mnożenie algebraiczne

sygnałów dochodzących z różnych

elementów systemu lub z otoczenia

iB

iC iA iB iAiB

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

59

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Technologię budowania schematu blokowego pokażemy na kilku

przykładach

Opis sposobu przetwarzania użyty w symbolu

elementu systemu może mieć różny charakter

charakterystyka statyczna – dla elementu

statycznego nieliniowego

Opis sposobu

WE przetwarzania

i

iWY

transmitancja operatorowa lub widmowa –

dla elementu dynamicznego liniowego

stacjonarnego

szkicowa charakterystyka skokowa lub

impulsowa – dla elementu dynamicznego

liniowego stacjonarnego

Kazimierz Duzinkiewicz, dr hab. inż.

szkicowa charakterystyka częstotli wościowa – dla elementu dynamicznego

liniowego stacjonarnego

Katedra Inżynierii Systemów Sterowania

60

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zadania – budowanie schematu blokowego w oparciu o zależności opisu

systemu sterowania

Zadanie 1: Działanie systemu sterowania opisane jest następującymi

zależnościami:

x3 K 3 x 2

x1 u x3

x2 K 1 x1

x4 K 4 x 2

y x4 x5

x5 K 2 x 2

Narysuj schemat blokowy tego układu sterowania

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

61

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Rozwiązanie

u

x1 u x3

x1

-

x3

x2 K1 x1

x3 K 3 x 2

x4 K 4 x 2

x5 K 2 x 2

Kazimierz Duzinkiewicz, dr hab. inż.

x1

x2

K1

x 2x

x2

2

x2

Katedra Inżynierii Systemów Sterowania

62

Teoria sterowania SN

x3 K 3 x2

Schematy analogowe i blokowe, realizowalność modeli stanu

x3

x4 K 4 x 2

x2

x5 K 2 x 2

x2

K3

x2

K4

x4

K2

x5

x5

y x4 x5

Kazimierz Duzinkiewicz, dr hab. inż.

x4

-

y

Katedra Inżynierii Systemów Sterowania

63

Teoria sterowania SN

u

-

x1

Schematy analogowe i blokowe, realizowalność modeli stanu

K1

x2

x 2x

2

K2

x5

K4

x4

x2

x3

y

K3

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

64

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zadanie: Utrzymać napięcie zasilania odbiorników w sieci prądu stałego na

stałym, zadanym poziomie Uo=24V

Wielkości zakłócające

Zaproponowane rozwiązanie

ωm

Φk

Φw

Iw

E

Rz

Ik

U

Io

K5 Uε Uo

Wielkość sterująca

-

Obiekt sterowany

Wielkość sterowana

Układ sterujący

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

65

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zależności

U E Rz I o

E K 1 m

W K

W K 2 I w , K K 4 I k

I k K5U

U U o U

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

66

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dostępna wiedza o

obiekcie sterowanym

Wielkości

zakłócające

Wartość

pożądana

wielkości

sterowanej

U0

W przykładzie

E I w , I k U ,U o

Kazimierz Duzinkiewicz, dr hab. inż.

I o ,m

System

sterowany

System

sterujący

W przykładzie

W przykładzie:

Wielkość

sterująca

Wielkość

sterowana

W przykładzie

U

Układ zamknięty sterowania

(ze sprzężeniem zwrotnym)

Katedra Inżynierii Systemów Sterowania

67

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Przykład – sterowanie napięciem zasilania –schemat blokowy

Symbole z falką - zmienne

Opis działania:

Schemat blokowy:

~

Iz

~ ~

~

U E RI z

R

~

E

~

~

~

E K1m

Kazimierz Duzinkiewicz, dr hab. inż.

~

- U~

~m

K1

~

E

Katedra Inżynierii Systemów Sterowania

68

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

~

~

~

~

w

w k

~

w K2 I w

~

~

k K5 I k

~

Kazimierz Duzinkiewicz, dr hab. inż.

~

+

~

k

~

Iw

~

K2

~

k

K5

w

~

Ik

Katedra Inżynierii Systemów Sterowania

69

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Schemat blokowy systemu sterowanego - prądnicy

~

Iz

~m

~

Iw

R

~

K2

w

~

+

K1

~

E

~

k

~

Iw

~

Ik

Kazimierz Duzinkiewicz, dr hab. inż.

~ ~ ~

~

U f 1 m , I z , I w , I k

~

U

~

Ik

K5

~m

~

Iz

-

~

U

Katedra Inżynierii Systemów Sterowania

70

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Opis działania systemu sterowanego - prądnicy

~ ~

~

U E RI z

~

~~

E K 1 m

~ ~

~

w k

~

~

w K2Iw

~

~

k K5Ik

(1)

(2)

(3)

(4)

(5)

Podstawiając kolejno (2) – (5) do (1) otrzymamy opis

zależności wejście – wyjście prądnicy

~

~

~

~

~

~

U K1 K 2m I w K1 K5m I k RI z

(6)

Opis działania prądnicy nieliniowy

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

71

Teoria sterowania SN

Jeżeli

~

Iw

Schematy analogowe i blokowe, realizowalność modeli stanu

~m

~m m const

~

stałe, czyli

Iz

R

~

K2

w

~

+

K

1 m

~

E

~

k

~

Ik

K5

~

Iz

~

Iw

~

Ik

Kazimierz Duzinkiewicz, dr hab. inż.

~ ~ ~

U f2 I z ,I w ,Ik

~

U

~

U

Katedra Inżynierii Systemów Sterowania

72

Teoria sterowania SN

~ ~

~

U E RI z

~

~

E K 1 m

~ ~

~

w k

~

~

w K2Iw

~

~

k K5Ik

Schematy analogowe i blokowe, realizowalność modeli stanu

(1)

(2a)

(3)

(4)

(5)

~

~

~

~

U K1 K 2m I w K1 K5m I k RI z

(6a)

Opis działania liniowy

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

73

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

~m var

~

Iz

Schemat blokowy systemu sterowania

~m

~

Iw

R

~

K2

w

~

+

K1

~

E

~

k

~

Ik

K5

~

~ ~

U U0 U

~

U

~

~ U0

U

Kazimierz Duzinkiewicz, dr hab. inż.

~

U

~

~

I k K 4U

~

Ik

+

Katedra Inżynierii Systemów Sterowania

K4

~

U

74

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Schemat blokowy systemu sterowania

~m

~

Iw

R

~

K2

w

~

+

~

k

~

Ik

K5

~m

~

Iz

~

Iw

~

U0

Kazimierz Duzinkiewicz, dr hab. inż.

~m var

~

Iz

~

E

K1

~ ~

~ ,~

U f3

I

,

m

z I w ,U 0

~ U

K4

~

U

-

~

U

+

~

U0

~

U

Katedra Inżynierii Systemów Sterowania

75

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Opis działania

~

~

~

~

~

~

U K1 K 2m I w K1 K5m I k RI z

~

~ ~

U U0 U

~

~

I k K 4U

(6)

(7)

(8)

Podstawiając kolejno (7) – (8) do (6) otrzymamy opis zależności

wejście – wyjście systemu sterowania

~

~

~

~

K 1 K 2 m I w

K 1 K 5 K 4 mU 0

~

U

~

~

1 K 1 K 5 K 4 m 1 K 1 K 5 K 4

m

(9)

~

RI z

~

1 K 1 K 5 K 4

m

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

76

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Schemat blokowy systemu sterowania

~

Iw

R

~

K2

~m m const

~

Iz

~

w

+

K

1 m

~

E

~

k

~

Ik

K5

~

~ ~

U U0 U

~

~ - U U~

U

0

Kazimierz Duzinkiewicz, dr hab. inż.

~

~

I k K 4U

~

U

~

Ik

+

Katedra Inżynierii Systemów Sterowania

K4

~

U

77

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Schemat blokowy systemu sterowania

~

Iw

R

~

K2

w

~m m ~ const

Iz

~

E

~

+

K

1 m

~

k

K5

~

Ik

K4

~

Iz

~

Iw

~

U0

Kazimierz Duzinkiewicz, dr hab. inż.

~ ~ ~

U f 4 I z , I w ,U 0

~

U

~

~ - U U~

U

0

+

~

U

Katedra Inżynierii Systemów Sterowania

78

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Opis działania

~

~

~

~

U K1 K 2m I w K1 K5m I k RI z

~

~ ~

U U0 U

~

~

I k K 4U

(6a)

(7)

(8)

Podstawiając kolejno (7) – (8) do (6a) otrzymamy opis zależności

wejście – wyjście systemu sterowania

~

~

K 1 K 2 m I w

K 1 K 5 K 4 mU 0

~

U

1 K 1 K 5 K 4 m 1 K 1 K 5 K 4 m

(9a)

~

RI z

1 K 1 K 5 K 4 m

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

79

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Rozważymy teraz model zlinearyzowany silnika PS i wybierzemy opis za

pomocą transmitancji operatorowej – zbudujemy schemat blokowy

transmitancyjny

d t

Giw0 it t Git 0 iw t D t M oz t

dt

diw t

Lw

u w t Rw iw t

dt

dit t

Lt

ut t Rt it t Giw0 t G0 iw t

dt

J

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

80

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Powracamy do przykładu z silnikiem PS

Niech

L t s

Lit t I t s

Liw t I w s

LM oz t M oz s

Lut t U t s

Lu w t U w s

Poddamy transformacji Laplace’a każde z równań, przy zerowych

warunkach początkowych

Warto pamiętać, że

Linearyzacja w otoczeniu punktu równowagi gwarantuje zerowe warunki

początkowe

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

81

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy pierwsze równanie i poddajmy je transformacji Laplace’a

d t

J

Giw0 it t Git 0 iw t D t M oz t

dt

Otrzymamy

Js s Giw0 I t s Git 0 I w s D s M oz s

D Js s Giw0 I t s Git 0 I w s M oz s

1

Giw0 I t s Git 0 I w s M oz s

D Js

1

s D Giw0 I t s Git 0 I w s M oz s

J

1 s

D

s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

82

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

1

s D Giw0 I t s Git 0 I w s M oz s

J

1 s

D

I t s

Gi w 0

I w s

Gi t 0

-

1

D

J

1 s

D

s

M oz s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

83

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy drugie równanie i poddajmy je transformacji Laplace’a

diw t

Lw

u w t Rw iw t

dt

Otrzymamy

Lw sI w s U w s Rw I w s

1

I w s

U w s

Rw Lw s

1

Rw

I w s

U w s

Lw

1

s

Rw

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

84

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

1

Rw

I w s

U w s

Lw

1

s

Rw

U w s

Kazimierz Duzinkiewicz, dr hab. inż.

1

Rw

L

1 w s

Rw

I w s

Katedra Inżynierii Systemów Sterowania

85

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy w końcu trzecie równanie modelu i poddajmy je transformacji

Laplace’a

dit t

Lt

ut t Rt it t Giw0 t G0 iw t

dt

Otrzymamy

Lt sI t s U t s Rt I t s Giw0 s G0 I w s

Rt Lt s I t s U t s Giw0s G0 I w s

I t s

1

U t s Giw0s G0 I w s

Rt Lt s

1

Rt

U t s Giw0s G0 I w s

I t s

Lt

1 s

Rt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

86

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

1

Rt

I t s

U t s Giw0 s G0 I w s

L

1 t s

Rt

s

I w s

Gi w 0

-

G0

-

1

Rt

Lt

1 s

Rt

I t s

U t s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

87

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zestawimy schemat całego modelu

U w s

U t s

1

Rw

L

1 w s

Rw

I w s

I w s

s

I w s

G 0

Gi w 0

M oz s

Kazimierz Duzinkiewicz, dr hab. inż.

-

1

I t s

Rt

L

1 t s

Rt

I t s

I w s

Gi t 0

I t s

Gi w 0

-

Katedra Inżynierii Systemów Sterowania

1

D

J

1 s

D

s

88

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Model obiektu/systemu typu wejście-wyjście wyrażony za pomocą

transmitancji

operatorowych

można

oczywiście

stosować

dla

obiektów/systemów wielowymiarowych

Zastosujemy tą formę reprezentacji modelu systemu do rozważanego

systemy

- modelu procesów elektromechanicznych silnika

obcowzbudnego prądu stałego

Niech

U 1 s

U s U j s

U s

s

Y1 s

Y s Yi s

Y s

l

wektory transformat wielkości wejściowych i wyjściowych

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

89

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dla systemu wielowymiarowego liniowego i stacjonarnego wprowadza się

macierz transmitancji operatorowych

G11

G s Gi 1

G

l1

G1 j G1s

Gij Gis

Glj Gls

Model obiektu/systemu typu wejście-wyjście wyrażony za pomocą

transmitancji operatorowych ma wówczas postać

Y s Gs U s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

90

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dla rozważanego modelu silnika, możemy zapisać

Gw w

G s Gt w

G

w

gdzie

Gwt

Gt t

G t

Gw M

U w s

Gt M U s U t s

M s

oz

G M

I w s

Y s I t s

s

I w s

U w s

I w s

Gwt s

U t s

Gw M s

I s

Gt w s t

U w s

I s

Gt t s t

U t s

I t s

Gt M s

M oz s

s

G w s

U w s

s

G t s

U t s

G w w s

Kazimierz Duzinkiewicz, dr hab. inż.

G M s

I w s

M oz s

s

M oz s

Katedra Inżynierii Systemów Sterowania

91

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Poszczególne elementy macierzy określa się korzystając z liniowości

systemu (spełnianie zasady superpozycji)

Nietrudno, w oparciu o schemat blokowy stwierdzić

1

I s

Rw

Kw

Gw w s w

U w s 1 Lw s 1 Tw s

Rw

Gw t s

Kw

gdzie

L

1

, Tw w

Rw

Rw

I w s

0

U t s

Gw M s

Kazimierz Duzinkiewicz, dr hab. inż.

I w s

0

M oz s

Katedra Inżynierii Systemów Sterowania

92

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Jeżeli wybrać za wielkość sterującą napięcie twornika ut(t), to najbardziej

interesującymi transmitancjami będą transmitancje w torach

G t s

s

G M s

U t s

s

M oz s

Ustalmy określające je wyrażenia

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

93

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Odpowiedni fragment schematu blokowego dla toru: prędkość kątowa –

napięcie twornika

U t s

Gi w 0

-

1

Rt

L

1 t s

Rt

Gi w 0

1

D

J

1 s

D

s

Struktura: pętla ujemnego sprzężenia zwrotnego

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

94

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Tor główny

U t s

1

Rt

L

1 t s

Rt

Gi w 0

1

D

J

1 s

D

s

Tor sprzężenia zwrotnego

-

Gi w 0

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

95

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Otrzymamy

Giw0

Giw0

Rt D

Rt D

L

L

J

J

Giw0

1 t s 1 s

1 t s 1 s

Rt

D

Rt

D

Rt D

G t s

2

2

Giw0 2

Lt

Lt

J Giw0

J Giw0

1 s 1 s

1 s 1 s

Rt D

R

D

R

D

Rt

D

Rt D

t

t

1

L

J

L

J

1 t s 1 s

1 t s 1 s

Rt

D

Rt

D

Giw0

Giw0

Rt D

Rt D

2

2

Lt

J Giw0

Lt J 2 Lt J Giw0

1 s 1 s

s s 1

R

D

R

D

R

D

R

D

R

D

t

t

t

t

t

Tor: prędkość kątowa – napięcie twornika ma cechy układu drugiego rzędu

K p 02

Kp

Y( s )

G2 rz ( s )

U ( s ) s 2 2 0 s 02 T02 s 2 2 T0 s 1

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

T0

1

0

96

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Odpowiedni fragment schematu blokowego dla toru: prędkość kątowa –

moment obciążenia zewnętrznego

Gi w 0

-

1

Rt

L

1 t s

Rt

Gi w 0

-

M oz s

1

D

J

1 s

D

s

Struktura: pętla ujemnego sprzężenia zwrotnego

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

97

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Tor główny

M oz s

-

s

1

D

J

1 s

D

Tor sprzężenia zwrotnego

-

Gi w 0

Kazimierz Duzinkiewicz, dr hab. inż.

1

Rt

L

1 t s

Rt

Gi w 0

Katedra Inżynierii Systemów Sterowania

98

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Otrzymamy

1

1

D

D

J

J

1 s

1 s

D

D

G M s

2

2

Giw0

Giw0 1 Lt

L

J

1 t s 1 s

Rt D

Rt

D

Rt D

Rt

1

L

J

L

J

1 t s 1 s

1 t s 1 s

Rt

D

Rt

D

L

1

1 t

D

Rt

s

2

J Giw0

s 1 s

D

Rt D

L

L

1

1

1 t s

1 t s

D

Rt

D

Rt

2

2

Lt

J Giw0

Lt J 2 Lt J Giw0

1 s 1 s

s s 1

Rt

D

Rt D

Rt D

Rt D

Rt D

Tor: prędkość kątowa – moment oporowy zewnętrzny ma cechy układu drugiego

rzędu z takim samym równaniem charakterystycznym jak tor prędkość kątowa

– napięcie twornika

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

99

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Częściowo wypełniliśmy macierz transmitancji G(s)

Gw w

G s Gt w

G

w

Gw t

Gt t

G t

1

R

w

1 Lw s

Rw

Gt w

G w ?

Gw M

Gt M

G M

0

Gt t ?

Giw0

Rt D

2

Lt J 2 Lt J Giw0

s s 1

Rt D

Rt D

Rt D

Kazimierz Duzinkiewicz, dr hab. inż.

0

Gt M ?

L

1

1 t s

D

Rt

2

Lt J 2 Lt J Giw0

s s 1

Rt D

Rt D

Rt D

Katedra Inżynierii Systemów Sterowania

100

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dalej wprowadźmy następujące założenia

Przyjmijmy, że napięcie wzbudzenia posiada stałą wartość lub nawet

założenie, że załączane jest na stałą wartość na tyle wcześniej przed

momentem zmian innych wejść systemu, że ustaną w tej części systemu

przebiegi przejściowe. Prowadzi to do:

* silnik jest systemem liniowym stacjonarnym, ale

* uzyskany przy poprzednich założeniach model transmitancyjny ulega

zmianie

Powód drugiej zmiany – napięcie uw(t) nie spełnia warunku L1 stosowania

przekształcenia Laplace’a

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

101

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Prześledźmy te zmiany

Jeżeli ustalona wartość napięcia wzbudzenia wynosi

U wn

to oznaczając odpowiadającą tej wartości napięcia wzbudzenia wartość

prądu wzbudzenia

I wn

U wn

Rw

Otrzymamy model

d t

J

GI wn it t D t M oz t

dt

di t

Lt t ut t Rt it t GI wn t

dt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

102

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dla uproszczenia oznaczmy

GI wn K wn

wówczas

J

d t

K wn it t D t M oz t

dt

dit t

Lt

ut t Rt it t K wn t

dt

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

103

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy pierwsze równanie i poddajmy je transformacji Laplace’a

d t

J

K wn it t D t M oz t

dt

Otrzymamy

Jss K wn I t s Ds M oz s

D Js s K wn I t s M oz s

s

1

K wn I t s M oz s

D Js

1

Km

K wn I t s M oz s

s D K wn I t s M oz s

J

1 Tm s

1 s

D

1

gdzie

Kazimierz Duzinkiewicz, dr hab. inż.

Km

Katedra Inżynierii Systemów Sterowania

D

, Tm

J

D

104

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

s

I t s

Km

K wn I t s M oz s

1 Tm s

K wn

-

Km

1 Tm s

s

M oz s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

105

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Weźmy drugie równanie i poddajmy je transformacji Laplace’a

Lt

dit t

ut t Rt it t K wn t

dt

Otrzymamy

Lt sI t s U t s Rt I t s K wn s

Rt Lt s I t s U t s K wn s

1

U t s K wn s

I t s

Rt Lt s

1

Rt

Kt

U t s K wn s

I t s

U t s K wn s

Lt

1 Tt s

1 s

Rt

gdzie

Kazimierz Duzinkiewicz, dr hab. inż.

Lt

1

K t , Tt

Rt

Rt

Katedra Inżynierii Systemów Sterowania

106

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

I t s

s

Kt

U t s K wn s

1 Tt s

K wn

-

Kt

1 Tt s

I t s

U t s

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

107

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Zestawimy schemat całego modelu

U t s

s

K wn

M oz s

Kazimierz Duzinkiewicz, dr hab. inż.

-

Kt

1 Tt s

I t s

I t s

I t s

K wn

-

Katedra Inżynierii Systemów Sterowania

1

D

J

1 s

D

s

108

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Nietrudno spostrzec, że mimo zmian modelu transmitancyjnego

systemu, struktura transmitancji w torach : prędkość kątowa –

napięcie twornika oraz prędkość kątowa – moment oporowy

zewnętrzny pozostają niezmienione (ćwiczenie własne – pokazać to)

Inne ćwiczenie:

Dla schematu

transmitancji

z

Gt t

G s

G t

gdzie

poprzedniego

Gt M

G M

I t s

Gt t s

U t s

s

G t s

U t s

Kazimierz Duzinkiewicz, dr hab. inż.

slajdu

policzyć

całą

macierz

U t s

I t s

Y s

U s

s

M oz s

Gt M s

I t s

M oz s

G M s

s

M oz s

Katedra Inżynierii Systemów Sterowania

109

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Wprowadzimy jeszcze jedno uproszczenie

Jeżeli nie interesować się przebiegami prądu twornika, uzyskamy

prosty model liniowy stacjonarny silnika jako obiektu sterowanego

prędkości kątowej z jednym wejściem sterującym, jednym wejściem

zakłócającym i jednym wyjściem

U t s

M oz s

Kazimierz Duzinkiewicz, dr hab. inż.

G t s

s

G M s

Katedra Inżynierii Systemów Sterowania

110

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Lub bardziej szczegółowo

M oz s

U t s

-

Kt

1 Tt s

I t s

K wn

s

Km

1 Tm s

K wn

Gs G t

G M

U t s

U s

M oz s

Y s s

gdzie

s

G t s

U t s

Kazimierz Duzinkiewicz, dr hab. inż.

s

G M s

M oz s

Katedra Inżynierii Systemów Sterowania

111

Teoria sterowania SN

Schematy analogowe i blokowe, realizowalność modeli stanu

Dziękuję

– koniec materiału prezentowanego podczas wykładu

Kazimierz Duzinkiewicz, dr hab. inż.

Katedra Inżynierii Systemów Sterowania

112