BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 1/7

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

1. Wiadomości wstępne

Monolityczne układy scalone TTL (z ang. Trasistor Transistor Logic) stanowią obecnie najbardziej

rozpowszechnioną grupę elektronicznych elementów przełączających. Układy te przeznaczone są

do realizacji logicznych struktur w urządzeniach cyfrowych. Z tego względu konstrukcja i

parametry tych układów zostały ujedno1icone. Sygnały cyfrowe mogą przyjmować tylko jedną z

dwóch ściśle określonych wartości napięć. Praktycznie określa się przedziały, w których mogą

znajdować się wartości napięć odpowiadające poziomowi wysokiemu H (z ang. high) i poziomowi

niskiemu L (z ang. low). Dla układów scalonych TTL wynoszą one:

- poziom H ("l" logiczne) - napięcie +2 V do +5,5 V,

- poziom L ("0" logiczne) - napięcie -0,5 V do +0,8 V.

W poprawnie działającym układzie, napięcie wyjściowe zawiera się zwykle w węższych granicach:

- poziom H - napięcie +2,4 V do +5 V,

- poziom L - napięcie 0V do +0,4V.

Elementarny układ TTL ma za zadanie realizować określoną funkcję logiczną oraz odpowiednio

wzmacniać sygnał wyjściowy. Wszystkie układy TTL wymagają zasilania ze źródła napięcia stałego

o wartości +5 ±0,25V.

Przekroczenie tego zakresu może spowodować uszkodzenie układu lub jego błędne działanie.

Podstawowymi elementami techniki cyfrowej TTL są bramki logiczne i przerzutniki.

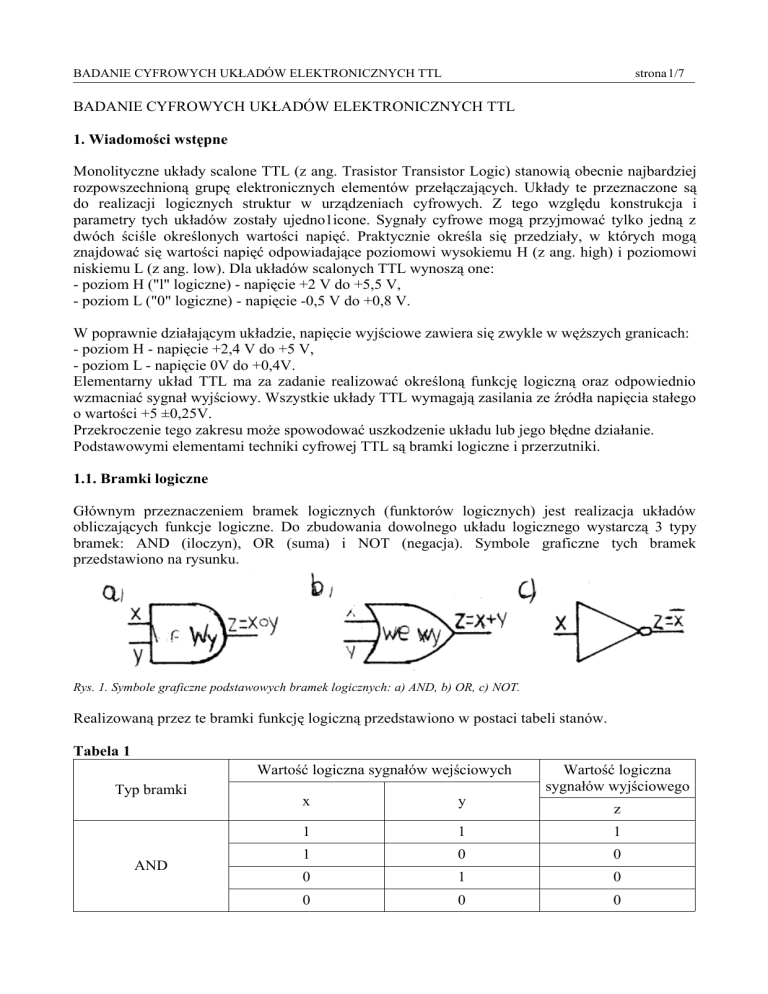

1.1. Bramki logiczne

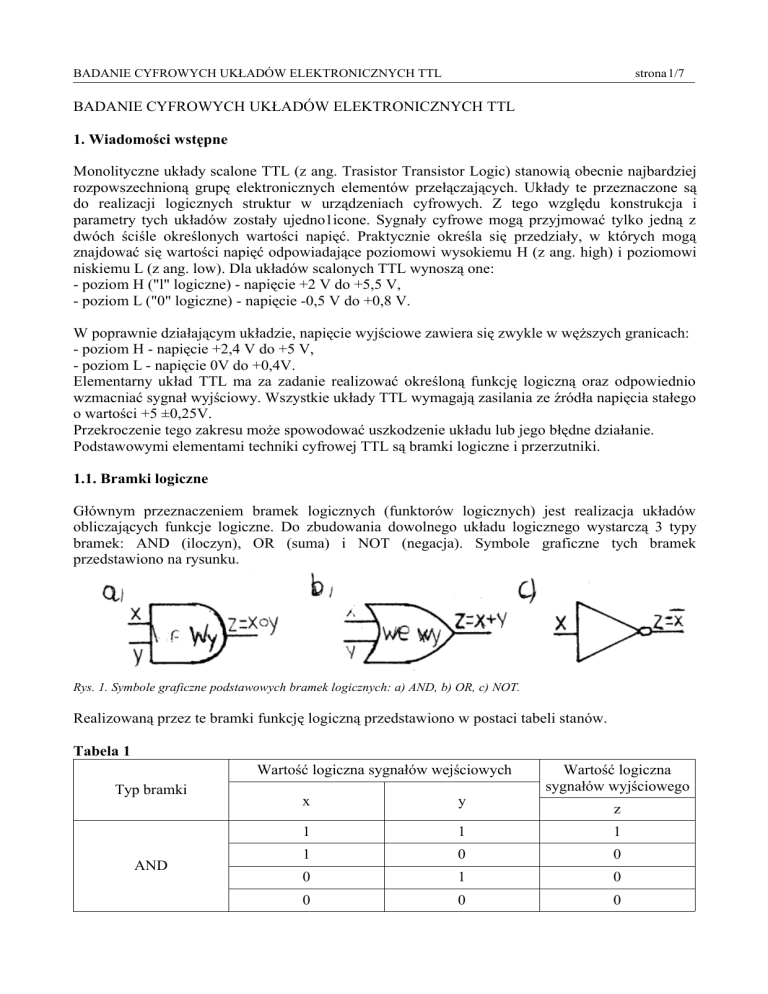

Głównym przeznaczeniem bramek logicznych (funktorów logicznych) jest realizacja układów

obliczających funkcje logiczne. Do zbudowania dowolnego układu logicznego wystarczą 3 typy

bramek: AND (iloczyn), OR (suma) i NOT (negacja). Symbole graficzne tych bramek

przedstawiono na rysunku.

Rys. 1. Symbole graficzne podstawowych bramek logicznych: a) AND, b) OR, c) NOT.

Realizowaną przez te bramki funkcję logiczną przedstawiono w postaci tabeli stanów.

Tabela 1

Wartość logiczna sygnałów wejściowych

Typ bramki

AND

Wartość logiczna

sygnałów wyjściowego

x

y

1

1

1

1

0

0

0

1

0

0

0

0

z

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 2/7

Tabela 2

Wartość logiczna sygnałów wejściowych

Typ bramki

OR

Wartość logiczna

sygnałów wyjściowego

x

y

1

1

1

1

0

1

0

1

1

0

0

0

z

Tabela 3

Wartość logiczna sygnałów wejściowych

Typ bramki

NOT

x

Wartość logiczna

sygnałów wyjściowego

z

0

1

1

0

Produkuje się jednak znacznie więcej typów bramek. Różnią się one między sobą liczbą wejść,

realizowaną funkcją lub parametrami elektrycznymi. Szeroki zestaw produkowanych układów

logicznych umożliwia budowę urządzeń przy wykorzystaniu mniejszej liczby elementów

składowych.

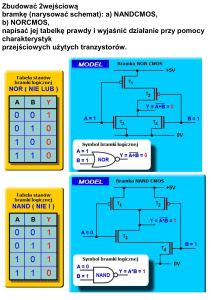

Podstawowym elementem układów cyfrowych jest bramka NAND. Jest ona elementem

uniwersalnym, ponieważ przy jej użyciu można zbudować każdą inną bramkę lub zrealizować

dowolny układ logiczny. Symbol bramki NAND przedstawiono na rys. 2.

Rys. 2. Symbol graficzny bramki NAND.

Sposób realizacji funktorów AND, OR i NOT przy użyciu bramki NAND pokazano na rys. 3.

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 3/7

Rys. 3. Sposób realizacji przy wykorzystaniu bramki NAND bramek: a) AND, b) OR, c) NOT.

Bramka NAND realizuje funkcję logiczną według tabeli stanów przedstawionej w tabeli 4.

Tabela 4

Wartość logiczna sygnałów wejściowych

Typ bramki

NAND

Wartość logiczna

sygnałów wyjściowego

x

y

1

1

0

1

0

1

0

1

1

0

0

1

z

Właściwości statyczne bramek określają podstawowe charakterystyki statyczne:

-charakterystyka wejściowa Il=f(Ul);

-charakterystyka przenoszenia U2=f(Ul);

-charakterystyka wyjściowa U2=f(I2).

Przeciętne charakterystyki statyczne przedstawiono na rys.1.

Do charakterystycznych parametrów dynamicznych bramek TTL należą:

-czas narastania zboczy impulsów;

-czas narastania i opadania napięcia wejściowego przy przełączaniu bramki.

1.2. Przerzutniki

Drugą podstawową rodziną elementów techniki cyfrowej są przerzutniki. Są to elementy

umożliwiające zapamiętanie konkretnego stanu na wyjściu i określoną zmianę tego stanu w

zależności od kombinacji sygnałów wejściowych. Przerzutniki możemy podzielić na synchroniczne

i asynchroniczne. Przerzutniki synchroniczne zmieniają stan na wyjściu w wyróżnionych chwilach

czasowych. Przerzutniki asynchroniczne zmieniają stan na wyjściu bezpośrednio po odpowiedniej

zmianie sygnałów wejściowych.

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 4/7

Podstawowymi przerzutnikami asynchronicznymi są przerzutniki typu RS i D. W przerzutniku typu

RS występujią dwa wejśc ia steruące: R i S, a w przerzutniku typu D jest jedno wejście sterujące: D.

W obu typach przerzutników występują dwa wyjścia wzajemnie się uzupełniające: wyjście proste Q

i zanegowane Q'. Symbole graficzne tych przerzutników pokazano na rys. 4.

Rys. 4. Symbole graficzne przerzutnika: a) typu RS, b) typu D.

Opis działania przerzutników podaje się w postaci tablic działania.

Zawierają one informacje o wartościach logicznych sygnałów wejściowych i o odpowiadających im

wartościom logicznym sygnałów wyjściowych. W tablicach działania sygnał oznaczony Q(t+l)

odpowiada sygnałowi wyściowemu po zmianie kombinacji sygnałów wejściowych. Sygnał

oznaczony Q(t) oznacza sygnał występujący na wyjściu przed zmianą kombinacji sygnałów

wejiściowych. Niedozwoloną kombinację sygnałów wejściowych oznaczono jako X. Tablicę

działania przerzutnika typu RS przedstawiono w tabeli 5, zaś w tabeli 6 pokazano tablicę działania

przerzutnika typu D.

Tabela 5

Typ przerzutnika

RS

Wartość logiczna sygnałów

wejściowych

Wartość logiczna sygnałów

wyjściowych

R

S

Q(t+1)

Q(t+1)

1

1

X

X

1

0

1

0

0

1

0

1

0

0

Q(t)

Q'(t)

Tabela 6

Typ przerzutnika

D

Wartość logiczna sygnału

wejściowego

Wartość logiczna sygnałów

wyjściowych

Q(t+1)

Q(t+1)

1

0

1

0

1

0

Przerzutniki typu RS i typu D można zbudować przy wykorzystaniu bramek typu NAND. Sposób

realizacji tych przerzutników pokazano na rys. 6.

Przerzutniki produkowane są również w postaci układów scalonych. W jednej obudowie umieszcza

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 5/7

się zwykle od 1. do 6. przerzutników.

2. Program ćwiczenia

Typowym układem scalonym zawierającym bramki NAND jest układ UCY7400. Wyprowadzenia

tego układu przedstawia rysunek.

Rys. 5. Wyprowadzenia układy scalonego UCY7400.

UWAGA!

Badane układy TTL są zasilane napięciem +5V i 0V (zacisk masy zasilacza). Poszczególne układy

pomiarowe należy łączyć przy wyłączonym napięciu zasilającym.

2.1. Sprawdzanie działania funktorów logicznych

Połączyć układ pomiarowy. Po ustawieniu odpowiedniej kombinacji sygnałów wejściowych "x" i

"y" (+5V dla "1" i 0 V dla "0") odczytać wartość sygnału wyjściowego "z" bramki "NAND".

Wyniki zestawić w tabeli

Wartość logiczna sygnałów wejściowych

Typ bramki

NAND

x

y

1

1

1

0

0

1

0

0

Wartość logiczna

sygnałów wyjściowego

z

Połączyć układy pomiarowe do sprawdzenia działania funktorów logicznych "NOT", "AND" i

"OR". Podając na wejście kombinację sygnałów wejściowych "0" i "l" odczytać wartość sygnału

wyjściowego. Wyniki badań zestawić w tabelach stanów.

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 6/7

Wartość logiczna sygnałów wejściowych

Typ bramki

x

Wartość logiczna

sygnałów wyjściowego

z

0

NOT

1

Wartość logiczna sygnałów wejściowych

Typ bramki

AND

x

y

1

1

1

0

0

1

0

0

Wartość logiczna sygnałów wejściowych

Typ bramki

OR

x

y

1

1

1

0

0

1

0

0

Wartość logiczna

sygnałów wyjściowego

z

Wartość logiczna

sygnałów wyjściowego

z

2.2. Sprawdzenie działania przerzutników typu "RS" i "D"

Połączyć układ do badania przerzutnika typu "RS" zbudowanego z bramek TTL. Ustawić

odpowiednią kombinację sygnałów wejściowych i odczytać wartość sygnałów wyjściowych.

Wyniki zestawić w formie tabeli działania.

Wartość logiczna sygnałów

Wartość logiczna sygnałów wyjściowych

wejściowych

Typ

Układ zrealizowany z

Przerzutnik z układu

przerzutnika

RS

bramek TTL

R

S

1

1

1

0

1

1

0

1

1

1

0

0

1

1

Q(t+1)

Q'(t+1)

scalonego

Q(t+1)

Q'(t+1)

BADANIE CYFROWYCH UKŁADÓW ELEKTRONICZNYCH TTL

strona 7/7

Połączyć układ do badania przerzutnika typu "D" zbudowanego z bramek TTL. Ustawić wartość

sygnał u wejściowego "0” lub "1" i odczytać wartość sygnałów wyjściowych.

Wyniki zestawić w postaci tabeli działania

Typ

przerzutnika

Wartość logiczna sygnałów

wejściowych

D

1

0

RS

1

0

Wartość logiczna sygnałów wyjściowych

Układ zrealizowany z

bramek TTL

Przerzutnik z układu

scalonego

Q(t+1)

Q(t+1)

Q'(t+1)

Q'(t+1)