DIAGNOSTYKA UKŁADÓW CYFROWYCH.

HAZARD w układach cyfrowych

Spis treści

Wiadomości teoretyczne: ...................................................................................................... 2

Zasilanie ............................................................................................................................ 2

Nie używane elementy i nie używane wejścia elementów logicznych ............................. 2

Zwarcie wyjścia do masy .................................................................................................. 2

Zwarcie wyjścia do potencjału Ucc źródła zasilania.......................................................... 3

Hazard statyczny: .............................................................................................................. 3

Bramka NAND .................................................................................................................. 5

Podstawowa bramka TTL 7400 ........................................................................................ 6

Badanie układu z przerwą w obwodzie zasilania .................................................................. 7

Brak masy .......................................................................................................................... 7

Brak połączenia z biegunem dodatnim źródła zasilania Ucc ............................................. 8

Badanie układów zawierających nie wykorzystane bramki.............................................. 9

Badanie bramek z nie używanymi wejściami (wejściami ‘w powietrzu’) ..................... 10

Badanie Bramek z wyjściem zwartym do masy.............................................................. 11

Pytania sprawdzające........................................................................................................... 13

Wiadomości teoretyczne:

Konstruowanie i uruchamianie układów cyfrowych związane jest często z koniecznością

wyszukania w zamontowanym układzie źródeł jego wadliwego działania. Przyczyną wadliwego

działania może być spowodowana błędami lub nieprzestrzeganiem określonych zasad projektowania i

konstruowania układów cyfrowych. Źródłem części z nich mogą być błędy montażu polegające na

niestarannym lutowaniu, powodującym brak kontaktu elektrycznego, co prowadzi do przerw w

przesyłaniu sygnałów, pozostawienia wejść i wyjść „w powietrzu”, braku zasilania, itp. W tym

ćwiczeniu zajmiemy się poznaniem metod i sposobów identyfikacji źródeł błędnego działania układów

cyfrowych na podstawie obserwowanych objawów ich wadliwego działania.

Zasilanie

Znamionowa wartość napięcia zasilania Ucc układów TTL wynosi 5V. Dopuszczalne zmiany

napięcia nie powinny być większe niż 5% wartości znamionowej. Napięcie zasilania Ucc układów

CMOS powinno mieć wartość z przedziału 3 – 5,5V. Dopuszczalne zmiany napięcia nie powinny być

większe niż 10% wartości Ucc.

Nie używane elementy i nie używane wejścia elementów logicznych

Wyjścia nie używanych elementów TTL zaleca się ustawić w stan wysoki H. Takie postępowanie

zmniejsza pobór prądu przez układ. Ponadto wyjścia takich elementów można wówczas używać (jako

źródeł) do ustawiania nie wykorzystywanych wyjść w stan wysoki.

Pozostawienie nigdzie nie dołączonych wejść elementów TTL powoduje zmniejszenie odporności

elementu logicznego na działanie zakłóceń, dlatego należy unikać takich sytuacji i stosować poniższe

zasady postępowania z nie używanymi wejściami:

1. Nie używane wejścia bramek NAND, AND należy dołączyć do napięcia Ucc. Można także

dołączyć je do wyjścia bramki nie używanej, którą należy tak sterować, aby ustawić ją w stan

wysoki.

2. Nie używane wejścia dowolnych bramek można połączyć z używanymi wejściami (tej samej

bramki), jeśli nie zostanie w ten sposób przekroczona dopuszczalna obciążalność układu

sterującego.

3. Nie wykorzystywane wejścia bramek OR, NOR należy łączyć do masy.

W odniesieniu do układów CMOS zasada ustawiania wyjść elementów logicznych w dany stan

(wysoki – H, niski – L) nie ma zastosowania, bowiem układy te pobierają jednakową (znikomą) moc w

obu stanach logicznych.

Nie używane wejścia elementów CMOS nie wolno pozostawić nigdzie nie dołączonych bo wówczas

napięcie wyjściowe ustala się w pobliżu napięcia przełączania. Bramka taka się wzbudza, pobiera

znaczny prąd i zakłóca pracę innych elementów.

Zwarcie wyjścia do masy

Połączenie wyjścia układu cyfrowego (bramki) z masą układu powoduje skutki zależne od stanu

wyjścia w chwili, w której dochodzi do stanu zwarcia. Jeżeli wyjście znajdowało się w stanie niskim L, to

zwarcie takiego wyjścia do masyw przypadku układów TTL obniży napięcie wyjściowe z wartości 0,2 –

0,5 V do zera i spowoduje nieznaczny wzrost prądu pobieranego przez układ.

Jeśli jednak element cyfrowy jest tak sterowany, że jego wyjście znajduje się w stanie wysokim H, to

skutki zwarcia takiego wyjścia do masy są już zauważalne. Maleje napięcie wyjściowe do zera i wzrasta

prąd wypływający z wyjścia. Prąd ten zwany prądem zwarciowym Ios, osiąga dużą (rzędu kilkudziesięciu

miliamperów) wartość. Stan taki nie grozi zniszczeniem układu, o ile dotyczy on tylko jednego

wyjścia układu scalonego. Zwarcie do masy większej liczby wyjść (znajdujących się w stanie H)

może doprowadzić do przegrzania i zniszczenia układu. Każde takie wyjście powoduje grzanie układu

mocą o wartości Ucc * Ios. Moce te sumują się i łatwo mogą przekroczyć dopuszczalną moc, jaka może

być tracona (zamieniana na ciepło) w jednym układzie.

W przypadku układów CMOS zwarcie do masy wyjścia znajdującego się w stanie niskim L,

nie spowoduje zauważalnych zmian napięcia i prądu.

Jeśli jednak element cyfrowy jest tak sterowany, że jego wyjście znajduje się w stanie

wysokim H, to skutki takiego zwarcia są identyczne jak w przypadku układów TTL.

Zwarcie wyjścia do potencjału Ucc źródła zasilania

Jeżeli wyjście znajduje się w stanie H połączymy z biegunem dodatnim Ucc napięcia

zasilającego, to nie spowoduje to istotnych skutków w pracy układu. Wystąpienie takiego połączenia

podczas, gdy wyjście to znajduje się w stanie L, prowadzi do dużego wzrostu prądu wpływającego do

tego wyjścia. Wartość tego prądu jest większa niż prąd zwarcia w układach TTL i podobna do prądu

zwarcia w układach CMOS. Ze względu na większe prądy (niż prądy zwarciowe) taki stan pracy jest

bardziej niebezpieczny dla układów cyfrowych i szybciej może doprowadzić do przegrzania układu.

Jednak przeważnie jest on dopuszczalny, jeżeli trwa zbyt długo.

Hazard statyczny:

Hazardem nazywamy błędne stany na wyjściach układów cyfrowych, powstające w stanach

przejściowych (przełączania) w wyniku nieidealnych właściwości używanych elementów. Jeśli źródłem

takiego błędnego stanu na wyjściu są nieidealne właściwości przełączające, to hazard taki nazywamy

statycznym, jeżeli transmisyjne, to dynamicznym. Wartość następującego wyrażenia bulowskiego

x

+ x jest zawsze równa 1. Jednak w rzeczywistym układzie (zbudowanym z bramek) na wyjściu tak

opisanego układu może pojawić się na krótko stan niski w chwili, gdy sygnał x będzie zmieniał swój stan.

Sytuacja będzie miała takie miejsce np. w układzie pokazanym na rys. 2.1. wówczas, gdy sygnały

wejściowe a = b = H a sygnał x będzie zmieniał swój stan. Przykład ten pokazuje jednocześnie

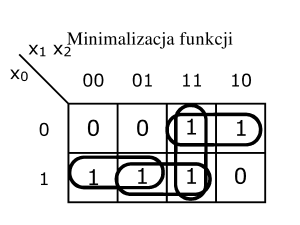

możliwość identyfikacji występowania hazardu statycznego na podstawie zakreślonej tablicy Karnaugha.

Hazard ma miejsce wtedy, gdy w takiej tablicy występują grupy (jedynek lub zer) sąsiadujące ze sobą. O

sąsiadowaniu mówimy jednak tylko wówczas, gdy grupy takie mają co najmniej jedną krawędź wspólną.

Grupy stykające się jedynie narożnikami nie są grupami sąsiadującymi.

Rys.1.1. Układ kombinacyjny z hazardem statycznym a)tablica Karnaugha; b) schemat układu; c)

przebiegi czasowe na wejściach i wyjściach bramki wyjśćiowej

Likwidacja hazardu polega na wprowadzeniu dodatkowej grupy (oczywiście nie będzie to już wówczas

postać minimalna takiej funkcji), zawierającej elementy sąsiadujących ze sobą grup. Ale jeżeli grupy ze

sobą sąsiadują, to zawsze będzie istniała możliwość wprowadzenia takiej dodatkowej grupy rys. 2.2.

Rys. 1.2. Likwidacja hazardu w układzie z rys. 1.1 a) zmodyfikowana tablica Karnaugha; b) układ

pozbawiony hazardu

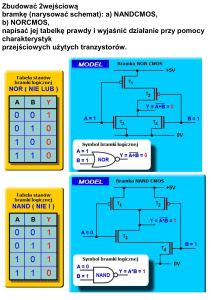

Bramka NAND

Bramka NAND (nie i) jest układem o dwu lub większej liczbie wejść. Realizuje ona funkcję

negacji iloczynu zmiennych wejściowych rys. 1.3.

Rys 1.3. Tablica prawdy i symbol graficzny bramki NAND

Bramka ta jest funkcjonalnie pełna, bowiem stosując ją można zrealizować zarówno operację

iloczynu logicznego (AND) jak i operację negacji (NOT) – czyli zgodnie z wcześniejszymi wnioskami

dowolną funkcje logiczną.

Realizacja negacji przy użyciu bramki NAND rys. 1.4.

Realizacja iloczynu logicznego przy użyciu bramek NAND rys. 1.5.

Podstawowa bramka TTL 7400

Układ 7400 zawiera w swej obudowie cztery dwuwejściowe bramki NAND. Jest to układ 14nóżkowy. Po trzy (dwie wejściowe, jedna wyjściowa) nóżki na każdą z czterech bramek plus dwie na

doprowadzenie napięcia zasilajacego.

Schemat ideowy bramki rys. 1.6.

Badanie układu z przerwą w obwodzie zasilania

Brak masy

Zbadać zachowanie się bramki NAND (TTL, CMOS) przy braku połączenia z masą

doprowadzeń zasilających układ scalony zawierający badaną bramkę. Zmierzyć napięcie na jej

wyjściu przy różnych stanach wejść. Symbole badanych układów oraz uzyskane wyniki zanotować

w tabeli. Porównać zachowanie się bramki w przypadku braku przerwy w obwodzie zasilania.

Określić różnice w zachowaniu się bramki z przerwą i bez w obwodzie zasilania. Wskazać na te

objawy, które można uznać za charakterystyczne dla pracy z brakiem połączenia z masą.

Tabela 1

Brak połączenia z biegunem dodatnim źródła zasilania Ucc

Zbadać zachowanie się bramki NAND (TTL, CMOS) przy braku połączenia z biegunem

dodatnim Ucc doprowadzeń zasilających układ scalony zawierający badana bramkę. Zmierzyć

napięcie na jej wyjściu przy różnych stanach wejść. Symbole badanych układów oraz uzyskane

wyniki zanotować w tabeli. Porównać zachowanie się bramki w przypadku braku przerwy w

obwodzie zasilania.

Określić różnice w zachowaniu się bramki z przerwą i bez w obwodzie zasilania. Wskazać na te

objawy, które można uznać za charakterystyczne dla pracy z brakiem połączenia z biegunem dodatnim

Ucc.

Tabela 2

Badanie układów zawierających nie wykorzystane bramki

Zmierzyć prądy pobierane przez układy TTL i CMOS zawierające bramki NAND nie

wykorzystane, tzn. z wejściami i wyjściami ‘w powietrzu’. Zmienić liczbę bramek nie

wykorzystanych. Powtórzyć powyższe pomiary sterując tak wejściami wszystkich bramek, aby

ustawić wyjścia w stan H oraz w stan L. Symbole badanych układów oraz uzyskane wyniki

zanotować w tabeli.

Porównać otrzymane wyniki. Sformułować wnioski – określić zalecenia odnośnie do

postępowania z nie wykorzystywanymi bramkami TTL i CMOS.

Tabela 3

Badanie bramek z nie używanymi wejściami (wejściami ‘w powietrzu’)

Sprawdzić zachowanie się bramki (sporządzić tablicę prawdy) przy sterowaniu jej wejść,

podczas gdy co najmniej jedno z wejść pozostaje nigdzie nie dołączone. Zmierzyć napięcia na nie

używanych wejściach. Zaobserwować na oscyloskopie sygnał wyjściowy bramki. Pomiary wykonać

dla bramki TTL i CMOS.

Uzasadnić otrzymane wyniki pomiarów. Wskazać na różnice w zachowaniu się układów TTL i

CMOS. Sformułować zasady postępowania z nie używanymi wejściami układów TTL i CMOS.

Przykład tabeli, tablicy prawdy z wejściem ‘w powietrzu’

Schemat układu pomiarowego:

Badanie Bramek z wyjściem zwartym do masy.

Zmierzyć wyjściowy prąd w stanie zwarcia wyjścia bramki do masy. Bramkę sterować tak, aby

ustawić ją w stan L oraz H. Zmierzyć prąd pobierany przez układ scalony. Sprawdzić przez dotyk,

czy jest wyczuwalne grzanie się układu.

Porównać otrzymane wyniki w obu przypadkach sterowania bramki. Obliczyć moc traconą w

bramce. Porównać ją z dopuszczalnymi stratami mocy badanego układu.

3.5. Badanie bramek z wyjściem zwartym do potencjału Ucc źródła zasilania.

Zmierzyć wyjściowy prąd w stanie zwarcia wyjścia bramki do potencjału Ucc. Bramkę sterować

tak, aby ustawić ją w stan L oraz w stan H. Zmierzyć prąd pobierany przez układ scalony.

Porównać otrzymane wyniki w obu przypadkach sterowania bramki. Obliczyć moc traconą w bramce.

Porównać ją z dopuszczalnymi stratami mocy badanego układu.

3.6. Badanie układu kombinacyjnego z hazardem.

Zaprojektować prosty (trójwejściowy) układ kombinacyjny, w którym pojawi się hazard

statyczny. Określić stany wejść, przy których wystąpi zjawisko hazardu, gdy zmienimy stan

jednego (któregoś) z wejść. Narysować ten układ oraz go połączyć. Doprowadzić do określonego

wcześniej wejścia sygnał z generatora fali prostokątnej, a sygnał z wyjścia układu obserwować na

oscyloskopie. Wyodrębnić impuls będący wynikiem występowania hazardu.

Zlikwidować hazard i ponowić obserwacje oscyloskopowe, aby potwierdzić skuteczność

dokonanego zabiegu.

Narysować układ pozbawiony hazardu i zaznaczyć na nim obwód odpowiedzialny za likwidację

zjawiska hazardu. Uzasadnić jego działanie.

schemat pomiarowy układu z hazardem

Pytania sprawdzające

1. Jakie skutki powoduje brak połączenia układu scalonego z masą?

2. Jakie skutki powoduje brak połączenia układu scalonego z potencjałem Ucc?

3. Jakie napięcie występuje na nie używanym wejściu bramki TTL I CMOS ?

4. Jak zachowuje się bramka TTL i CMOS z nie używanymi wejściami? Uzasadnij odpowiedź w

obu przypadkach.

5. Określ zasady postępowania z nie używanymi bramkami TTL i CMOS.

6. Podaj przykład układu kombinacyjnego z hazardem. Wskaż sytuacje, w której może on

wystąpić. Podaj sposób jego likwidacji.

![(Microsoft PowerPoint - ECiUL_wyk\263ad_4 [tryb zgodno\234ci])](http://s1.studylibpl.com/store/data/001455800_1-6a6f55c053d4f6dd6b8f4448b4d747a8-300x300.png)