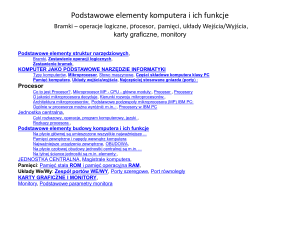

Procesor

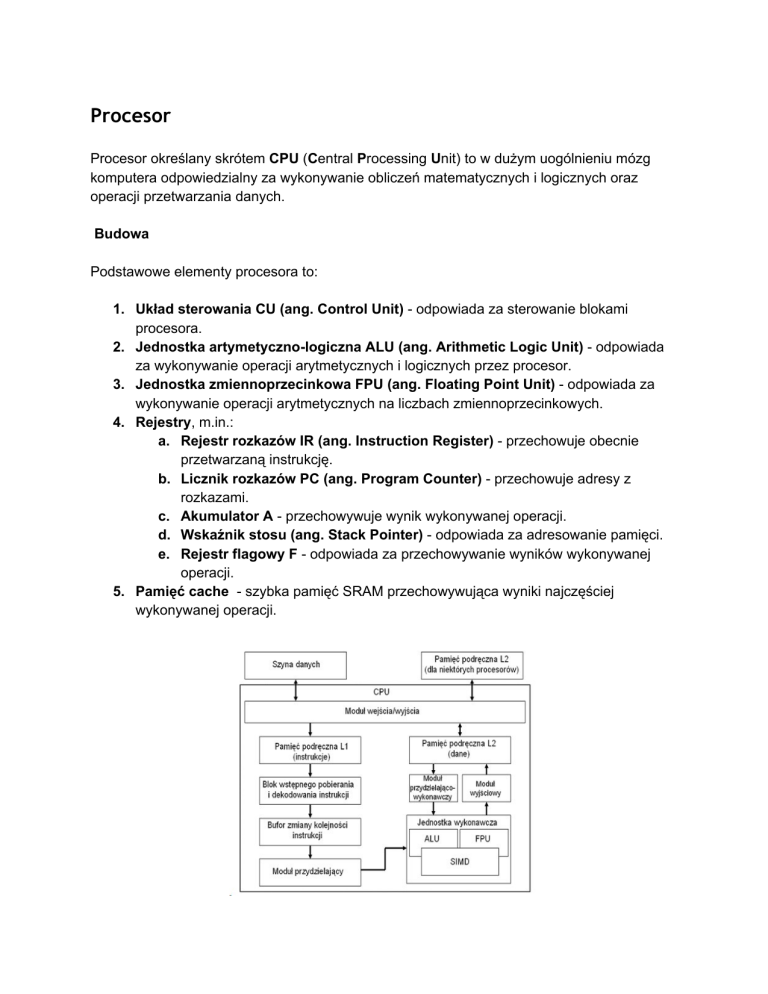

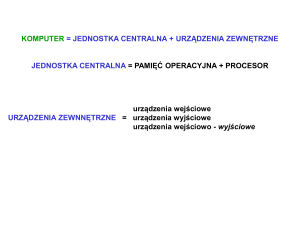

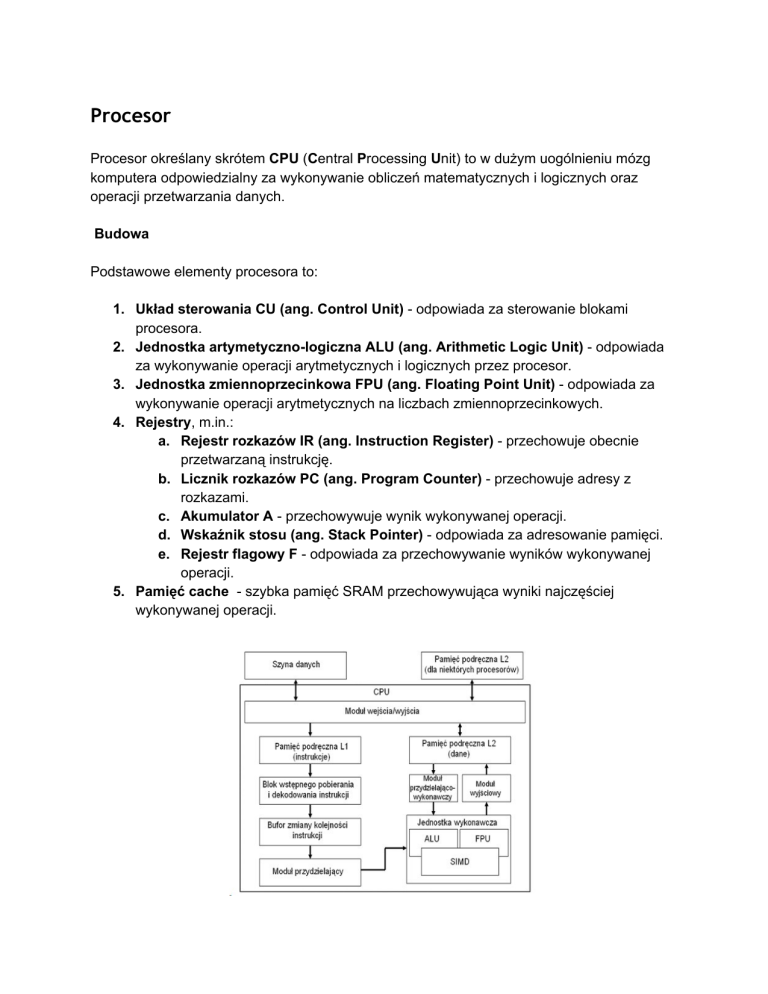

Procesor określany skrótem CPU (Central Processing Unit) to w dużym uogólnieniu mózg komputera odpowiedzialny za wykonywanie obliczeń matematycznych i logicznych oraz operacji przetwarzania danych. Budowa Podstawowe elementy procesora to: 1. Układ sterowania CU (ang. Control Unit) ­ odpowiada za sterowanie blokami procesora. 2. Jednostka artymetyczno­logiczna ALU (ang. Arithmetic Logic Unit) ­ odpowiada za wykonywanie operacji arytmetycznych i logicznych przez procesor. 3. Jednostka zmiennoprzecinkowa FPU (ang. Floating Point Unit) ­ odpowiada za wykonywanie operacji arytmetycznych na liczbach zmiennoprzecinkowych. 4. Rejestry, m.in.: a. Rejestr rozkazów IR (ang. Instruction Register) ­ przechowuje obecnie przetwarzaną instrukcję. b. Licznik rozkazów PC (ang. Program Counter) ­ przechowuje adresy z rozkazami. c. Akumulator A ­ przechowywuje wynik wykonywanej operacji. d. Wskaźnik stosu (ang. Stack Pointer) ­ odpowiada za adresowanie pamięci. e. Rejestr flagowy F ­ odpowiada za przechowywanie wyników wykonywanej operacji. 5. Pamięć cache ­ szybka pamięć SRAM przechowywująca wyniki najczęściej wykonywanej operacji. Typy obudów mikroprocesorów 1. PGA (ang. Ping Grid Array) ­ standard obudów z nóżkami w kształcie symetrycznej siatki. Odmiany PGA: a. PPGA (ang. Plastic PGA) ­ obudowa PGA z plastikowymi osłonami rdzenia. b. CPGA (ang Ceramic PGA) ­ obudowa PGA z ceramicznymi osłonami rdzenia. c. FC­PGA (ang. Flip Chip PGA) ­ obudowa PGA, w której rdzeń został przeniesiony na górną część obudowy i został zatopiony w plastikowej osłonie. d. FC­PGA2 (ang. Flip Chip PGA2) ­ podobna do FC­PGA z tą różnicą że rdzeń został przykryty stalową blaszką. 2. SPGA (ang. Staggered PGA) ­ niesymetryczne rozmieszczenie nóżek w rzędach. 3. SECC (ang. Single Edge Contact Cartrige) ­ mikroprocesor jest przylutowany do płytki drukowanej wraz z pamięcią cache L2, a całość jest umieszczona w plastikowej obudowie w postaci kartdridża. 4. SEPP (ang. Single Edge Processor Package) ­ obudowa podobna do SECC tylko bez plastikowej osłony. 5. Micro­FCBGA (ang. Flip Chip Ball Grid Array) ­ obudowa posiadająca kulki na końcu każdego pinu. Takie zastosowanie poprawia przepływ prądu między procesorem a socket’em. 6. LGA (ang. Lang Grid Array) ­ obudowa firmy Intel, nóżki zostały zastąpione pozłacanymi stykami. Magistrale mikroprocesora Do grup magistral zapewniających komunikację CPU z pozostałymi komponentami należą: 1. Magistrala danych ­ najważniejsza magistrala zapewniająca przesył danych pomiędzy procesorem a chipsetem znajdującym się na płycie głównej. Aktualnie w PC spotyka się cztery rozwiązania: a. Magistralę FSB, b. Magistralę Hyper Transport, c. Magistralę QPI, d. Magistralę DIM 2. Magistrala adresowa ­ służy do adresowania pamięci operacyjnej. Jeżeli znamy szerokość magistrali adresowej, możemy określić z jaką pamięcią może współpracować procesor. 3. Magistrala pamięci ­ odpowiada za połączenie procesora z pamięcią RAM i umożliwia wymianę danych między nimi. 4. Magistrala sterująca ­ odpowiada za przesyłanie sygnałów sterujących między CPU, pamięcią RAM i innymi urządzeniami wejścia­wyjścia. Działanie procesora CPU współpracuje z pamięcią podręczną przechowywującą dane oraz sekwencyjne ciągi instrukcji nazywane programem. Procesor pobiera z pamięci podręcznej dane wskazane przez licznik rozkazów PC (licznik za każdym razem jest uaktualniany) i umieszcza je w rejestrze rozkazów IR. Układ sterujący PC pobiera dane z rejestru IR, dekoduje rozkaz oraz ustala argumenty i rodzaj operacji następnie przesyła dane dane z rejestru do jednostki ALU, która wykonuje następujące operacje. Po przetworzeniu przez ALU wyniki są przenoszone do rejestru A lub trafiają do pamięci operacyjnej. Cała procedura cały czas się powtarza i w następnych “obiegach” przetwarzane są kolejne instrukcje. Architektura procesora W zależności od sposobu przechowywania danych i rozkazów CPU możemy wyróżnić: 1. Architekturę z Princeton ­ w tym samym bloku pamięci są przechowywane dane i programy. 2. Architekturę harwardzką ­ rozkazy i dane są przechowywane w oddzielnych pamięciach. 3. Architekturę mieszaną ­ połączenie powyższych architektur, z tą różnicą że wykorzystują one wspólne magistrale. W zależności od złożoności wykonywanych instrukcji: 1. Mikroprocesor CISC (ang. Complex Instruction Set Computer) ­ posiada bogaty zestaw instrukcji o dużych możliwościach. 2. Mikroprocesor RISC (ang. Reduced Instruction Set Computer) ­ posiada ograniczony zestaw instrukcji.