1.Klaster komputerowy-zwany także gronem - grupa

połączonych jednostek komputerowych, które

współpracują ze sobą w celu udostępnienia

zintegrowanego środowiska pracy. Komputery wchodzące

w skład klastra (będące członkami klastra) nazywamy

węzłami (ang. node). W istniejących rozwiązaniach

klastrowych można wyodrębnić dwie podstawowe klasy

wynikające z celów budowy takich rozwiązań:

Z reguły procesory wykonane w architekturze CISC

działają wolniej niż procesory, o przeciwstawnych

założeniach RISC, działające z tą samą częstotliwością.

-Klastry wydajnościowe: pracujące jako komputer

równoległy. Celem ich budowy jest powiększenie mocy

obliczeniowej. Wiele obecnych superkomputerów działa

na tej zasadzie.

-Zredukowana liczba rozkazów do niezbędnego minimum.

Ich liczba wynosi kilkadziesiąt, podczas gdy w

procesorach CISC sięga setek. Upraszcza to znacznie

dekoder rozkazów.-Redukcja trybów adresowania, dzięki

czemu kody rozkazów są prostsze, bardziej zunifikowane,

co dodatkowo upraszcza wspomniany wcześniej dekoder

rozkazów. Ponadto wprowadzono tryb adresowania, który

ogranicza ilość przesłań - większość operacji wykonuje się

-Klastry niezawodnościowe: pracujące jako zespół

komputerów dublujących nawzajem swoje funkcje. W

razie awarii jednego z węzłów, następuje automatyczne

przejęcie jego funkcji przez inne węzły.

2.GRID-Siatka komputerowa (ang. grid) to system,

który integruje i zarządza zasobami będącymi pod kontrolą

różnych domen (od instytucji po system operacyjny) i

połączonymi siecią komputerową, używa standardowych,

otwartych protokołów i interfejsów ogólnego

przeznaczenia (odkrywania i dostępu do zasobów,

autoryzacji, uwierzytelniania) oraz dostarcza usług

odpowiedniej jakości

3.Benchmark - test wydajności sprzętu komputerowego

lub oprogramowania.Istnieje wiele programów, które

testują różne charakterystyki sprzętu komputerowego i

oprogramowanie - moc pojedynczej maszyny, interakcje w

systemie klient-serwer (z pojedynczym lub wieloma

klientami) czy liczbę transakcji na sekundę w systemie

przetwarzania transakcyjnego

7.RISC_W związku z powyższym zaprezentowano

architekturę mikroprocesorów, w której uwzględniono

wyniki badań. Jej podstawowe cechy to:

wg schematu:

.

-Ograniczenie komunikacji pomiędzy pamięcią, a

procesorem. Przede wszystkim do przesyłania danych

pomiędzy pamięcią, a rejestrami służą dedykowane

instrukcje, które zwykle nazywają się load (załaduj z

pamięci), oraz store (zapisz do pamięci); pozostałe

instrukcje mogą operować wyłącznie na rejestrach.

Schemat działania na liczbach znajdujących się w pamięci

jest następujący: załaduj daną z pamięci do rejestru, na

zawartości rejestru wykonaj działanie, przepisz wynik z

rejestru do pamięci.

-Zwiększenie liczby rejestrów (np. 32, 192, 256, podczas

gdy np. w architekturze x86 jest zaledwie 8 rejestrów), co

również ma wpływ na zmniejszenie liczby odwołań do

pamięci.

4.LINPACK, wprowadzony przez Dongarrę, jest oparty

na bibliotece LINPACK. Mierzy on szybkość

rozwiązywania gęstego systemu równań liniowych

(typowego zadania inżynierskiego) i stanowi ważny

wskaźnik szybkości komputera mierzonej w liczbie

operacji zmiennoprzecinkowych. Benchmark jest

podstawą rankingu superkomputerów TOP500 - listy

najszybszych superkomputerów świata.

-Dzięki przetwarzaniu potokowemu (ang. pipelining)

wszystkie rozkazy wykonują się w jednym cyklu

maszynowym, co pozwala na znaczne uproszczenie bloku

wykonawczego, a zastosowanie superskalarności także na

zrównoleglenie wykonywania rozkazów. Dodatkowo czas

reakcji na przerwania jest krótszy.

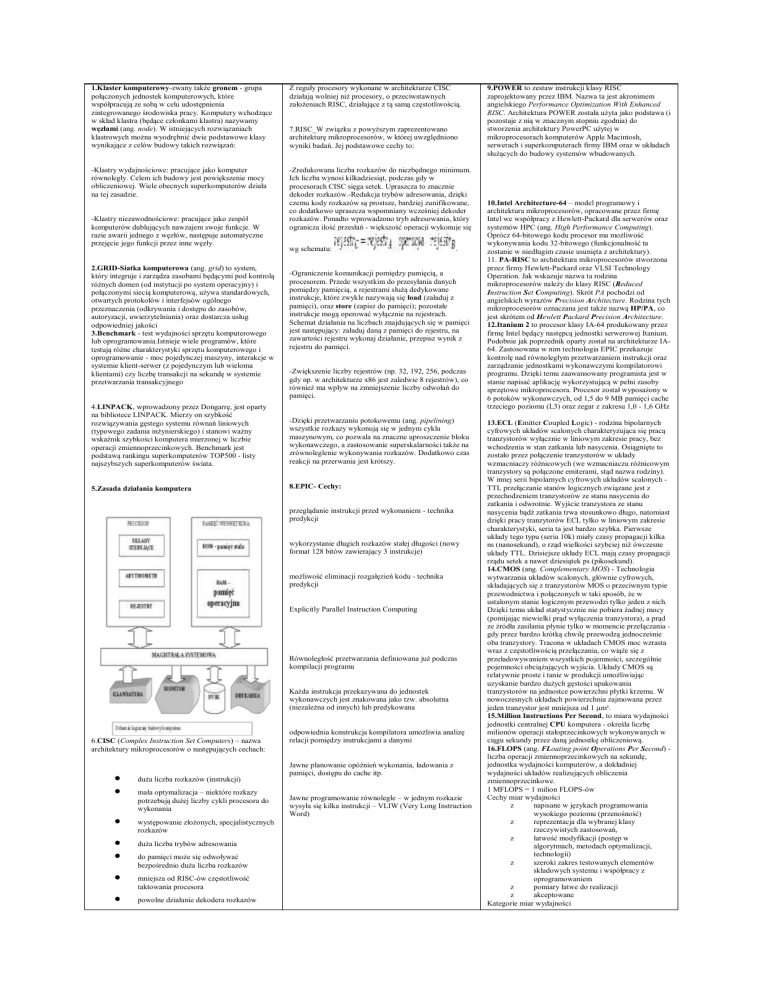

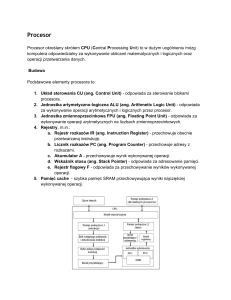

5.Zasada działania komputera

8.EPIC- Cechy:

przeglądanie instrukcji przed wykonaniem - technika

predykcji

wykorzystanie długich rozkazów stałej długości (nowy

format 128 bitów zawierający 3 instrukcje)

możliwość eliminacji rozgałęzień kodu - technika

predykcji

Explicitly Parallel Instruction Computing

Równoległość przetwarzania definiowana już podczas

kompilacji programu

Każda instrukcja przekazywana do jednostek

wykonawczych jest znakowana jako tzw. absolutna

(niezależna od innych) lub predykowana

6.CISC (Complex Instruction Set Computers) – nazwa

architektury mikroprocesorów o następujących cechach:

duża liczba rozkazów (instrukcji)

mała optymalizacja – niektóre rozkazy

potrzebują dużej liczby cykli procesora do

wykonania

występowanie złożonych, specjalistycznych

rozkazów

duża liczba trybów adresowania

do pamięci może się odwoływać

bezpośrednio duża liczba rozkazów

mniejsza od RISC-ów częstotliwość

taktowania procesora

powolne działanie dekodera rozkazów

odpowiednia konstrukcja kompilatora umożliwia analizę

relacji pomiędzy instrukcjami a danymi

Jawne planowanie opóźnień wykonania, ładowania z

pamięci, dostępu do cache itp.

Jawne programowanie równoległe – w jednym rozkazie

wysyła się kilka instrukcji – VLIW (Very Long Instruction

Word)

9.POWER to zestaw instrukcji klasy RISC

zaprojektowany przez IBM. Nazwa ta jest akronimem

angielskiego Performance Optimization With Enhanced

RISC. Architektura POWER została użyta jako podstawa (i

pozostaje z nią w znacznym stopniu zgodnia) do

stworzenia architektury PowerPC użytej w

mikroprocesorach komputerów Apple Macintosh,

serwerach i superkomputerach firmy IBM oraz w układach

służących do budowy systemów wbudowanych.

10.Intel Architecture-64 – model programowy i

architektura mikroprocesorów, opracowane przez firmę

Intel we współpracy z Hewlett-Packard dla serwerów oraz

systemów HPC (ang. High Performance Computing).

Oprócz 64-bitowego kodu procesor ma możliwość

wykonywania kodu 32-bitowego (funkcjonalność ta

zostanie w niedługim czasie usunięta z architektury).

11. PA-RISC to architektura mikroprocesorów stworzona

przez firmy Hewlett-Packard oraz VLSI Technology

Operation. Jak wskazuje nazwa ta rodzina

mikroprocesorów należy do klasy RISC (Reduced

Instruction Set Computing). Skrót PA pochodzi od

angielskich wyrazów Precision Architecture. Rodzina tych

mikroprocesorów oznaczana jest także nazwą HP/PA, co

jest skrótem od Hewlett Packard Precision Architecture.

12.Itanium 2 to procesor klasy IA-64 produkowany przez

firmę Intel będący następcą jednostki serwerowej Itanium.

Podobnie jak poprzednik oparty został na architekturze IA64. Zastosowana w nim technologia EPIC przekazuje

kontrolę nad równoległym przetwarzaniem instrukcji oraz

zarządzanie jednostkami wykonawczymi kompilatorowi

programu. Dzięki temu zaawansowany programista jest w

stanie napisać aplikację wykorzystującą w pełni zasoby

sprzętowe mikroprocesora. Procesor został wyposażony w

6 potoków wykonawczych, od 1,5 do 9 MB pamięci cache

trzeciego poziomu (L3) oraz zegar z zakresu 1,0 - 1,6 GHz

13.ECL (Emitter Coupled Logic) - rodzina bipolarnych

cyfrowych układów scalonych charakteryzująca się pracą

tranzystorów wyłącznie w liniowym zakresie pracy, bez

wchodzenia w stan zatkania lub nasycenia. Osiągnięte to

zostało przez połączenie tranzystorów w układy

wzmacniaczy różnicowych (we wzmacniaczu różnicowym

tranzystory są połączone emiterami, stąd nazwa rodziny).

W innej serii bipolarnych cyfrowych układów scalonych TTL przełączanie stanów logicznych związane jest z

przechodzeniem tranzystorów ze stanu nasycenia do

zatkania i odwrotnie. Wyjście tranzystora ze stanu

nasycenia bądź zatkania trwa stosunkowo długo, natomiast

dzięki pracy tranzytorów ECL tylko w liniowym zakresie

charakterystyki, seria ta jest bardzo szybka. Pierwsze

układy tego typu (seria 10k) miały czasy propagacji kilka

ns (nanosekund), o rząd wielkości szybciej niż ówczesne

układy TTL. Dzisiejsze układy ECL mają czasy propagacji

rządu setek a nawet dziesiątek ps (pikosekund).

14.CMOS (ang. Complementary MOS) - Technologia

wytwarzania układów scalonych, głównie cyfrowych,

składających się z tranzystorów MOS o przeciwnym typie

przewodnictwa i połączonych w taki sposób, że w

ustalonym stanie logicznym przewodzi tylko jeden z nich.

Dzięki temu układ statystycznie nie pobiera żadnej mocy

(pomijając niewielki prąd wyłączenia tranzystora), a prąd

ze źródła zasilania płynie tylko w momencie przełączania gdy przez bardzo krótką chwilę przewodzą jednocześnie

oba tranzystory. Tracona w układach CMOS moc wzrasta

wraz z częstotliwością przełączania, co wiąże się z

przeładowywaniem wszystkich pojemności, szczególnie

pojemności obciążających wyjścia. Układy CMOS są

relatywnie proste i tanie w produkcji umożliwiając

uzyskanie bardzo dużych gęstości upakowania

tranzystorów na jednostce powierzchni płytki krzemu. W

nowoczesnych układach powierzchnia zajmowana przez

jeden tranzystor jest mniejsza od 1 µm².

15.Million Instructions Per Second, to miara wydajności

jednostki centralnej CPU komputera - określa liczbę

milionów operacji stałoprzecinkowych wykonywanych w

ciągu sekundy przez daną jednostkę obliczeniową.

16.FLOPS (ang. FLoating point Operations Per Second) liczba operacji zmiennoprzecinkowych na sekundę,

jednostka wydajności komputerów, a dokładniej

wydajności układów realizujących obliczenia

zmiennoprzecinkowe.

1 MFLOPS = 1 milion FLOPS-ów

Cechy miar wydajności

z

napisane w językach programowania

wysokiego poziomu (przenośność)

z

reprezentacja dla wybranej klasy

rzeczywistych zastosowań,

z

łatwość modyfikacji (postęp w

algorytmach, metodach optymalizacji,

technologii)

z

szeroki zakres testowanych elementów

składowych systemu i współpracy z

oprogramowaniem

z

pomiary łatwe do realizacji

z

akceptowane

Kategorie miar wydajności

syntetyczne miary wydajności

(podstawowe operacje) - Dhrystone i

Whetstone

z

jądra programowe (kernels) wybrane

fragmenty rzeczywistych programów, m.in.

Livermore Fortran Kernels i NAS Kernel

Benchmark Program

z

algorytmy - programy testowe, np.

LINPACK

z

aplikacje (kompletne) (fizyka, chemia lub

wspomaganie zarządzania), np. Perfect

Benchmarks, ParkBench, z rodziny SPEC,

SAP, NotesBench i Baan

z

specyfikacje - stanowią zbiór wymagań

funkcjonalnych realizowanych przy

dowolnej implementacji sprzętowej i

programowej, np. miary z rodziny TPC

Miary syntetyczne

z

z

z

Whetstone (1976) obliczenia numeryczne;

wywołania funkcji z biblioteki

matematycznej (np. sin(.), exp(.)); Algol i

Pascal

Dhrystone (1984) - zastosowania

nienumeryczne stałoprzecinkowe (instr.

warunkowe i wywołania procedur), systemy

operacyjne, kompilatory, czy edytory; ADA

iC

shifter), który do tej pory był obecny w każdym procesorze

serii x86, począwszy od modeli 80386. Układ taki można

znaleźć również w procesorach Athlon i Hammer.

20.Centrino (także zwane Centrino Mobile Technology Mobilna Technologia Centrino) jest inicjatywą

marketingową firmy Intel, zawierającą połączenie CPU,

chipsetu płyty głównej i interfejsu sieci bezprzewodowej w

formie komputera przenośnego. Rozwiązanie to pozwoliło

na uzyskanie ponad dwukrotnej oszczędności energii

zużywanej przez dotychczasowe układy zestawów

przenośnych firmy Intel.

27.SMP (ang. Symmetric Multiprocessing, przetwarzanie

symetryczne) - architektura komputerowa, która pozwala

na znaczne zwiększenie mocy obliczeniowej systemu

komputerowego poprzez wykorzystanie 2 lub więcej

procesorów do jednoczesnego wykonywania zadań.

W architekturze SMP każdy procesor może zostać

przypisany do wykonywania każdego zadania, tak aby

wyrównać obciążenie ("obowiązki" są dzielone "po

równo"). W architekturze SMP procesory te współdzielą

zasoby pamięci oraz wejścia/wyjścia przy pomocy

magistrali.

21.MD Opteron

Opteron to pierwszy procesor firmy AMD serii K8 w

architekturze AMD64.

Stosowany przede wszystkim do serwerów oraz do

klastrów obliczeniowych. Architektura procesora Opteron

wprowadziła kilka nowości: m.in. każdy procesor ma

własny kontroler pamięci, dzięki czemu chipsety płyt

głównych dla tych komputerów będą mniej złożone.

Oprócz tego w komputerach wieloprocesorowych można

uzyskać większą wydajność.

17.Architektura Intel Netburst Microarchitecture, w

firmie Intel oznaczana jako P68, jest spadkobiercą

mikroarchitektury P6 linii x86 procesorów Intela.

Pierwszym rdzeniem korzystającym z tej

mikroarchitektury był Williamette, który na rynku pojawił

się pod koniec roku 2000. Rdzeń stanowił podstawę

pierwszych procesorów serii Pentium 4; wszystkie dalsze

układy z tej serii również korzystały z architektury

NetBurst. W roku 2001 Intel zaprezentował rdzeń Foster,

w którym ta architektura również znalazła swoje miejsce.

W konsekwencji tych działań, NetBurst pojawił się

również w linii procesorów Xeon, podobnie, jak ma to

miejsce w przypadku procesorów Celeron, pochodzących

od Pentium 4.

22.High Performance Computing?

18.Hyper Pipelined Technology

Współbieżność i przetwarzanie równoległe

Intel wybrał tę nazwę do określenia dwudziestoetapowych

potoków rdzenia Williamette. Był to znaczny wzrost w

porównaniu do 10 etapów w potokach procesorów

Pentium III. Architektura rdzenia Prescott, jak dotąd

ostatnia w linii procesorów Pentium 4, wyposażona jest w

potoki o długości 31 etapów. Mimo że dłuższe potoki

obarczone są pewnymi wadami, wśród których główną jest

zredukowana liczba instrukcji wykonywanych w jednym

cyklu procesora (IPC), taka liczba pozwala na stosowanie

wyższego taktowania procesora, co równoważy straty

spowodowane redukcją IPC. Mniejsza liczba IPC jest

pośrednią konsekwencją głębokości potoku - kwestią

kompromisu projektowego (mała liczba długich potoków

charakteryzuje się mniejszą IPC, niż większa liczba

krótkich potoków. Kolejną niedogodnością związaną ze

zwiększoną liczbą etapów potoku jest zwiększenie liczby

kroków, które trzeba pokonać wstecz, by dotrzeć do

zdarzenia, w którym mechanizm przewidywania

rozgałęzień popełnił błąd. Zwiększa to naturalnie straty

spowodowane błędem rozgałęzienia. By zrównoważyć te

straty, Intel opracował mechanizm "Rapid Execution

Engine" i zainwestował wiele środków w technologię

przewidywania rozgałęzień. Według zapewnień firmy,

pozwoliło to zmniejszyć liczbę błędów w

przewidywaniach o 33% w stosunku do Pentium III. [1]

Współbieżność to jedno z podstawowych podejść przy

budowie wydajnych systemów:

-Przetwarzanie, które ustala poziom nieosiągalny

wcześniej

-Przetwarzanie, które może być osiągnięte przez więcej niż

pojedynczy procesor, komputer czy serwer.

-Przetwarzanie wymagające specjalnej optymalizacji do

osiągnięcia maksymalnej wydajności, pod względem mocy

obliczeniowej.

Ważną rzeczą jest wykorzystanie wielowątkowości przez

programy komputerowe (oraz obsługa wielowątkowości

przez system operacyjny) - upraszcza to możliwość

"podzielenia" procesu dla kilku procesorów. Szczególną

korzyść z przetwarzania równoległego czerpią aplikacje do

renderingu i edycji wideo, małą natomiast pakiety biurowe

czy gry.

28.Komputery masywnie równoległe (ang. Massively

Parallel Processors - MPP). Rodzaj architektury

komputerowej. Jej zadaniem jest umożliwienie

przetwarzania współbieżniego (jednoczesnego) na wielu

procesorach. Do naistotniejszych realizowanych funkcji

należą:

--zarządzanie przydziałem zasobów komputera

równoległego do procesów i organizacja komunikacji

między procesami;

-szeregowanie zadań (procesów) w czasie i przestrzeni;

-zarządzanie pamięcią wirtualną;

-rekonfiguracja systemu i redystrybucja zasobów między

procesami w przypadku awarii jednego z węzłów.

19.Rapid Execution Engine

W przypadku tej technologii, jednostki arytmetycznologiczne (ALU) procesora pracują z podwojoną

częstotliwością rdzenia. Oznacza to, ze w procesorze o

taktowaniu rzędu 3,5 GHz, jednostki ALU osiągają

efektywne taktowanie rzędu 7 GHz. Powodem

wprowadzenia takiego rozwiązania jest chęć nadrobienia

strat spowodowanych niską liczbą IPC. Dodatkowo, takie

rozwiązanie znacznie zwiększa wydajność procesora w

operacjach na liczbach całkowitych. Wadą rozwiązania

Rapid Execution Engine jest spowolnienie wykonywania

pewnych instrukcji (i to zarówno spowolnienie

rzeczywiste, jak i względne), co z kolei powoduje

problemy przy optymalizacji. Przykładem są operacje

przesunięcia i obrotu, cierpiące z powodu braku

kombinacyjnego układu przesuwającego (ang. barrel

Współbieżność: Przetwarzanie gdzie wiele zadań jest

realizowanych w tym samym czasie.

Współbieżność może być używana na wiele sposobów:

Współbieżność jest jednym ze sposobów na ukrycie

opóźnień przez większość współczesnych Systemów

Operacyjnych

Współbieżność wspólnie z redundancją są używane do

budowy systemów Fault Tolerance.

Przetwarzanie równoległe wykorzystuje współbieżność do

obniżenia czasu wykonywania.

23.SISD Jest to architektura klasycznego komputera

sekwencyjnego, zawierającego jeden procesor i jeden blok

pamięci operacyjnej. Ciąg instrukcji wykonywany jest

sekwencyjnie. Architektura taka może zawierać również

pewne elementy równoległości, jak np. przetwarzanie

potokowe (ang. pipelining). Procesor może się składać z

kilku jednostek przetwarzających, jednak wszystkie te

jednostki podlegają jednej jednostce sterującej procesora.

Również jeżeli komputer składa się z kilku procesorów,

ale wykonują one niezależne od siebie programy, to

możemy traktować go jako zestaw maszyn SISD.

24.Single Instruction/Multiple Data (SIMD) to rodzaj

instrukcji procesora, które wykonują tę samą operację na

wielu danych.

25.MIMD (ang. Multiple Instruction Multiple Data) wiele strumieni instrukcji, wiele strumieni danych.

26.MISD (ang. Multiple Instruction Single Data) - wiele

strumieni instrukcji, jeden strumień danych.

29.Non-Uniform Memory Access(NUMA) - architektura

komputerowa, służąca do przetwarzania

współbieżnego.Architektura NUMA charakteryzuje się

tym, że udostępnia użytkownikowi spójną logicznie

przestrzeń adresową, chociaż pamięć jest fizycznie

podzielona. Komputery zbudowane w tej architekturze

posiadają wiele procesorów.

Niejednorodność w dostępie do pamięci polega na tym, że

dany procesor szybciej uzyskuje dostęp do swojej lokalnej

pamięci, niż do pamięci pozostałych procesorów lub

pamięci współdzielonej.