PROJEKTOWANIE

SYSTEMÓW

KOMPUTEROWYCH

WYKŁAD NR 2

PROCESORY KOMPUTEROWE

dr Artur Woike

Historia

mikroprocesorów

Procesor Viatron

• Termin „mikroprocesor” został wprowadzony przez

amerykańską firmę Viatron Computer Systems

(założona w 1967 r., zbankrutowała w 1971 r.).

• W 1968 r. stworzyła ona mały komputer o nazwie

System 21.

• Podstawowy zestaw składał się z mikroprocesora,

pamięci RAM, klawiatury, panelu kontrolnego,

9” monitora CRT i maksymalnie dwóch urządzeń

peryferyjnych (np. czytnika/perforatora kart,

kasetowego napędu magnetycznej pamięci

taśmowej).

Procesor Four-Phase Systems Inc.

• Four-Phase Systems Inc. była amerykańską firmą

komputerową założoną w 1969 r. (w latach 19811982 wykupiona przez Motorolę).

• W 1970 r. zaprojektowała ona 8-bitowy moduł

o nazwie AL-1.

• AL-1 zawierał osiem rejestrów i jedną jednostkę

arytmetyczno-logiczną.

• Z połączenia trzech modułów AL-1, trzech modułów

pamięci ROM i trzech układów „random logic”

powstawał 24-bitowy mikroprocesor.

• W 1995 r. Lee Boysal (twórca AL-1) zmontował

na potrzeby eksperymentu procesowego system

komputerowy zawierający pojedynczy moduł AL-1

jako mikroprocesor, moduł pamięci ROM, moduł

pamięci RAM i moduł I/O.

Grumman F-14 Tomcat

• Jest to ponaddźwiękowy, 2-miejscowy, 2-silnikowy

samolot myśliwski o zmiennej geometrii skrzydeł.

• Oblatany 21.12.1970 r., w użyciu od 1974 do 2006 r.

Garret AiResearch MP944

• Początki firmy Garret AiReseaech sięgają 1936 r.

• Firma wielokrotnie zmieniała nazwę (obecnie część

koncernu Honeywell International, Inc.), ale zawsze

zajmowała się techniką lotniczą.

• MP944 jest to mikroprocesor obsługujący centralę

aerometryczną w myśliwcu F-14 Tomcat.

• Prace projektowe rozpoczęto na zamówienie

Marynarki Wojennej USA w 1968, a zakończono

w 1970 r.

• MP944 był 20-bitowym układem obsługującym

przetwarzanie potokowe.

• W 1971 r. Ray Holt (jeden z twórców MP944) opisał

ten układ w artykule do branżowego czasopisma

„Computer Design”.

• Z uwagi na znaczne zaawansowanie konstrukcji

artykuł i projekt utajniono aż do 1997 r.

Texas Instruments TMS1000

•

•

•

•

•

Firmę Texas Instruments założono w 1951 r.

TMS1000 został zaprojektowany w 1971 r.

Oficjalnie zaprezentowany 17.09.1971 r.

Produkowany w latach 1974-1981.

Jest to pierwszy jednoukładowy komputer (pojedynczy

układ scalony zawiera procesor, pamięć RAM, pamięć

ROM, układy I/O oraz zegar taktujący).

• Texas Instruments posiada patent na mikroprocesor

(od 1973 r.) i na mikrokomputer jednoukładowy

(od 1978 r.).

• Po raz pierwszy wykorzystany

w kalkulatorze SR-16.

• Parametry techniczne:

•

•

•

•

•

•

Procesor 4-bitowy;

Częstotliwość taktowania 300 kHz;

Wyprodukowany w technologii 8 m;

32 B pamięci RAM i 1024 B pamięci ROM;

42 rozkazy;

8 rejestrów (dwa 6-bitowe, cztery 4-bitowe, jeden 2bitowy i jeden 1-bitowy).

Intel 4004

• Firma Intel (nazwa pochodzi od słów Integrated

Electronics) została założona w 1968 r.

• W 1969 r. firma Busicom (japoński producent

kalkulatorów) zamówił projekt układu scalonego

dla wysoko wydajnych kalkulatorów.

• Marcian Hoff, inżynier przydzielony do prac

projektowych, zaproponował realizację układu

w postaci 4-składnikowej architektury.

• W skład zaproponowanej architektury wchodziły

następujące moduły:

•

•

•

•

4-bitowa programowalna jednostka obliczeniowa;

Układ pamięci ROM do przechowywania programu;

Układ pamięci RAM do przechowywania danych;

Proste urządzenie I/O.

• Początkowo Busicom odrzucił propozycję takiego

układu i zażądał zaprojektowania układu scalonego

dedykowanego dla kalkulatorów.

• Intel 4004 został przedstawiony 15.11.1971 r.

• Był produkowany od 1971 do 1981 r.

• Jest uznawany za pierwszy powszechnie dostępny

mikroprocesor.

• Parametry techniczne:

•

•

•

•

•

•

•

•

Procesor 4-bitowy;

Zbudowany z około 2300 tranzystorów;

Wyprodukowany w technologii 10 m;

Powierzchnia kości 12 mm2;

Szybkość około 92 kIPS;

Maksymalna częstotliwość taktowania 740 kHz;

Oddzielna pamięć dla danych i programu;

Pojedyncza multipleksowana szyna dla transferu 12bitowych adresów, 8-bitowych instrukcji i 4-bitowych

słów danych;

• Możliwość zaadresowania 640 B pamięci RAM i 4096 B

pamięci ROM;

• 46 rozkazów (41 rozkazów 8-bitowych i 5 rozkazów 16bitowych);

• 16 rejestrów 4-bitowych.

Budowa i zasada

działania procesora

Procesor i jego zadania

• Procesor jest inaczej nazywany centralną jednostką

wykonawcza (Central Processing Unit, CPU).

• Jest to układ scalony, którego przeznaczeniem jest

wykonywanie rozkazów.

• Procesor nadzoruje pracę wszystkich podzespołów

komputera.

• Zazwyczaj jest zorganizowany w postaci zespołu

współpracujących ze sobą bloków funkcjonalnych.

• Procesor pobiera wykonywane instrukcje z pamięci.

• Często przed wykonaniem instrukcje złożone

są rozkładane na ciągi rozkazów elementarnych

(mikrooperacji).

• Procesor rozdziela wykonanie przetwarzanych

rozkazów na swoje poszczególne podjednostki.

• Przykładowe rozkazy jakie mogą wykonywać

procesory:

•

•

•

•

•

Działania arytmetyczne;

Działania logiczne;

Instrukcje skoków;

Instrukcje warunkowe;

Kopiowanie danych (np. rejestr-rejestr, pamięć-rejestr).

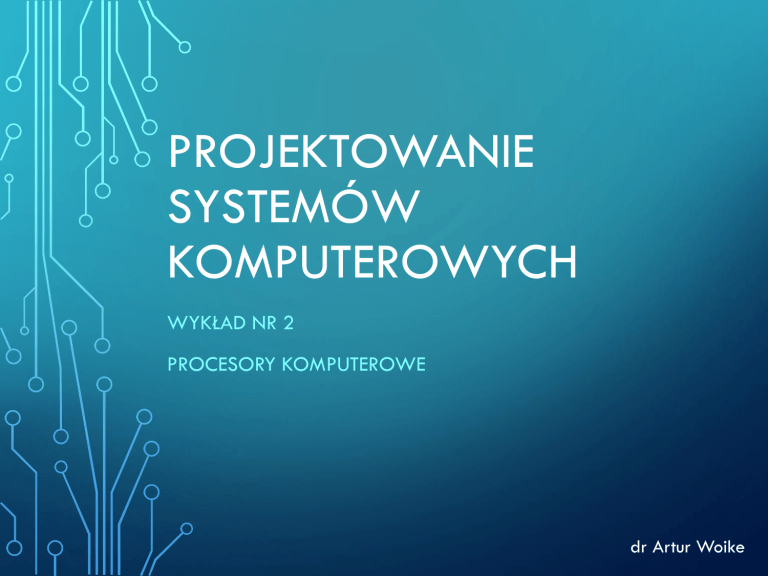

• Podstawowe moduły składowe procesora:

• Jednostka arytmetyczno-logiczna (Arithmetic Logic Unit,

ALU) – wykonuje podstawowe operacje logiczne oraz

działania na liczbach całkowitych.

• Rejestry (Registers) – przechowują np. adresy komórek

pamięci, dane, wyniki obliczeń, informacje o stanie

procesora.

• Jednostka zmiennoprzecinkowa (Floating-Point Unit,

FPU) – wykonuje obliczenia numeryczne na liczbach

zmiennoprzecinkowych oraz niektóre inne złożone

instrukcje obliczeniowe.

• Układy sterujące – zajmują się np. dekodowaniem

instrukcji, dostarczaniem danych z pamięci dla ALU i FPU,

przekazywaniem do pamięci wyników obliczeń.

• Pamięć podręczna (Cache) – przyspiesza dostęp

do pamięci komputera.

Schemat blokowy procesora

• Blok komunikacyjny (Bus Unit, BU):

• Potocznie nazywany szyną procesora;

• Odpowiada za współpracę z pamięcią przechowującą

instrukcje, dane i wyniki obliczeń.

• Zazwyczaj składa się z dwóch oddzielnych magistrali

dla adresów i danych.

• Zarządzanie szyną adresową i szyną danych odbywa się

za pomocą dodatkowych sygnałów kontrolnych

i sterujących.

• Kolejka rozkazowa (Prefetch):

• Aby zapewnić płynną pracę procesora kod programu jest

pobierany w większych porcjach.

• Wstępnie pobrane dane do wykonania oczekują

na wykonanie w kolejce.

• Oczekujący na wykonanie kod jest przechowywany

w postaci zakodowanej.

• Dekoder instrukcji (Instruction Unit, IU):

• Instrukcje przeznaczone do wykonania są dekodowane

w bloku dekodera.

• Często dekoder jest wspomagany przez dedykowaną

podręczną pamięć stałą ROM zawierającą słownik

tłumaczący zdekodowane instrukcje na sekwencje

elementarnych rozkazów.

• Jednostka wykonawcza (Execution Unit, EU):

• Zdekodowane rozkazy przekazywane są do jednostki

wykonawczej w celu ich wykonania.

• Rozkazy operujące na liczbach stałoprzecinkowych

(całkowitych) są przekazywane do wykonania w module

ALU.

• Blok sterujący (Control Unit, CU) odpowiada

za sterowanie pracą modułu ALU.

• Rozkazy operujące na liczbach zmiennoprzecinkowych

są przekazywane do wykonania w module FPU.

• Jednostka adresowania (Adressing Unit, AU):

• Rozkazy często zawierają odwołania do pamięci

operacyjnej (np. argumenty rozkazu).

• Wyniki instrukcji często trzeba zapisać w ściśle

określonym obszarze pamięci.

• W takich sytuacjach za dostęp do pamięci odpowiada

właśnie jednostka adresowania.

• Ze względu na konieczność stosowanie w dostępie

do pamięci dodatkowych mechanizmów technicznych

(np. stronicowania i segmentacji) potrzebna jest

wyspecjalizowana podjednostka zarządzania pamięcią

(Memory Management Unit, MMU).

Uwagi:

• Obecnie schemat może ulegać stopniowemu rozmyciu.

• Dla współczesnych mikroprocesorów nie zawsze daje się

zastosować tak wyraźny podział na wyspecjalizowane

bloki funkcjonalne.

Jednostka arytmetyczno-logiczna

• Jednostka arytmetyczno-logiczna (Arithmetic Logic

Unit, ALU) jest centralnym blokiem procesora.

• ALU zazwyczaj wykonuje następujące rozkazy:

• Operacje arytmetyczne (np. dodawanie, odejmowanie,

negacja liczby, zwiększanie lub zmniejszanie liczby o 1,

mnożenie, dzielenie, dzielenie modulo).

• Przesunięcia bitowe (np. o stałą lub zmienną liczbę

bitów).

• Operacje logiczne (np. AND, OR, NOT, XOR).

Oznaczenia:

• A, B – operandy (argumenty);

• F – wejście z jednostki kontrolnej CU;

• R – wyjście;

• D – status wyjścia.

Jednostka zmiennoprzecinkowa

• Pierwowzorem jednostki zmiennoprzecinkowej

(Floating-Point Unit, FPU) jest koprocesor.

• Koprocesor jest układem, którego zadaniem jest

wspomaganie pracy procesora przy wykonywaniu

obliczeń numerycznych.

• Koprocesory w formie zewnętrznych układów były

stosowane do architektury 80486 włącznie.

• Układ procesor-koprocesor jest traktowany jako

pojedynczy procesor o zwiększonej liczbie

dostępnych rejestrów, rozkazów i typów danych .

• Koprocesory nie mogą pracować samodzielnie

(bez procesora głównego).

• Począwszy od architektury 80486 rolę układu

zewnętrznego koprocesora przejęły wbudowane

w układ procesora jednostki zmiennoprzecinkowe.

• Jednostki zmiennoprzecinkowe zajmują się nie tylko

operacjami zmiennoprzecinkowymi, ale również

innymi bardziej skomplikowanymi obliczeniami

(np. operacjami wektorowymi).

Pamięć podręczna

• Najszybszą dostępną dla procesora pamięcią

są jego wewnętrzne rejestry.

• Procesory o coraz większych częstotliwościach

taktowania do optymalnej pracy wymagają coraz

szybszych pamięci komputerowych.

• Stosowana obecnie pamięć operacyjna typu DRAM

(Dynamic Random Access Memory) nie może

sprostać zapotrzebowaniu na dane współczesnych

procesorów.

• Pamięć podręczna (Cache) jest buforem pomiędzy

procesorem a pamięcią operacyjną

• Jest to pamięć o krótkich czasach dostępu.

• Duża i tania pamięć operacyjna jest wspomagana

przez szybką i małą (więc nie aż tak drogą) pamięć

podręczną.

• Rozwinięciem idei pamięci podręcznej jest kaskada

pamięci podręcznych.

• W kaskadzie każdy kolejny poziom (Level) jest

większy i wolniejszy od poprzedniego.

• W praktyce obecnie używa się maksymalnie trzech

poziomów pamięci podręcznej.

• Efektywne wykorzystanie pamięci podręcznej jest

możliwe dzięki dużej spójności kodu programów

przetwarzanych przez mikroprocesory.

• W procesorach opartych na architekturze NetBurst

(np. Pentium 4, Pentium D) nie było klasycznej

pamięci podręcznej poziomu 1 (zamiast tego była

implementowana pamięć podręczna dla wcześniej

zdekodowanych mikrooperacji).

• Czasami uwzględnia się pamięć podręczną

mikrooperacji jako poziom 0.

• Obecnie często pamięć podręczna poziomu 1 jest

rozdzielona na dwie oddzielne części (dla instrukcji

i dla danych).

• Pamięć podręczna poziomu 2 zazwyczaj jest

zunifikowana.

• Pamięć podręczna poziomu 3 najczęściej jest

wspólna dla wszystkich rdzeni procesora.

• Wpływ wielkości pamięci podręcznej na wydajność

jest złożony.

Techniki przetwarzania

rozkazów

Architektura typu RISC

• Termin RISC (Reduced Instruction Set Computer)

powstał w trakcie prac nad projektem procesora

IBM 801.

• Prace nad projektem IBM 801 rozpoczęto w 1974 r.

• IBM 801 osiągał wydajność rzędu 15 MIPS.

• Architektura RISC charakteryzuje się ograniczeniem

listy rozkazów procesora do niewielkiej liczby

bardzo szybko wykonywanych operacji.

• W założeniu większość rozkazów jest realizowanych

sprzętowo, a więc można ograniczyć konieczność

stosowania dekodera instrukcji.

• Szybkość przetwarzania rozkazów RISC jest duża.

• Tłumaczenie programu z instrukcji złożonych

na rozkazy RISC jest wykonywane przez kompilator.

• Procesor musi pobrać wcześniej przetłumaczony

kod programu z pamięci komputera.

• W naturalny sposób pojawia się zapotrzebowanie

na dużą przepustowość magistrali procesor-pamięć.

Architektura typu CISC

• Architektura CISC (Complex Instruction Set

Computer) jest stosowana np. we wszystkich

wersjach architektury x86 firmy Intel.

• Procesory projektowane w architekturze CISC

realizują coraz więcej rozkazów, które mogą być

coraz bardziej skomplikowane.

• Pojedynczy rozkaz może wymagać wykonania

szeregu działań.

• Czas wykonywania rozkazu CISC może być bardzo

długi (np. kilkadziesiąt cykli zegara).

• Programy napisane dla procesorów CISC mają

zwarty kod.

• Tłumaczenie programu na rozkazy wykonuje

dekoder, który przy takim podejściu musi być

obszerny.

• Pobieranie kodu programu przez procesor jest

ułatwione (w stosunku do architektury RISC).

Obecne architektury RISC i CISC

• Początkowo architektury RISC i CISC stanowiły

odrębne kategorie.

• Obecnie podział między nimi ulega rozmyciu.

• Procesory RISC często mają długie listy rozkazów.

• Niektóre rozkazy RISC mogą być skomplikowane.

• Obecne procesory CISC często posiadają jądro

pracujące w trybie RISC.

Przetwarzanie potokowe

• Przetwarzanie potokowe polega na podzieleniu

czasu pracy procesora nad pojedynczym rozkazem

na kilka faz (stopni).

• Potok (Pipeline) w tym samym czasie pracuje nad

wykonaniem kilku rozkazów.

• Każdy rozkaz znajduje się w innej fazie wykonania.

• W każdym cyklu zegara taktującego zostaje

wykonany 1 rozkaz.

• Liczba stopni potoku (Pipeline Stages) jest

nazywana głębokością potoku.

• Podczas przetwarzania potokowego mogą się

pojawić dwie sytuacje wyjątkowe:

• Wstrzymanie potoku (np. na skutek wystąpienia

wzajemnej zależności rozkazów lub konfliktu rejestrów).

• Oczyszczenie potoku (np. na skutek wystąpienia błędu).

• Zazwyczaj wyróżniamy 4 podstawowe fazy potoku:

•

•

•

•

Pobranie (Fetch, F);

Dekodowanie (Decode, D);

Wykonanie (Execute, E);

Zakończenie (Write-Back, WB).

• W konkretnej implementacji przetwarzania

potokowego podstawowe fazy mogą być

podzielone na mniejsze bardziej uszczegółowione

stopnie.

Przetwarzanie 64-bitowe

• O typie procesora zazwyczaj decyduje rozmiar

rejestrów ogólnego przeznaczenia.

• Niektóre procesory mają część rejestrów większych

od rejestrów ogólnego przeznaczenia.

• Współczesny rynek procesorów przeznaczonych

dla komputerów osobistych jest zdominowany

przez dwie firmy:

• Intel Corporation (założona w 1968 r.);

• Advanced Micro Devices (założona w 1969 r.).

• Obie firmy na przełomie XX i XXI w. prowadziły

prace koncepcyjne nad 64-bitową architekturą

dla mikroprocesorów.

• Intel opracował architekturę IA-64.

• Pierwsze procesory oparte na architekturze IA-64

(Intel Itanium) zadebiutowały na rynku w 2001 r.

• AMD opracowało architekturę AMD64 (oznaczaną

również x86-64), będącą rozszerzeniem 32-bitowej

architektury x86-32 firmy Intel).

• Pierwsze procesory oparte na architekturze AMD64

(procesory AMD K8, obecnie AMD Family 0Fh)

pojawiły się na rynku w 2003 r.

Architektura IA-64

Założenia koncepcyjne:

• Architektura x86 jest ograniczona.

• Zgodność z poprzednimi generacjami mikroprocesorów

i dostępnym dla nich oprogramowaniem komplikuje

strukturę i działanie nowych mikroprocesorów.

• Wsteczna zgodność utrudnia innowacyjność.

• Dla komputerów o dużej wydajności będzie dostępne

dedykowane dla nich oprogramowanie skompilowane

w sposób optymalny.

• Nie będzie dużego zapotrzebowania na wykonywanie

aplikacji skompilowanych dla architektury x86-32.

• Komputery o dużej wydajności nie muszą wykonywać

powszechnie dostępnego oprogramowania w sposób

maksymalnie wydajny.

• Przeciętny użytkownik nie potrzebuje możliwości danych

przez przetwarzanie 64-bitowego.

• Przeciętny użytkownik nie będzie zainteresowany

zakupem 64-bitowego mikroprocesora.

Efekt:

• Architektura IA-64 nie jest oparta na architekturze

x86-32.

• Architektura IA-64 nie jest zgodna z architekturą x86-32.

• Procesory produkowane w oparciu o architekturę IA-64

posiadały dodatkowy moduł sprzętowy emulujący

działanie procesora x86-32.

• Niewielka wydajność w aplikacjach przeznaczonych

dla architektury x86-32.

Architektura AMD64

Założenia koncepcyjne:

• Architektura x86-32 ma swoje ograniczenia.

• Dalszy rozwój architektury x86-32 pozwoli wiele z nich

usunąć.

• Zgodność z poprzednimi generacjami mikroprocesorów

i dostępnym dla nich oprogramowaniem jest zaletą.

• Przejście na w pełni 64-bitowe oprogramowanie będzie

dokonywane bardzo powoli.

• Komputery o dużej wydajności muszą jeszcze (przez jakiś

czas) wykonywać kod powszechnie dostępnych aplikacji

skompilowanych dla architektury x86-32 w sposób

maksymalnie efektywny.

• Przeciętny użytkownik już niedługo zostanie postawiony

przed koniecznością wykorzystania możliwości danych

przez przetwarzanie 64-bitowe (np. w celu umożliwienia

efektywnej obsługi więcej niż 4 GB pamięci RAM).

Efekt:

• Całkowita zgodność z oprogramowaniem przeznaczonym

dla architektury x86-32.

• Brak emulacji architektury x86-32 (wbudowany tryb

Legacy Mode).

• Duża wydajność w aplikacjach przeznaczonych

dla architektury x86-32.

• Możliwość zaadresowania 1 TB pamięci RAM (przy

zastosowaniu 40-bitowej magistrali adresowej).

• Możliwość przydzielenia pojedynczemu procesowi

do 256 TB pamięci wirtualnej.

• Wbudowanie kontrolera pamięci w strukturę procesora

w celu skrócenia czasu dostępu do pamięci operacyjnej.

IA-64 czy AMD64?

• Ostatecznie na rynku komputerów osobistych

przyjęła się koncepcja firmy AMD.

• Architektura AMD64 jako rozwinięcie architektury

x86-32 ograniczyła konieczność stosowania

całkowicie nowego oprogramowania.

• Firma Intel (od zmodyfikowanej architektury

NetBurst) zaczęła wyposażać swoje procesory

w tryb zgodności z architekturą AMD64 (Enhanced

Memory 64-bit Technology, EM64T).

• Obecnie wszystkie nowe modele procesorów

są zgodne z architekturą AMD64.

Techniki przyspieszania

przetwarzania

Przetwarzanie superskalarne

• Procesor superskalarny posiada co najmniej 2

pracujące równolegle potoki.

• Równoległe potoki nie stanowią niezależnych

obiektów.

• Dołączenie drugiego i kolejnych potoków nie daje

gwarancji stałego wzrostu wydajności.

• Procesory superskalarne mogą zawierać wiele

modułów ALU i FPU.

• Niektóre potoki mogą być wyspecjalizowane

(wykonywanie wybranych rozkazów).

• FPU często traktuje się jako wyspecjalizowany

potok.

Przemianowywanie rejestrów

• Nie wszystkie rozkazy wykonywane przez procesor

dają się rozdzielić na równoległe potoki.

• Najczęstszą przyczyną konfliktów są odwołania

do tych samych rejestrów procesora.

• Przemianowywanie rejestrów (Register Renaming)

jest metodą polegającą na tymczasowym

podstawianiu dodatkowych rejestrów procesora

(pomocniczych) w sytuacji wystąpienia rozkazów

powodujących konflikt.

Przewidywanie skoków

• Do wykorzystania pełnej mocy obliczeniowej CPU

konieczny jest stały dopływ instrukcji do wykonania.

• W przypadku wystąpienia instrukcji warunkowej

nie wiadomo jak przebiegnie realizacja dalszej

części programu.

• Po rozstrzygnięciu warunku instrukcji typu „if”

(zazwyczaj w okolicach środka potoku) może się

okazać, że potok zawiera i przetwarza rozkazy

z niewłaściwej gałęzi kodu programu.

• Im dłuższy potok, tym więcej niewłaściwych

rozkazów może w nim wystąpić.

• Oczyszczenie potoku ze zbędnych instrukcji jest

czasochłonne i jest stratą czasu procesora.

• Występują dwa podstawowe podejścia:

• Przewidywanie dalszego biegu programu (Branch

Prediction);

• Podążanie wieloma ścieżkami rozgałęzienia (Multiple

Paths of Execution).

• Prawdopodobieństwo przewidzenia właściwej

gałęzi programu jest zawsze mniejsze od 1.

• Podążanie wieloma ścieżkami wymaga powielania

wielu modułów procesora, ponadto wielokrotne

zagnieżdżenia kodu szybko mogą wyczerpać każdą

dostępną ilość zasobów sprzętowych.

• Współczesne procesory w większości korzystają

z metody Branch Prediction.

Optymalizacja kodu programu

• Optymalizacja polega na próbie dopasowania kodu

programu do architektury i konstrukcji konkretnego

procesora (lub rodziny procesorów),

• Współczesne mikroprocesory projektuje się tak,

aby zmniejszać znaczenie optymalizacji kodu.

• Obecnie kod niezoptymalizowany często może być

wykonywany niewiele wolniej niż odpowiadający

mu kod zoptymalizowany.

Zarządzanie pamięcią

operacyjną

• Procesor musi przetwarzać dane przechowywane

w pamięci operacyjnej.

• Operacje wykonywane na pamięci mają charakter

dwukierunkowy (odczyt lub zapis).

• Zapis polega na przekazania słowa danych

do magistrali danych oraz jego adresu docelowego

na magistralę adresową.

• Odczyt polega na przekazaniu magistrali adresowej

adresu położenia żądanego słowa danych oraz

pobrania tego słowa danych z magistrali danych.

Magistrale adresowe w architekturze x86:

Typ procesora

Szerokość magistrali

procesowej

Ilość możliwej do zaadresowania

pamięci

16-bitowy

20-bitowa

1 MB

16-bitowy

24-bitowa

16 MB

32-bitowy

32-bitowa

4 GB

32-bitowy

36-bitowa

64 GB

64-bitowy

40-bitowa

1 TB

Tryby pracy procesora

Tryb rzeczywisty (Real Mode):

• Procesor 32-bitowy przełącza się w stan odwzorowujący

działanie jednostki 16-bitowej.

• Nie zapewnia ochrony pamięci przed jednoczesnym

wykorzystaniem przez inny proces.

• Nie zapewnia obsługi wielozadaniowości.

• Udostępnia 1 MB przestrzeni adresowej.

Tryb chroniony (Protected Mode):

• Zaprojektowany w celu ochrony procesów pracujących

w wielozadaniowym systemie operacyjnym.

• Umożliwia udostępnienie przestrzeni adresowej większej

niż 1 MB.

• Układy sprzętowe procesora (MMU) kontrolują

odwołania do pamięci operacyjnej.

• W procesorach obsługujących mechanizm stronicowania

tryb chroniony pozwala na całkowitą separację

procesów.

Tryb wirtualny procesora 8086 (Virtual 8086 Mode):

• Pozwala na uruchamianie programów przeznaczonych

dla trybu rzeczywistego w trybie chronionym.

• Każdy program widzi oddzielny wirtualny procesor 8086

pracujący w trybie rzeczywistym.

• Mechanizmy trybu chronionego kontrolujące dostęp

do zasobów i zapobiegające konfliktom pozostają

włączone.

Stronicowanie

• Stronicowanie (Paging) pozwala na ograniczenie

i kontrolę dostępu procesów do pamięci poprzez

użycie tzw. stron (mniejszych sekcji pamięci).

• Pozwala na przydzielenie każdemu procesowi

indywidualnej wirtualnej przestrzeni adresowej.

• Umożliwia wykorzystanie większej ilości pamięci

operacyjnej niż jest fizycznie dostępne w systemie

komputerowym.

Produkcja i podstawowe

parametry procesorów

Prawo Moore’a

• Gordon Moore (jeden z założycieli firmy Intel)

w 1965 r. zaobserwował, że ekonomicznie

opłacalna liczba tranzystorów w układach scalonych

podwaja się co około 18 miesięcy.

• Liczba ta była wielokrotnie korygowana ze względu

na występowanie różnych problemów fizycznych

i technicznych.

• Obecnie przyjmuje się, że liczba tranzystorów

w mikroprocesorach podwaja się co około 24

miesiące.

• Głównym powodem dla którego zachodzi prawo

Moore’a jest ciągły postęp technologiczny

w procesach produkcyjnych mikroprocesorów.

• Pomimo ciągłego rozwoju technologicznego

występują bariery fizyczne dla szerokości ścieżek

oraz przesyłania informacji w układach scalonych.

• Przewiduje się, że prawo Moore’a przestanie

zachodzić w niedalekiej przyszłości.

• Inna popularna wersja Prawa Moore’a (tak zwane

Rozszerzone Prawo Moore’a) mówi, że moc

obliczeniowa mikrokomputerów podwaja się

co około 24 miesiące.

Proces produkcyjny procesora

Etapy produkcji procesora z tranzystorami 3D

(litografia 22 nm stosowana przez firmę Intel)

1. Piasek kwarcowy:

• Podstawowym surowcem

(dwutlenek krzemu).

jest

piasek

kwarcowy

2. Oczyszczanie:

• Krzem musi zostać oczyszczony (podgrzewa się go w celu

utworzenia siatki krystalicznej w formie cylindra).

3. Cięcie i polerowanie:

• Monokrystaliczne cylindry krzemowe są przecinane

na wafle (plastry o grubości około 1 mm) i polerowane.

4. Lakierowanie:

• Na obracający się wypolerowany wafel nanoszona jest

emulsja światłoczuła.

5. Napromieniowanie:

• Emulsja jest wielokrotnie naświetlana (za pomocą

promieni UV i przy wykorzystaniu masek) oraz częściowo

usuwana.

• Następnie następuje trawienie chemiczne krzemu

(powstaje wtedy krzemowa baza tranzystorów).

6. Implementowanie:

• Ponownie nakłada się i naświetla emulsję światłoczułą,

a następnie wafel w odpowiednich miejscach

bombarduje się jonami (co zmienia jego właściwości

przewodzące) i usuwa pozostałą część emulsji.

7. Izolowanie:

• Tranzystor (pomarańczowy) powstaje na skutek

wielokrotnego powtarzanie kroków 5 i 6.

• Po utworzeniu tranzystor jest izolowany od innych

elementów za pomocą dwutlenku krzemu (przezroczysty

czerwony).

8. Galwanizowanie:

• Podczas galwanizacji tworzone są złącza tranzystorów.

• Nadmiar miedzi zostaje spolerowany.

9. Okablowanie:

• Do układu dodaje się okablowanie (połączenia pomiędzy

tranzystorami) zbudowane z kilku warstw metali.

10. Montaż:

• Oddzielony od wafla CPU łączy się ze złączem interfejsu

płyty głównej (zielony) i pokrywą odprowadzającą ciepło

(srebrny).

Rozmiar charakterystyczny

tranzystora

• Jest to parametr techniczny zaawansowania

procesu produkcyjnego oraz gęstości upakowania

tranzystorów w układach scalonych.

• Rozmiarem charakterystycznym tranzystora jest

nazywana minimalna długość kanału tranzystora.

• Im mniejszy rozmiar charakterystyczny tym większe

możliwe upakowanie i szybkość działania.

• Rozmiar charakterystyczny dla współczesnych CPU:

• AMD – obecnie 28 nm, 14 nm planowane w 2017 r.;

• Intel – obecnie 14 nm, 10 nm planowane w 2017 r.

Częstotliwość taktowania

• Taktowanie jest sposobem sterowania pracą układu

cyfrowego.

• Polega na generowaniu i dostarczaniu przez zegar

sygnału elektrycznego (zazwyczaj prostokątnego)

o określonej częstotliwości.

• Mikroprocesor wykonuje 1 podstawową operację

w każdym pojedynczym cyklu (takcie) zegara.

• Do wykonania pojedynczego rozkazu zazwyczaj

potrzebne jest wykonanie kilku podstawowych

operacji.

• Częstotliwość taktowania procesora (Clock Rate)

to podstawowy wskaźnik szybkości z jaką procesor

wykonuje podstawowe operacje.

• Częstotliwość taktowania jest wyrażona w Hercach

(Hz), czyli liczbie cykli przypadających na 1 sekundę.

• Porównywanie współczesnych mikroprocesorów

pod względem częstotliwości taktowania zazwyczaj

nie jest miarodajne.

• Częstotliwość taktowania współczesnych CPU:

• AMD – do 4,3 GHz;

• Intel – do 4,0 GHz.

Napięcie zasilające

• Właściwe napięcie zasilania wszystkich obecnych

procesorów jest dobierane automatycznie.

• Niewielkie podniesienie napięcia zasilającego zazwyczaj

poprawia nieco stabilność pracy procesora, ale

jednocześnie powoduje wzrost poziomu temperatury

struktury półprzewodnikowej mikroprocesora.

• Obwody zasilające jądro procesora są oddzielone

od obwodów zasilających magistrale.

• Układy wytwarzające napięcie zasilania dla CPU mogą

być montowane bezpośrednio na płycie głównej lub

jako dodatkowe moduły VRM (Voltage Regulator

Module).

Współczynnik TDP

• TDP (Thermal Design Power) to ilość wydzielanego

przez mikroprocesor ciepła, którą trzeba

odprowadzić za pomocą układów chłodzenia.

• Firma Intel rozumie TDP jako moc, którą procesor

pobiera i oddaje w postaci ciepła przy obciążeniu

realnymi programami.

• AMD rozumie TDP jako teoretyczną moc jaką CPU

mógłby pobierać i oddawać w postaci ciepła.

• Współczesne procesory posiadają mechanizmy

ograniczające w razie potrzeby pobór mocy.

Gniazdo procesora

• Początkowo mikroprocesory były wlutowywane

bezpośrednio na płytę główną.

• Uniemożliwiało to wymianę CPU na inny model.

• Gniazdo procesora jest to złącze na płycie głównej

przeznaczone do montażu procesora.

• Pełni ono rolę interfejsu pomiędzy procesorem

a pozostałymi podzespołami komputera.

• Dla danego typu gniazda mogą występować pewne

charakterystyczne cechy (np. kształt, napięcie,

częstotliwość taktowania magistrali systemowej).

• Gniazda procesora stosowane w komputerach

osobistych można podzielić na dwa typy:

• Slot (szczelina);

• Socket (gniazdo).

• Obecnie używa się gniazd typu socket.

• Procesor musi być zgodny z typem gniazda (między

innymi).

• Różnice pomiędzy gniazdami mogą być bardzo

subtelne.

• Niektóre gniazda posiadają wsteczną zgodność

z poprzednimi wersjami.

• Obecne gniazda procesorów są wyposażane

w mocowania typu ZIF (Zero Insertion Force).

Dodatkowe technologie

implementowane

w procesorach

Wielordzeniowość

• Procesor wielordzeniowy posiada więcej niż jeden

rdzeń fizyczny.

• Pierwsze wielordzeniowe procesory w architekturze

x86 zostały wprowadzone w 2005 r.:

• Seria AMD Opteron;

• Seria Intel Pentium Extreme Edition.

• Dwa sposoby tworzenia CPU wielordzeniowych:

• Integracja wielu rdzeni w jeden układ scalony.

• Oddzielne kości rdzeni są połączone w jednym

opakowaniu.

• Mogą być różne metody implementacji (np. rdzenie

mogą dzielić pamięć podręczną lub nie, mogą być

takie same lub różne).

• Przyrost wydajności procesora uzyskiwany poprzez

implementację dodatkowych rdzeni zależy w dużej

mierze od dostępnego oprogramowania.

Teraflops Research Chip

• 11.02.2007 r. Intel zaprezentował działający

wielordzeniowy CPU o nazwie Teraflops Research

Chip zbudowany z 80 rdzeni zintegrowanych

w jednym układzie scalonym.

• Jego rdzenie są prostsze od rdzeni stosowanych

w obecnych mikroprocesorach.

• Każdy rdzeń posiada 2 jednostki FPU.

• Rdzenie są połączone ze sobą za pomocą routerów

(każdemu rdzeniowi jest przypisany dedykowany

router).

• Został wyprodukowany w procesie technologicznym

65 nm.

• Zbudowany z około 100 mln. tranzystorów.

• Rozmiar kości to 274,5

Teraflops Research Chip

Częstotliwość

taktowania (GHz)

Napięcie

Teoretyczna wydajność

zasilające (V) (TFLOPS)

Pobór mocy (W)

3,16 GHz

0,95 V

1,01 TFLOPS

62 W

5,1 GHz

1,2 V

1,63 TFLOPS

175 W

5,7 GHz

1,35 V

1,81 TFLOPS

265 W

Pierwszy komputer, który przekroczył w testach

barierę 1 TFLOPS, to zbudowany w 1996 r. komputer

ASCI Red (około 10000 procesorów Pentium Pro

o częstotliwości taktowania 200 MHz, pobór mocy

około 500 kW).

Wielowątkowość

• Polega na możliwości jednoczesnego wykonywania

więcej niż jednego wątku sprzętowego na jednym

fizycznym rdzeniu.

• Implementacja firmy Intel to Hyper-Threading

Technology (zaprezentowana w 2002 r.).

• HTT polega na przypisaniu przez system każdemu

fizycznemu rdzeniowi dwóch wirtualnych rdzeni

logicznych i rozdzieleniu pomiędzy nie wątków

do wykonania (jeżeli jest to możliwe).

• Obecnie AMD nie implementuje odpowiednika

technologii HTT.

• Procesory AMD (od zaprezentowanej w 2011 r.

architektury Bulldozer) korzystają z technologii

Clustered Multi-Threading (CMT).

• CMT w wersji AMD polega na wykorzystaniu

do budowy CPU modułów (każdy moduł zawiera

dwie niezależne jednostki ALU i jedną 256-bitową

jednostkę FPU zbudowaną z połączenia dwóch

jednostek 128-bitowych).

• Każdy pojedynczy moduł jest traktowany jako

dwurdzeniowy ze względu na ALU.

• W zależności od rodzaju aktualnie wykonywanego

kodu moduł jest traktowany jako jednordzeniowy

lub dwurdzeniowy ze względu na FPU

• HTT jest odmianą technologii Simultaneous MultiThreading (SMT).

• Implementacja wielowątkowości typu SMT

dla mikroprocesorów AMD jest przewidziana

na 2017 r. (w architekturze Zen).

Mostek północny i południowy

• Mostek północny (Northbridge) i południowy

(Southbridge) są dwoma najważniejszymi układami

współpracującymi z procesorem.

• Procesor jest połączony z mostkiem północnym

za pomocą szyny systemowej (Front Side Bus, FSB).

• Mostek

północny

najczęściej

odpowiada

za komunikację CPU z pamięcią RAM, szybkimi

magistralami przeznaczonymi dla kart graficznych

(np. PCI-E) i mostkiem południowym.

• Czasami układ mostka północnego zawiera

zintegrowaną w nim kartę graficzną.

• AMD począwszy od serii procesorów Athlon64

(2003 r.) integruje pewne funkcje mostka

północnego (kontroler pamięci RAM) w CPU.

• AMD od 2011 r. w serii procesorów Accelerated

Processing Unit (APU) integruje układ graficzny

w CPU.

• Intel począwszy od układów architektury Nehalem

(2008 r.) integruje układy mostka północnego

w CPU.

• W architekturze Clarkdale (2010 r.) Intel integrował

układ graficzny i kontroler pamięci jako oddzielną

kość umieszczoną w jednym opakowaniu razem

z CPU.

• Począwszy od architektury Sandy Bridge (2011 r.)

Intel integruje układ graficzny, kontroler pamięci

i CPU w pojedynczej kości.

Instrukcje multimedialne

• Od 1997 r. Intel zaczął implementować w swoich

procesorach

zestawy

dodatkowych

rozkazów

multimedialnych (początkowo instrukcje MMX –

MultiMedia eXtensions, później SSE – Streaming SIMD

Extensions).

• Ostania dodana partia rozkazów ma numer SSE 4.2.

• AMD w 1998 r. zaczęło implementować własny

dodatkowy zestaw rozkazów multimedialnych 3DNow!

• W 2010 r. AMD wstrzymało implementację instrukcji

3DNow! w nowych modelach swoich CPU.

• Obecnie procesory AMD (w większości) mają

zaimplementowaną obsługę instrukcji MMX i SSE.

Automatyczne przetaktowywanie

• Od architektury Nehalem (2008 r.) Intel

w niektórych modelach procesorów implementuje

technologię automatycznego przetaktowywania

rdzeni nazywaną Turbo Boost.

• Turbo Boost automatycznie podwyższa lub obniża

częstotliwość taktowania poszczególnych rdzeni

CPU w zależności od warunków takich jak np.

aktualny pobór mocy ,współczynnik TDP oraz

maksymalna dopuszczalna częstotliwość zegara

taktującego.

• AMD w 2010 r. zaimplementowało w niektórych

swoich CPU technologię Turbo Core działającą

na podobnej zasadzie jak konkurencyjny Turbo

Boost.