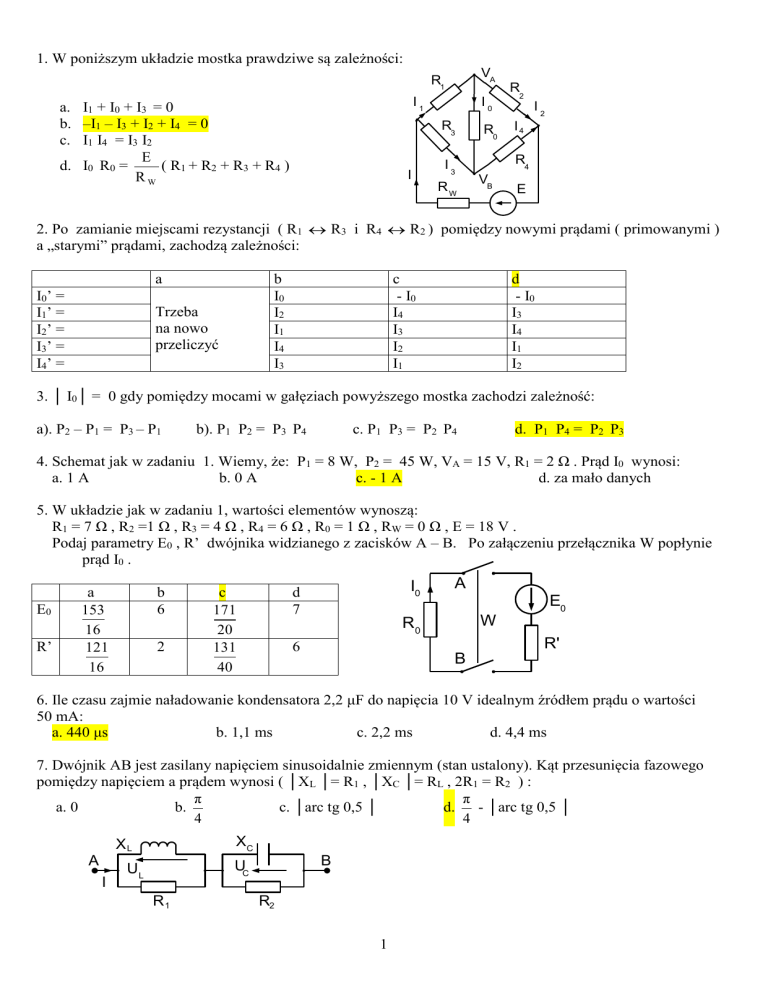

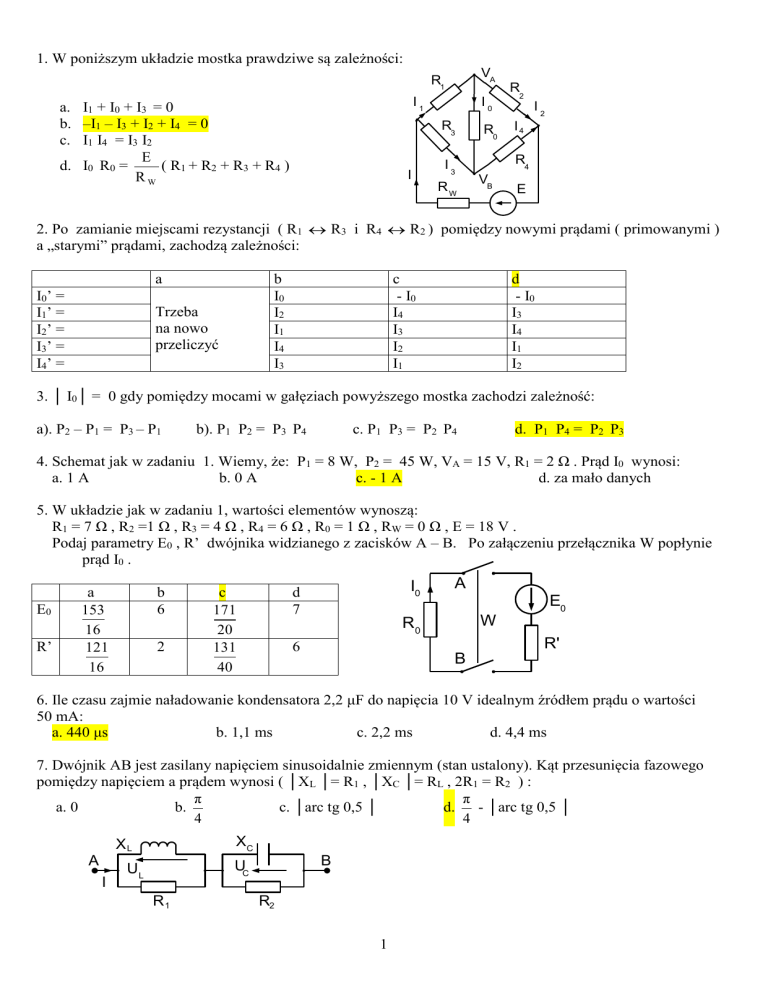

1. W poniższym układzie mostka prawdziwe są zależności:

VA

R1

I1

a. I1 + I0 + I3 = 0

b. –I1 – I3 + I2 + I4 = 0

c. I1 I4 = I3 I2

E

d. I0 R0 =

( R1 + R2 + R3 + R4 )

RW

I0

R3

I

I3

RW

R0

R

2

I2

I4

R4

VB

E

2. Po zamianie miejscami rezystancji ( R1 R3 i R4 R2 ) pomiędzy nowymi prądami ( primowanymi )

a „starymi” prądami, zachodzą zależności:

a

I0’ =

I1’ =

I2’ =

I3’ =

I4’ =

b

I0

I2

I1

I4

I3

Trzeba

na nowo

przeliczyć

c

- I0

I4

I3

I2

I1

d

- I0

I3

I4

I1

I2

3. │ I0│ = 0 gdy pomiędzy mocami w gałęziach powyższego mostka zachodzi zależność:

a). P2 – P1 = P3 – P1

b). P1 P2 = P3 P4

c. P1 P3 = P2 P4

d. P1 P4 = P2 P3

4. Schemat jak w zadaniu 1. Wiemy, że: P1 = 8 W, P2 = 45 W, VA = 15 V, R1 = 2 Ω . Prąd I0 wynosi:

a. 1 A

b. 0 A

c. - 1 A

d. za mało danych

5. W układzie jak w zadaniu 1, wartości elementów wynoszą:

R1 = 7 Ω , R2 =1 Ω , R3 = 4 Ω , R4 = 6 Ω , R0 = 1 Ω , RW = 0 Ω , E = 18 V .

Podaj parametry E0 , R’ dwójnika widzianego z zacisków A – B. Po załączeniu przełącznika W popłynie

prąd I0 .

E0

R’

a

153

16

121

16

b

6

2

c

171

20

131

40

I0

d

7

A

E0

W

R0

R'

6

B

6. Ile czasu zajmie naładowanie kondensatora 2,2 μF do napięcia 10 V idealnym źródłem prądu o wartości

50 mA:

a. 440 μs

b. 1,1 ms

c. 2,2 ms

d. 4,4 ms

7. Dwójnik AB jest zasilany napięciem sinusoidalnie zmiennym (stan ustalony). Kąt przesunięcia fazowego

pomiędzy napięciem a prądem wynosi ( │XL │= R1 , │XC │= RL , 2R1 = R2 ) :

π

π

a. 0

b.

c. │arc tg 0,5 │

d.

- │arc tg 0,5 │

4

4

XC

XL

A

I

B

UC

UL

R1

R2

1

8. Po zamianie trójkąta z pojemnościami C na równoważną gwiazdę, wartości pojemności C’ wynoszą:

V

V

a. 3C

C

2

C

b.

C

C'

3

Z

C'

C'

U

C

c. 2C

1

d.

C

U

Z

3

9. Dwa źródła napięcia połączono jak na rysunku. Po zamknięciu wyłącznika W przez R0 popłynie prąd:

24 V

a. 12 A

b. 8 A

c. 4 A

d. 0

2

12 V

1

W

3

R0

10. W kondensatorze płaskim wysunięto część dielektryka o przenikalności względnej εr. Określ w procentach,

jaką część dielektryka należy wysunąć, aby pojemność zmniejszyła się n – krotnie [n (1, εr )]. Wartość

X

100 % wynosi:

X

L

L

L

(ε 1)(n 1)

ε (n 1)

100% b. r

100%

a. r

nε r

n(ε r 1)

εrn

(ε 1)n

100% d. r

100%

c.

(n 1)(ε r 1)

(n 1)ε r

R

11. Przedstawiony czwórnik ma następujące własności selektywne:

a.

b.

c.

d.

pasmowo – przepustowe

stałe wzmocnienie niezależne od częstotliwości

pasmowo - zaporowe

dolnoprzepustowe

L

R

U wy

Uwe

L

12. W układzie przedstawionym na rysunku załączamy idealny klucz T1, a po ustabilizowaniu się prądów i

napięć równocześnie wyłączamy T1 i załączamy idealny klucz T2 . Określ różnicę pomiędzy ekstremalnymi

wartościami prądu IC :

+ 24 V

a.

b.

c.

d.

200 mA

260 mA

360 mA

480 mA

+ 12 V

IC

T2

C

600 Ω

100 Ω

T1

2

13. Dla źródła prądu określ dopuszczalny zakres zmian R0.

a.

b.

c.

d.

+ 12 V

00,14 k

03,3 k

012 k

0100 k

5V6

100

3k3

R0

14. Dla równoległego stabilizatora napięcia 5V/dz (na rysunku) podaj wartość minimalną R0 (pomijamy prąd

dzielnika z diodą Zenera).

+ 6 V 0,5 Ω

a.

b.

c.

d.

I

6

3

4,4

2,5

R

4V4

T

R0

390 Ω

15. Jaka maksymalna moc wydziela się na tranzystorze regulującym T?

a. 20W

b. 13W

c. 10W

d. 5W

16. Dla poniższego układu, podać wartość minimalnego napięcia

UCE tranzystora prostującego T pracującego jako klucz

(dioda D idealna).

a.

b.

c.

d.

5V

TTL

5kV

500V

50V

5V

T

0,1 H

10 Ω

D

10 k Ω

17. Charakterystyka wzmacniacza w funkcji częstotliwości (niskich) ma

K

kształt:

U

a.

f

+ EC

KU

RC

R1

b.

f

Rg

T

Uwe

R2

RE

KU

U wy

c.

f

CE

K

U

d.

f

3

18. Na wejście poniższego wzmacniacza podano przebieg prostokątny niskiej częstotliwości nałożony na

dodatnią składową stałą, tak aby wzmacniacz pozostawał w obszarze aktywnym pomiędzy VC min a VC max.

Następnie na oscyloskopie zaobserwowano przebieg VC.

UC

UC max

Δ UC

UC min

t

Aby uzyskać kształt prostokąta (amplituda VC nie musi zostać zachowana) należy:

a. zwiększyć CE 10- krotnie

c. zwiększyć EE

b. odłączyć CE

d. Zwiększyć Rg

19. Na wejście wzmacniacza selektywnego o częstotliwości 400 kHz podano przebieg prostokątny jak na

rysunku. Punkt pracy tranzystora dobrano tak, aby przy Uwe jak na rysunku, w pełni wykorzystać napięcie

zasilania EC. Elementy L, T idealne. Amplituda przebiegu na wyjściu wyniesie:

a. EC

1

+ EC

b.

EC

2

L

C

1

c.

EC

4

22 μ

d. 0

T

A

5 μs 5μs

U wy

Uwe

100 μ

20. W poniższym wzmacniaczu punkt pracy dobrano optymalnie. Zakładamy, że T jest idealny a rezystancję

cewki można pominąć. Po rozwarciu W uzyskamy:

+ EC

a.

b.

c.

d.

osłabienie n.cz.

uwydatnienie w.cz.

uwydatnienie n.cz.

osłabienie w.cz.

W

RC

R1

L

T

Uwe

R2

4

U wy

21. Wzmocnienie poniższego układu dla zakresu średnich częstotliwości wynosi około:

a.

b.

c.

d.

0,5

1

2

3

0,1 F

Uwe

Uwy

2 F

100k

100k

22. Wzmocnienie poniższego układu zależy:

a.

b.

c.

d.

1k

wprost od częstotliwości

odwrotnie od częstotliwości

jest stałe w funkcji częstotliwości

w układzie dochodzi do generacji drgań

1k

we

L

wy

C

R

23. W poniższym układzie na wyjściu otrzymujemy:

a.

b.

c.

d.

C

falę prostokątną

sinusoidę

obciętą sinusoidę

przebieg trójkątny

R4

R1

Uz

Uz

R3

wy

R2

24. W układzie z poprzedniego zadania wartość napięć maksymalnych (dodatnich i ujemnych) wynosi:

R3

R2 R4

R2

c. (U z 0,6V)

R3 R4

R2

R3

R

d. (U z 0,6V) 3

R1

a. (U z 0,6V)

b. (U z 0,6V)

25. W układzie z poprzedniego zadania okres generowanego przebiegu wyniesie:

a.

4R 3 R 1C

R2

b.

4R 2 R 3 C

R1

c.

4R 1 R 2 C

R3

d.

4R 1C

R 2R 3

26. Jeżeli zachodzi: f1 f 2 f 3 1 , to prawdziwa jest zależność (f – funkcje Boole’a):

a. f 2 f1 f 3

b. f 2 f1 f 3

c. f 2 f1 f 3

d. f 2 f1 f3

5

27. Bramkę sumy modulo 2 z wyjściem trójstanowym połączono jak poniżej. Jaka funkcja jest realizowana?

(bramka aktywna, gdy na wejściu sterującym mamy poziom L)

a.

b.

c.

d.

ab

ab

ab

ab

Vcc

1k

a

b

28. Poniższy układ może być wykorzystywany do: (a i b przebiegi periodyczne)

a. pomiaru stosunku częstotliwości

a

b. pomiaru średniego współczynnika

b

wypełnienia

c. pomiaru częstotliwości średniej

d. pomiaru wzajemnego przesunięcia fazowego

Uwy

29. Dla poniższego połączenia funktorów logicznych uzyskamy na wyjściu dwóch bramek O.C. typu sumy

modulo-dwa następującą funkcję:

+

a. a b

b. ab

c. a b

d. 1

R

a

b

a

b

wy

a

b

a

b

30. Poniższy układ może służyć

+5V

a. jako generator przebiegów o regulowanym

współczynniku wypełnienia (we=1)

b. do wykrywania impulsów jedynkowych „”

spełniających relację 1<<2

c. jw. dla relacji <1 lub >2

d. do generacji wąskich impulsów po każdym

zboczu impulsu na wejściu

we

P1

C

P2

5k1

5k1

1

2

Q1

wy

6

C

Q2

31. Aby zrealizować komparator równoległy dwóch 2-bitowych liczb binarnych b1 b0a1 a0 zastosowano

dekoder 4/16. Do generacji relacji M-R-W (mniejszy- równy- większy) wykorzystano trzy bramki NAND o

odpowiedniej ilości wejść. Do ich wejść podamy wprost następujące zanegowane wyjścia dekodera:

W

R

M

a.

4 , 8 , 9 , 12 , 13 , 14 0 , 5 , 10 , 15

1 , 2 , 3 , 6 , 7 , 11

b.

1 , 3 , 6 , 9 , 11 , 14

2 , 5 , 7 , 10 , 13 , 15

0 , 4 , 8 , 12

c.

1 , 3 , 7 , 8 , 9 , 13

0 , 4 , 5 , 11 , 12 , 15 2 , 6 , 10 , 14

d.

2 , 4 , 5 , 10 , 11 , 14 3 , 6 , 9 , 15

0 , 1 , 7 , 8 , 12 , 13

0

1

15

842 1

b1 b0 a1 a0

W

R

M

32. Na wejściu kodera kodu 1 z „n” na 3-bitowy kod binarny dokonano połączeń jak na rysunku. Uzyskujemy

w ten sposób na wyjściach

7

7

22

6

21

6

20

a.

b.

c.

d.

kod Graya

kod priorytetowy

kod Johnsona

kod linijki świetlnej

5

5

Koder 1 z n

33. Aby uzyskać funkcje dwójki liczącej (zmiana stanu na przeciwny co okres zegarów Z1,Z2) wykorzystano

dwa przerzutniki typu zatrzask. Jaki kształt zegarów Z1 Z2 jest wymagany?

D

Q

D

Q

Z1

Q

Q

Z2

a. nie jest możliwe

b.

c.

c.

7

d.

Z1

Z2

34. Przerzutnik D połączono jak na rysunku. Dla danych przebiegów clk i S określ przebiegi na wyjściu Q

S

clk

S

D S Q

clk

R

Q

a.

b.

Q

c.

d.

35. Licznik podłączono do dekodera zgodnie z rysunkiem. Do wyjść: 0 , 4 , 5 podłączono identyczny licznik.

n

Zlicza on z krotnością „ ” w stosunku do pierwszego licznika:

8

a.

3

2

1

0

4

5

b.

1

1

1

c.

2

1

3

d.

2

2

1

1

J0

1

K0

Q0

1

J1

1

K1

Q1

1

J2

1

K2

5

6

Q2

we

dekoder

0

1

2

3

4

7

36. Łącząc rejestr z sumatorem, jak poniżej uzyskujemy n- stanowy licznik (wyjścia: Q3 Q2 Q1 Q0). Wartość N

wynosi:

a.

b.

c.

d.

8

7

6

4

D3

Q3

a3 b3

S3

D2

D1

Rejestr

Q2

Q1

a2

b2

D0

Q0

a1

b1 a0 b0

c0

S1

S0

S2

37. Komparator szeregowy porównuje dwie liczby AB począwszy od bitów najmłodszych. Bieżący stan

porównywania zapamiętywany jest przez dwa przerzutniki: „W”- większy i „M” mniejszy (możliwe stany 10,

00, 01). Określ funkcje logiczne na wejściu Dw (przerzutnik „większy”). Przed porównaniem oba przerzutniki

są zerowane.

a Układ

D

Q

Qw

kombina- Dw D Q

a. (a b)Qw

A

cyjny

Q

b. a b Qw(a b)

c. (a Qw)b

D

d. a b Qw.a b

Q

B

Q

clk

8

b

DM

D

Q

QM

38. Jak wyżej tylko dla wejścia DM

a. a b Q M ab

b. (a b)Q M

c. ab Q M (a b)

d. (a Q M )b

39. Interfejs szeregowy, asynchroniczny, odbiera ramkę formatu 8- bitowego z bitem parzystości (przebieg

poniżej). Jaki bajt zostanie zidentyfikowany?

a. 75h

b. AEh

c. 3Ah

d. 57h

40. Jeśli odbiornik w interfejsie szeregowym stwierdzi tzw. błąd ramki, świadczy to o:

a.

b.

c.

d.

przeciwnym stanie bitu parzystości

odebranym bajcie spoza kodu ASCII

niedopasowaniu odbiornika do prędkości nadawcy

zbyt długim odstępie pomiędzy kolejnymi ramkami

41. Rozkaz korekcji dziesiętnej bajtu używamy w celu:

a.

b.

c.

d.

konwersji liczby binarnej na dziesiętną

po rozkazie dodawania liczb w kodzie ASCII

w celu uzyskania wartości (100(dec)- liczba)- kod BCD

po rozkazie dodawania liczb w kodzie BCD

42. Mikroprocesor 8-bitowy wykonał odejmowanie liczb (7A-BE) hex. Uzyskany rezultat i stany bitów

warunkowych (C- przeniesienie / pozyczka ), Z- zerowość, N- znak, V- przekroczenie zakresu) wynoszą:

a.

b.

c.

d.

BC hex

38 hex

44 hex

6D hex

V

1

0

1

0

N

1

1

0

0

Z

0

0

1

0

C

1

0

0

1

43. Uzyskany powyżej rezultat jest poprawny (+) lub niepoprawny (-) dla kodów NB (naturalny binarny) oraz

U2 (uzupełnień do dwóch).

a.

b.

c.

d.

NB

+

+

-

U2

+

+

-

44. W którym typie rozkazów musimy zwracać uwagę na kod używany do obliczeń (NB lub U2)?

a. Przesunięcia

b. Dodawania

c. Odejmowania

45. Mikrokontroler 8051 zaliczamy do układów typu:

a. Harvard

b. von Neumana

c. pseudo- Harvard

9

d. innych

d. Porównania

46. Przenoszalność oprogramowania w przód w ramach tej samej rodziny p (mikroprocesorów) nie jest

możliwa, jeżeli nowy typ ma:

a.

b.

c.

d.

nowe linie przerywające

nowe rozkazy

inną interpretację bitów warunkowych

nowe rejestry

47. Przenoszalność oprogramowania wstecz w ramach tej samej rodziny p (wykorzystujemy wyjątek

nielegalnej instrukcji i emulację softwarową) jest niemożliwe, gdy nowszy p posiada:

a.

b.

c.

d.

nowe rejestry

nowe tryby adresowania

szybszy zegar

nowe formaty danych

48. Instrukcje: DJNZ (dekrementacja i skok gdy nie zero) oraz CJNE (porównanie i skok gdy nierówne) można

używać do organizacji pętli programowych. Indeks pętli może być zwiększany (+) bądź zmniejszany (-). Określ

typowe zastosowanie obu rozkazów w każdej parze.

DJNZ

CJNE

a.

b.

+

c.

+

d.

+

+

49. Ciąg programu w hipotetycznym p zatrzymał się na instrukcji ALA: JMP ALA. Układ zaakceptował

przerwanie. Aby powrót z przerwania nastąpił do następnej instrukcji, z pominięciem „zapętlonego” skoku,

procedura przerywająca powinna:

a.

b.

c.

d.

nie ingerować- działanie powyższe jest właściwe dla każdego p

zmodyfikować rejestr SP (wskaźnik stosu)

przepisać stan SP do PC (licznik programu)

zmodyfikować na stosie adres „ALA”

50. W czasie cyklu magistrali typu odczyt, hipotetyczny p generuje strob odczytu RD . Kiedy karta ma wysłać

do p ważne dane?

RD

a.

b.

c.

d.

10