POLSKA

OPIS PATENTOWY

RZECZPOSPOLITA

LUDOWA

137887

Patent dodatkowy

do patentu nr

Zgłoszono: 82 08 05

(P. 237815)

Int. Cl4

G05F 1/56

Pierwszeństwo:

URZAO

PATENTOWY

PRL

Zgłoszenie ogłoszono: 84 02 13

Opis patentowy opublikowano: 1986 12 30

Twórca wynalazku: Czesław Osiński

Uprawniony z patentu: Instytut Komputerowych Systemów Automatyki

i Pomiarów, Wrocław (Polska)

Parametryczny stabilizator napięcia

tranzystorze bipolarnym, którego złącze baza-emiter jest zabocznikowane jednym rezystorem dwurezystorowego dzielnika, zać pomiędzy bazę i kolektor

ma włączony stabilizator lub stabilizator i diodę

prostowniczą, przy czym jeden zacisk wspomnia¬

nego dwójnika jest połączony z biegunem napięcia

zasilającego. Drugi rezystor wspomnianego dwure-

Przedmiotem wynalazku jest parametryczny sta¬

bilizator napięcia, przeznaczony

do stosowania w

różnych układach elektronicznych — wymagających

małego lub ściśle określonego prądu spoczynkowe¬

go albo stałego, wymuszonego przepływu prądu po¬

między dwoma wybranymi węzłami układu — głów¬

nie zaś w dwuprzewodowych przetwornikach i se¬

paratorach analogowych operujących sygnałem

przesyłowym 4—20 mA jako wejściowy stabiliza¬

tor napięcia. Może być również wykorzystany jako

zystorowego dzielnika jest połączony z drugim bie¬

10

dwójnikowy stabilizator prądu.

Powszechnie w roli parametrycznego stabilizato¬

ra napięcia jest stosowany złączowy tranzystor po¬

lowy pracujący przy bramce zwartej ze źródłem.

Jednakże wielkość prądu przepuszczana przez tak

połączony tranzystor nie jest powtarzalna nawet dla

różnych egzemplarzy tego samego typu. Poza tym,

15

Z polskiego opisu patentowego nr 127 400 znany

20

storem dwurezystorowego dzielnika połączonego dru¬

gim rezystorem z jednym biegunem napięcia zasi¬

lającego, charakteryzuje się tym, że kolektor bi¬

tywany jako programowany stabilizator prądu.

Z innego polskiego opisu patentowego nr 124 258

jest znany wtórnikowy stabilizator napięcia z ogra¬

25

niczeniem prądu obciążenia, który ma czwórnik re¬

gulacyjny w postaci szeregowego tranzystora, ste¬

polarnego tranzystora jest

połączony

z

wyjściem

stabilizatora, które poprzez rezystor jest połączone

z wyjściem regulacyjnego czwórnika, zaś poprzez

odbiornik programujący prąd dwójnikowego stabi¬

rowanego różnicą napięć wyjściowego i odniesienia

pobieranego z dwójnika — zmniejszającego rezys¬

stabilizatora — opartego na

lub emiterem bipolarnego tranzystora, którego złą¬

cze baza-emiter jest zbocznikowane jednym rezy¬

jest tranzystorowy układ parametrycznego stabili¬

zatora napięcia, który może być również wykorzys¬

137 887

na przykład w przetwornikach

w regulacyjny czwórnik, połączony wejściem z bazą

ratura otoczenia.

dynamiczną

pięcia zasilającego,

dwuprzewodowych stabilizujących prąd w stan¬

dardowym zakresie.

Parametryczny stabilizator napięcia zaopatrzony

silny wpływ na punkt pracy tranzystora ma tempe¬

tancję

gunem napięcia zasilającego.

Wadą znanych układów wtórnikowych stabiliza¬

torów napięcia jest znaczna wartość i zależność

prądu spoczynkowego od zmian napięcia zasilają¬

cego, co praktycznie uniemożliwia ich stosowanie

w układach z założenia odpornych na zmiany na¬

lizatora lub rezystor, napięciowe wyjście jest połą¬

30

czone z drugim biegunem zasilającego napięcia.

137 887

W innej wersji parametryczny stabilizator napię¬

(fig. 1), którego część jest przepuszczana przez tran¬

cia charakteryzuje się tym, że kolektor bipolarnego

zystor

tranzystora jest połączony z wyjściem regulacyjne¬

go czwórnika, który poprzez rezystor jest połączone

przez rezystor R4 będący obciążeniem tego wyjś¬

cia dla warunku utrzymania prądu Idi stabilizatora

z napięciowym wyjściem stabilizatora, które poprzez

5

tycznie stałym prądem spoczynkowym jest niewiel¬

stabilizatora

napięcia

może

i

przepływa

Ubei

napięcia

Zaletą parametrycznego stabilizatora napięcia we¬

dług wynalazku, poza małym, rzędu 20—50 |*A —

zależnym od typu stosowanego stabilizatora — prak¬

parametrycznego

stabilizatora

>R2

10

ka, około 0,7V minimalna, wymagana dla prawid¬

łowej pracy układu, różnica napięć wejście—wyjś¬

cie. Po włączeniu rezystora w miejsce odbiornika

napięcia stałego może być on wykorzystany jako

dwójnik stabilizujący prąd, którego poziom można

zmieniać przez zmianę wartości wymienionego re¬

zystora.

Dzięki małej mocy rozpraszanej w elementach

wyjścia

Ze względu na logarytmiczną zależność spadku

dwutranzystorowy układ super -

-alfa.

do

Dl na poziomie .

odbiornik lub rezystor programujący prąd dwójnikowego stabilizatora jest połączone z drugim bie¬

gunem zasilającego napięcia, natomiast regulacyjny

czwórnik stanowi

Tl,

na

wejściu

tranzystora

bipolarnego

w

funkcji jego prądu kolektora, praktycznie całą —

wymuszoną przez wahania zasilającego napięcia —

zmianę prądu I przejmuje tranzystor Tl zapewnia¬

jąc tym samym prawie stały punkt pracy stabili¬

zatorowi Dl. Regulacyjny czwórnik 1 porównuje

wyjściowe napięcie układu z napięciem odniesienia

15 wyznaczonym przez sumę napięć UDI+UBEI (fig.

1) lub UD1+UD2 (fig. 2) i odpowiednio do zmian

obciążenia,

które reprezentuje rezystor

R4,

regu¬

luje prądem doprowadzanym do wyjścia tak, aby

utrzymać

spadek napięcia na rezystorze R£

na

20 stałym poziomie praktycznie równym przy założe¬

niu

R3=0 UDI.

Wyjście układu z zacisku A obciążone rezysto¬

być

rem R4 ma więc charakter napięciowy, bowiem

zmiana rezystora R4 praktycznie nie wpływa na

on — z wyłączeniem czwórnika regulacyjnego dla

dużych obciążeń — wykonany jako układ scalony.

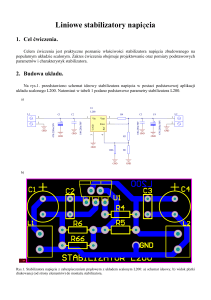

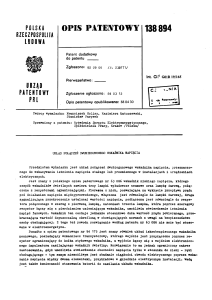

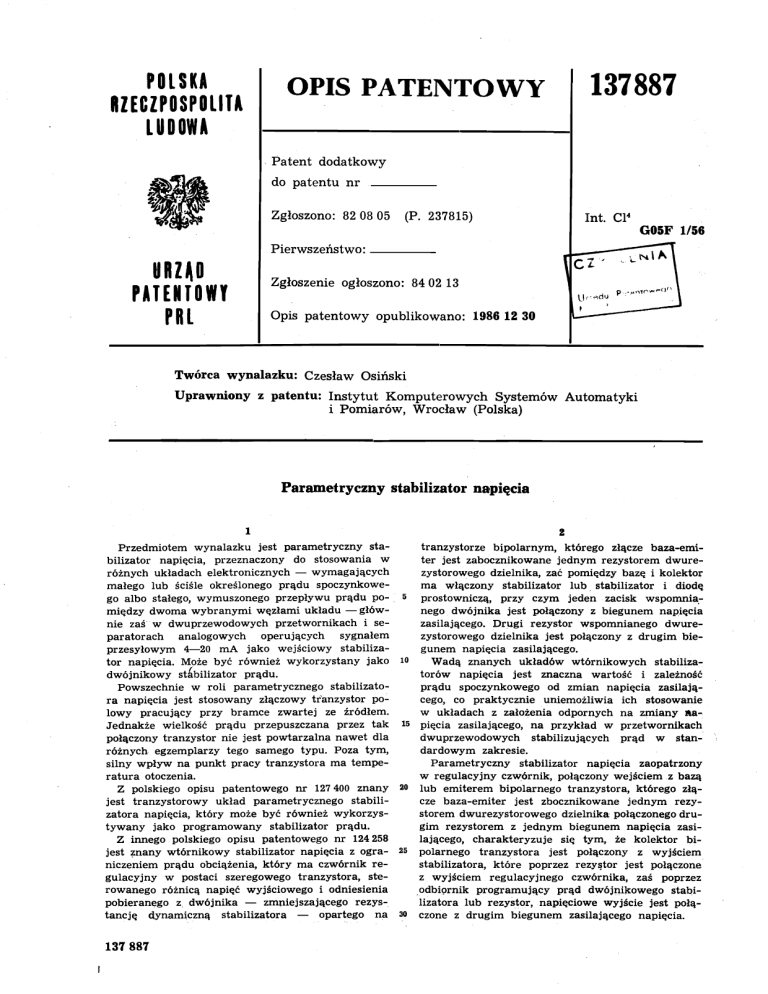

Przedmiot wynalazku jest uwidoczniony w przy¬

kładzie wykonania na rysunku, na którym fig. 1

25 wielkość wytworzonego na nim spadku napięcia.

przedstawia schemat ideowy parametrycznego sta¬

D2 podzielonym przez wartość tego rezystora R3.

W przypadku konieczności zapewnienia minimal-

bilizatora napięcia, mający bipolarny tranzystor

połączony kolektorem z wyjściem stabilizatora, zaś

fig. 2 — inną wersję stabilizatora, w którym bi¬

polarny

tranzystor

jest

połączony

kolektorem

poprzez

rezystor

Rl

z

dodatnim

służy

można zmostkować usuwając jednocześnie diodę D2.

Oznaczając minimalny dla prawidłowego działania

stabilizatora prąd czwórnika 1 przez Ip można określić warunek na maksymalną wartość progra¬

35

mującego rezystora R4 wyprowadzony przy pomi¬

nięciu wejściowego prądu czwórnika 1 i zwartym

rezystorze R3.

gunem zasilającego napięcia Uz oraz złącze baza-emiter zabocznikowane rezystorem R2.

Baza tranzystora Tl jest połączona (fig. 1) z kato¬

Uz—UDI—UBEI ^ UDI

Rl

dą stabilizatora Dl, zaś poprzez prostowniczą dio¬

—+Ip>-

R4

UDI

stąd R4 max <

Uz max —UDI —UBEI

+ Ip

Rl

UDI

45

Prądu II stabilizatora wyraża się jako

R4

UBEI

ciem do emitera tranzystora Tl, zaś według fig. 2 —

do bazy tranzystora Tl. Pomiędzy wyjście B czwór¬

nika 1 i pierwszy wyjściowy zacisk A stabilizatora

jest włączony rezystor R3.

obciążenia

30 nej rezystancji wyjściowej rezystor R3 i diodę D3

bie¬

dę D2 z pierwszym zaciskiem A napięciowego wyjś¬

cia stabilizatora, do którego jest również podłączo¬

ny kolektor wspomnianego tranzystora Tl. Regu¬

lujący czwórnik 1 zaciskiem wspólnym dla jego

wejścia i wyjścia jest połączony do dodatniego

bieguna Uz oraz w wykonaniu według fig. 1 wejś¬

ograniczeniu prądu

na poziomie bliskim spadkowi napięcia na diodzie

z

wyjściem regulacyjnego czwórnika.

Parametryczny stabilizator napięcia jest zaopa¬

trzony w bipolarny tranzystor Tl, mający emiter

połączony

Rezystor R3

R2

Rzeczywiste parametry parametrycznego stabiliza-

50

W wykonaniu układu według fig. 2 katoda sta¬

torą napięcia według wynalazku są bardzo bliskie

wyżej opisanym przy dużym wzmocnieniu prądo¬

bilizatora Dl poprzez prostowniczą diodę D2 jest

połączona z zaciskiem A, zaś poprzez prostowniczą

wym czwórnika 1 (co najmniej 200) oraz spełnio¬

nym warunku UDI > UBEI.

diodę D3 z bazą tranzystora Tl, którego kolektor

jest zwarty z wyjściem B czwórnika 1. Równolegle

do wyjścia stabilizatora, pomiędzy zacisk A i ano¬

dę stabilizatora Dl jest włączony zastępujący od¬

biornik napięcia rezystor R4 programujący prąd IL

stabilizatora przepływający przez odbiornik RL

prądu włączony szeregowo z zasilającym napięciem

Uz.

55

1. Parametryczny stabilizator napięcia zaopatrzo¬

ny w regulacyjny czwórnik połączony wejściem z

bazą lub emiterem bipolarnego tranzystora, którego

•o złącze baza—emiter jest zabocznikowane jednym

rezystorem dwurezystorowego dzielnika połączonego

Działanie układu. Do wspólnego węzła rezystorów

Rl i R2 dopływa prąd I równy:

drugim

Uz—Udi—Ubei—Il«Rj

Ri

Zastrzeżenia patentowe

65

rezystorem

z jednym

biegunem

napięcia

zasilającego, znamienny tym, że kolektor bipolar¬

nego tranzystora (Tl) jest połączony z wyjściem

(A) stabilizatora, które poprzez rezystor (R3) jest

137 887

6

połączone z wyjściem (B) regulacyjnego czwórnika

(1), zaś poprzez odbiornik (RL) programujący prąd

(II) stabilizatora rezystor (R4), wspomniane wyjś¬

cie (A) jest połączone z drugim biegunem zasilają¬

cego napięcia (Uz).

zystorem dwurezystorowego dzielnika połączonego

drugim rezystorem z jednym biegunem napięcia

zasilającego, znamienny tym, że kolektor bipolar¬

nego tranzystora (Tl) jest połączony z wyjściem (B)

, regulacyjnego czwórnika (1), które poprzez rezystor

(R3) jest połączone z napięciowym wyjściem (A)

2. Stabilizator według zastrz. 1, znamienny tym,

że regulacyjny czwórnik (1) stanowi dwutranzystorowy układ super-alfa.

3. Parametryczny stabilizator napięcia zaopatrzo¬

ny w regulacyjny czwórnik połączony wejściem z

bazą lub emiterem bipolarnego tranzystora, którego

stabilizatora, które poprzez odbiornik (RL) progra¬

mujący

prąd

(II)

stabilizatora,

rezystor

(R4)

jest

połączone z drugim biegunem zasilającego napięcia

10

złącze baza—emiter jest zabocznikowane jednym re-

(Uz).

4. Stabilizator według zastrz. 3, znamienny tym,

że regulacyjny czwórnik (1) stanowi dwutranzysto-

rowy układ super-alfa.

Fig.1

Rufl *t-łW n

Fig. 2