Elementy Elektroniczne

dr hab. inż Piotr Płotka

pok. 301

tel. 347-1634

e-mail: [email protected]

konsultacje:

środa

8:15 - 9:00

czwartek 13:15 – 14:00

Elementy Elektroniczne - materiały pomocnicze:

eti.pg.edu.pl

O Wydziale

Katedry

Katedra Systemów Mikroelektronicznych

Dydaktyka

Przedmioty

Elementy Elektroniczne (materiały dla studentów)

1

Elementy Elektroniczne - Literatura:

3

1. M.Polowczyk, E.Klugmann, Przyrządy Półprzewodnikowe,

Wyd.PG, 2001

2. W. Marciniak, Przyrządy półprzewodnikowe i układy scalone, WNT,

1979

Literatura dodatkowa:

1.A.S. Sedra, K.C. Smith, "Microelectronic Circuits", Oxford,

2007

2.Ch. Papadopoulos, "Solid-State Electronic Devices: An

Introduction", Springer 2014

3.M. Grundmann, The Physics of Semiconductors: An

Introduction Including Nanophysics and Applications,

2ed., Springer 2010

4.Ch.C. Hu, Modern Semiconductor Devices for Integrated

Circuits, Prentice Hall 2009

5.S.M. Sze, Kwok K. Ng, "Physics of Semiconductor

Devices", 3 ed., Wiley, 3 ed., 2006

4

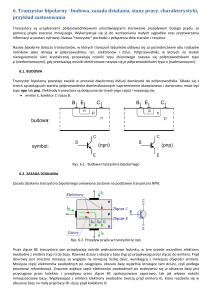

Spróbujmy zrozumieć jak działa

najpowszechniej dziś stosowany w

układach scalonych tranzystor MOS

wchodząc na początek tylko trochę w

fizykę półprzewodników.

2

Półprzewodniki w układzie okresowym

5

Najczęściej używanymi półprzewodnikami są Si oraz Ge z grupy IV

oraz związki IIIV jak GaAs, AlN, InP, GaP

Tabela układu okresowego – www.chemik.pl

regularne:

6

prosta

przestrzennie centrowana ściennie centrowana

Struktura krystaliczna

Atomy w sieci krystalicznej

ułożone są okresowo,

komórki podstawowe

powtarzają się.

diamentu

Si, C, Ge

blendy

cynkowej

GaAs,GaP

soli kuchennej

PbS, PbTe...

Wybrane ważne struktury

komórek sieci krystalicznej

S.M.Sze, Kwok K.Ng, Physics of

Semiconductor Devices, 3 ed, Wiley, 2006

wurcytu

CdS, ZnS...

3

Z okresowym ułożeniem atomów w krysztale wiąże się struktura pasmowa kryształu

7

• Pasmo przewodnictwa półprzewodnika jest tylko częściowo zapełnione

elektronami. Może ich tam być znikomo mało lub wystarczająco dużo dla

uzyskania znaczącego przewodnictwa.

• Pasmo walencyjne jest prawie całkowicie wypełnione elektronami. Dziury – braki

elektronów. Dziur w tym paśmie może być znikomo mało. Może ich tam być

znikomo mało lub wystarczająco dużo dla uzyskania znaczącego przewodnictwa.

Strukt_pasmowa_1

Z okresowym ułożeniem atomów w krysztale wiąże się struktura pasmowa kryształu

8

• Elektrony, te które są, mogą się swobodnie (prawie) poruszać w paśmie przewodnictwa

• Dziury – braki elektronów, mogą się swobodnie (prawie) poruszać w paśmie

walencyjnym

Strukt_pasmowa_2

4

Różnica pomiędzy półprzewodnikiem, a dielektrykiem jest umowna - tylko ilościowa

9

• Przerwa energetyczna dielektryka (izolatora) jest bardzo duża, rzędu kilku

elektronowoltów (eV).

• Dlatego w paśmie przewodnictwa praktycznie nie ma elektronów.

1 eV = 1 V · q

≈ 1,6·10-19 J

gdzie q – ładunek

elektronu

• Dlatego w paśmie walencyjnym praktycznie nie ma dziur, które mogłyby

przewodzić prąd elektryczny.

Strukt_pasmowa_3

Półprzewodnik w polu elektrycznym

10

E – energia

E – natężenie pola elektrycznego

Ψ – potencjał elektryczny

q – ładunek elementarny, q ≈ 1,6·10-19 C = 1,6·10-19 A·s

E = − q⋅Ψ

dΨ 1 dE

= ⋅

E =−

dx q dx

EC

EC

EV

EV

kierunek pola elektrycznego E

kierunek pola elektrycznego E

5

11

Zanim poznacie tranzystor MOS

zróbcie tranzystor inny od znanych!

Chcesz zrobić zupełnie nowy tranzystor - inny od znanych?

12

• Weź zasobnik elektronów (źródło,

emiter..).

• Weź drugi zasobnik elektronów (dren,

kolektor...) i umieść go na niższym

poziomie energetycznym – spolaryzuj

dodatnio względem pierwszego VDS>0V.

• Pomiędzy źródłem a drenem umieść

krzem o małej koncentracji n.

• Wytwórz w tym obszarze barierę

potencjału, taką aby jej wysokość ΨB

dała się regulować elektrycznie przez

zmianę napięcia sterującego VGS.

Jeśli uda Ci się to zrobić, i uzyskasz

wzmocnienie mocy, to masz użyteczny

tranzystor!

6

Wpływ bariery potencjału na natężenie prądu drenu

13

• Elektrony w pierwszym zasobniku,

źródle, mają różne energie E≥Ec.

Prawdopodobieństwo obsadzenia stanu

energetycznego bardzo szybko maleje

ze wzrostem E.

• Elektrony o wyższych energiach

przyczyniają sie do pokonywania bariery

ΨB przez część elektronów.

• Elektrony, które pokonały barierę ΨB są

dalej unoszone przez pole elektryczne E

w kierunku drugiego zasobnika – drenu.

Tworzą prąd drenu ID.

• Zmniejszanie |ΨB| powoduje, że więcej

elektronów pokonuje barierę – Płynie

prąd ID o większym natężeniu.

• Zwiększanie |ΨB| powoduje, że mniej

elektronów pokonuje barierę – Płynie

mniejszy prąd ID.

Wykres pasmowy dla tranzystora

14

• Ten wykres przedstawia tranzystor

wykonany z półprzewodnika jednego

rodzaju (krzemu).

• Szerokość przerwy energetycznej

Eg = Ec - Ev

jest stała w całym tranzystorze, od źródła

do drenu.

• W ogólnym przypadku różne części

tranzystora mogą być wykonane z

różnych rodzajów półprzewodnika, o

różnych Eg.

7

Możliwe mechanizmy transportu dziur i elektronów

15

Dyfuzja i unoszenie w polu elektrycznym

źródło

dren

• W obecnie produkowanych przyrządach odległość dren – źródło jest tak duża,

że elektrony doznają wielokrotnego rozpraszania. Ich energie i pędy relaksują.

• Wprowadza się pojęcie średniej prędkości unoszenia w polu E na drodze między

rozproszeniami.

• Transport nośników opisywany jest przy pomocy pojęć:

dyfuzji,

i unoszenia w polu E z uśrednioną prędkością.

Możliwe mechanizmy transportu dziur i

elektronów -1

Możliwe mechanizmy transportu dziur i elektronów

16

Transport balistyczny

Możliwe mechanizmy transportu dziur i

elektronów -2

źródło

dren

• Elektrony nie doznają rozpraszania na drodze źródło - dren. Ich energie i pędy nie

relaksują.

• Ich energie całkowite nie zmieniają się.

• W polu E na drodze bariera-dren wzrasta pęd elektronu, a zatem jego energia

kinetyczna.

• Energia kinetyczna może być bardzo wysoka, więc czas przelotu – bardzo krótki.

• Aby uniknąć rozpraszania odległość źródło-dren powinna być w GaAs < 20 nm, w

krzemie < 5 nm.

• Takie tranzystory mogłyby działać przy f > 1012 Hz (f > 1 THz)

8

Zjawiska ograniczające prąd w tranzystorze

17

• Transport elektronów w obszarze

niewielkiego pola E w kanale (za

barierą potencjału). Tak jest w

tranzystorach polowych, np.

MOS.

• Dwa zjawiska jednocześnie.

Wstrzykiwanie elektronów przez

barierę potencjału ΨB a także

transport elektronów w obszarze

zerowego lub niewielkiego pola E

w bazie (za barierą potencjału).

Tak jest w tranzystorach

bipolarnych.

• Wstrzykiwanie elektronów przez

barierę potencjału ΨB. Tak jest w

niektórych tranzystorach z bardzo

krótkim kanałem. Jest też

spodziewane w tranzystorach

balistycznych - bipolarnych i

polowych.

18

Nie będzie nam łatwo

wymyślić nowy tranzystor.

Najłatwiejsze do wymyślenia

zostały już wymyślone i

zrobione.

9

J.E Lilienfeld - wynalazek tranzystora MOS – 1933 r.

19

20

Nagrody Nobla za odkrycia i wynalazki

związane z przyrządami - 1/2

?

?

2014

Isamu Akasaki, Hiroshi Amano i Shuji Nakamura

- za sprawne diody świecące niebieskim

światłem, co pozwoliło wytworzyć jasne i

energooszczędne źródła światła

2010

Andre Geim, Konstantin Novoselov – za

doświadczenia nad dwuwymiarowym grafenem

2009

Charles K. Kao – za włókna optyczne do

przesyłania światła na duże odległości

Willard S. Boyle, George E.

Smith - za wynalezienie –

sensora CCD

10

2007

A. Fert, P. Grünberg- za odkrycie zjawiska

gigantycznego magnetooporu

2000

A. J. Heeger, A. G. MacDiarmid, H.

Shirakawa - za odkrycie i rozwijanie

polimerów przewodzących

2000

Z. I. Alferov - za opracowanie heterostruktur

półprzewodnikowych dla optoelektroniki

1998

R. B. Laughlin, H. L. Störmer, D. C. Tsui - za

odkrycie cieczy kwantowej ze wzbudzeniami

o ładunkach ułamkowych - ułamkowe

kwantowe zjawisko Halla

1987

J. G. Bednorz, K. A. Müller - za odkrycie

wysokotemperaturowego nadprzewodnictwa

w materiałach ceramicznyc

1985

K. von Klitzing - za kwantowe zjawisko Halla

1973

Leo Esaki - za doświadczalne okrycia

dotyczące tunelowania w półprzewodnikach

1972

J. Bardeen, L. N. Cooper, R. Schrieffer - za

teorię zjawiska nadprzewodnictwa (teorię

BCS)

1964

C. H. Townes, N. G. Basov, A. M. Prokhorov za badania, które doprowadziły do laserów i

maserów

1956

W. B. Shockley, J. Bardeen, W. H. Brattain za badania nad półprzewodnikami i odkrycie

tranzystora

21

Nagrody Nobla za odkrycia i wynalazki

związane z przyrządami - 2/2

H. Kroemer - za opracowanie

tranzystora heterozłączowego

Jack S. Kilby - za wkład w

wynalezienie układu

scalonego

I. Giaever - za doświadczenia

nad tunelowaniem w

nadprzewodnikach

B. D. Josephson - za teorię

tunelowania w złączu

nadprzewodników

Ian Ross (Bell) - wynalazek tranzystora MOS ze

wzbogacanym kanałem – 1955 r.

22

C.T. Sah, Evolution of the MOS transistor-from conception to VLSI, Proc IEEE, Vol.

76, pp. 1280-1326, 1988

11

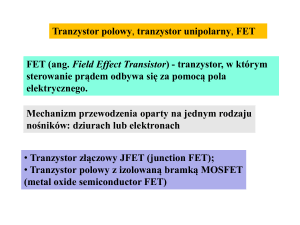

Układy Scalone

23

Wynalezione przez

Jacka Kilby

1958r. - Texas Instruments

• Elementy wykonane w pojedynczej płytce

Ge,

• trawionej na wskroś dla izolacji elementów;

• drutowe połączenia między elementami

Strona z notatnika J.S. Kilby ukazująca

generator z przesuwnikiem fazy

wykonany z płytki Ge metodą dyfuzji.

Strona z notatnika J.S. Kilby ukazująca

przerzutnik wykonany z płytki Ge

metodą dyfuzji.

J.S. Kilby, IEEE Trans. Electron Dev., v.23,

s.648, 1976

Wczesne układy scalone – Texas Instruments

Pierwszy układ scalony na germanie

wykonany przez J. Kilby

w Texas Instruments - 1958

24

Pierwszy planarny krzemowy układ scalony

wykonany techniką planarną. Przerzutnik z

aluminiową metalizacją, Fairchild, 1961 –

pomysł Roberta Noyce, 1958

“A Solid State of Progress,”

Fairchild Camera and Instrument Corporation,

1979, G.E.Moore, Proc. IEEE, v.86,s.53-62, 1998

12

Obecnie produkowane procesory z krzemowymi tranzystorami CMOS

http://www.electroiq.com

Procesor z tranzystorami w

technologii o rozmiarze

charakterystycznym 32 nm - Samsung

dla Apple iPhone5 – 2012 r.

25

Procesor czterordzeniowy z

tranzystorami wykonanymi w

technologii o rozmiarze

charakterystycznym 22 nm – INTEL

2013 r.

Zaprojektujcie układy lepsze dla Waszych

potrzeb, szybsze i zużywające mniej energii!

Tranzystor MOS

26

Charakterystyki statyczne tranzystora

polowego MOS ze wzbogacanym kanałem

typu n.

Static characteristics of a field-effect metal oxide

semiconductor transistor with an enhanced channel

Static characteristics – IV characteristics, current-voltage characteristics

metal oxide semiconductor field-effect transistor – MOSFET

enhanced channel - induced channel – normally OFF

13

Zerowe napięcia VGS i VDS

27

• W krzemie typu p równowagowa

koncentracja elektronów n jest

znikomo mała , np. 102 cm-3.

• W krzemie typu p równowagowa

koncentracja dziur p jest duża,

np. 1018 cm-3.

• Nie ma więc ciągłego kanału

elektronowego od źródła do

drenu. Bariera potencjału ΨB na

granicy obszaru n źródła jest

wysoka.

• Dlatego prąd drenu ID jest

znikomy nawet jeśli VDS>0 V.

Idealizowany wykres płaskich pasm (flat-band)

Ten wykres jest idealizowany. Założono

równe prace wyjścia i brak uwięzionych

ładunków.

VGS większe od napięcia progowego VTn , VDS ≈ 0 V

28

• Krzem pod powierzchnią SiO2 w

stanie silnej inwersji.

• Tranzystor odetkany gdy VGS > VTn >

0 V.

• Między źródłem a drenem utworzony

kanał o przewodnictwie

elektronowym.

• Przyłożenie VGS = VTn > 0 powoduje

obniżenie bariery potencjału ΨB do

nieistotnie małej wartości – w

tranzystorze z transportem

unoszeniowo-dyfuzyjnym.

• Jeśli VDS > 0 V to popłynie ID

związany z przepływem elektronów.

Idealizowany wykres pasmowy (band diagram)

14

VGS > VTn , 0 V < VDS < VGS - VTn

VGS > VTn , 0 V < VDS < VGS - VTn

29

• Krzem pod powierzchnią SiO2 w stanie

silnej inwersji - zaindukowany kanał typu

n.

• Płynie prąd drenu ID.

• Wzdłuż kanału o długości L przepływ

prądu drenu ID wywołuje zmianę

potencjału Ψ(x), przy czym

Ψ(x=0) = 0 V

Ψ(x=L) = VDS

gdzie

x=0 odpowiada krawędzi źródła,

x=L odpowiada krawędzi drenu.

• Wzdłuż kanału o zmienia się zatem

napięcie VG(x) pomiędzy metalową

bramką a kanałem:

VG ( x) = VGS − Ψ ( x)

Ładunek elektronów w kanale

VGS > VTn , 0 V < VDS < VGS - VTn

30

• Napięcie VG(x) pomiędzy metalową

bramką a kanałem zmienia się wzdłuż

kanału:

VG ( x) = VGS − Ψ ( x)

Ψ(x=0) = 0 V

Ψ(x=L) = VDS

• Przewodzący kanał można traktować jako

dolną okładkę kondensatora z SiO2 jako

dielektrykiem i metalem bramki jako górną

okładką.

• Napięcie VG(x) - VTn indukuje ładunek

charakterystyczny nośników w kanale

Qinvn:

0

Qinvn = −Cox ⋅ [VG ( x) − VTn ] = − q n( x, y )dy

−∞

Qinvn = −Cox ⋅ [VGS − VTn − Ψ ( x)]

gdzie

Cox =

ε SiO 2ε 0

tox

A⋅ s

m 2

A⋅ s

m 2

przy czym tox – grubość tlenku bramki

εSiO2 ε0 – przenikalność dielektryczna SiO2

15

Prąd drenu w obszarze triodowym

31

• Znając ładunek charakterystyczny

nośników w kanale Qinvn:

VGS > VTn , 0 V < VDS < VGS - VTn

Qinvn = −Cox ⋅ [VGS − VTn − Ψ ( x)]

• i wyrażenie na natężenie prądu

elektronowego w cienkiej warstwie Inx

ID

I D = − WQinvn μ nEx

Ex = −

dΨ ( x )

d ( x)

• otrzymujemy wyrażenie na przyrost

potencjału na krótkim odcinku dx

dΨ ( x ) =

VDS

0

gdzie

Prąd drenu w obszarze triodowym - 2

Cox =

ε SiO 2ε 0

I D ⋅ dx

μ nWCox ⋅ [VGS − VTn − Ψ ( x)]

L

μ nWCox ⋅ [VGS − VTn − Ψ ] ⋅ dΨ = I D ⋅ dx

0

tox

Prąd drenu w obszarze triodowym

32

VGS > VTn , 0 V < VDS < VGS - VTn

ID

• Natężenie prądu drenu jest stałe na całej

długości kanału

VDS

μ nWCox ⋅

0

gdzie

L

[VGS − VTn − Ψ ] ⋅ dΨ = I D ⋅ dx

Cox =

0

ε SiO 2ε 0

tox

• Po scałkowaniu otrzymujemy wyrażenie na ID(VDS, VGS)

16

Prąd drenu w obszarze triodowym - 3

Prąd drenu w obszarze triodowym

33

• Otrzymujemy więc wyrażenie na

charakterystyki statyczne tranzystora

polowego MOS ID(VDS, VGS)

ID

I D = μ n Cox

V2

W

⋅ (VGS − VTn ) ⋅VDS − DS

L

2

Cox =

gdzie

ε SiO 2ε 0

tox

• To wyrażenie jest słuszne dla zakresu

napięć VDS i VGS

VGS > VTn

0 V < VDS < VGS - VTn

• W tym zakresie napięć VDS napięcie VGS jest wystarczająco duże aby dokonać

inwersji na całej długości kanału.

• Dla większych VDS warstwa inwersyjna nie jest indukowana w pobliżu drenu.

Prąd drenu w obszarze triodowym - 4

Prąd drenu w obszarze triodowym

34

• W zakresie napięć VDS i VGS

VGS > VTn

0 V < VDS < VGS - VTn

I D = μ n Cox

W

L

V2

⋅ (VGS − VTn ) ⋅ VDS − DS

2

Cox =

ID

Obszar nasycenia

ε SiO 2ε 0

tox

Charakterystyka

idealnego

MOSFETa,

VTn = 1,0 V

• Pojedyncza charakterystyka ID(VDS) przy ustalonym VGS ma kształt odwróconej paraboli

osiągającej maksimum dla VDS=VGS-VTn – na granicy stosowalności.

• Ten obszar pracy nazywamy obszarem liniowym (triodowym, nienasycenia – linear,

triode, nonsaturation, non-pinch-off) tranzystora MOS.

17

Prąd drenu w obszarze nasycenia -1

Prąd drenu w obszarze nasycenia

• W zakresie wyższych napięć VDS

gdy

35

VGS > VTn

• Krzem pod powierzchnią SiO2 w pobliżu

źródła jest w stanie silnej inwersji zaindukowany kanał typu n.

VDS > VGS – VTn > 0 V

• Płynie prąd drenu ID.

• Wzdłuż kanału o długości L przepływ

prądu drenu ID wywołuje tak dużą zmianę

potencjału, że pod bramką w pobliżu

drenu nie dochodzi do inwersji – nie jest

indukowana warstwa typu n.

VG ( x) = VGS − Ψ ( x) < VTn

• Prąd drenu ID jednak płynie.

• Różnice potencjałów przyłożone

pomiędzy dren a źródło i pomiędzy

bramkę a źródło prowadzą do powstania

pola elektrycznego, które „porywa”

elektrony z końca inwersyjnego kanału i

unosi je do drenu.

• Ten obszar pracy nazywamy obszarem nasycenia (pentodowym – pentode, saturation,

pinch-off) tranzystora MOS.

Prąd drenu w obszarze nasycenia -2

Prąd drenu w obszarze nasycenia

• W zakresie wyższych napięć VDS

gdy

36

VGS > VTn

• Inwersyjny kanał typu n jest

zaindukowany pod częścią powierzchni

SiO2 - w pobliżu źródła.

VDS > VGS – VTn > 0 V

• Płynie prąd drenu ID.

• Natężenie prądu ID ma dla danej wartości

VGS taką jak maksymalna wartość w

obszarze triodowym:

W (VGS − VTn )

⋅

2

L

2

I D = μ n Cox

• Natężenie prądu drenu ID według

najprostszego modelu zależy tylko od

VGS, a nie zależy od napięcia dren –

źródło VDS

• Charakterystyki współczesnych

MOSFETów w układach scalonych

odbiegają od tego modelu.

• Ten obszar pracy nazywamy obszarem nasycenia (pentodowym – pentode, saturation,

pinch-off) tranzystora MOS.

18

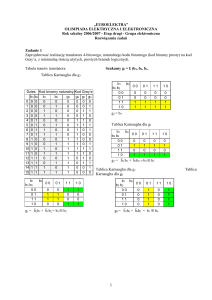

Prosty model charakterystyk tranzystora MOS

37

• W zakresie nasycenia, gdy

• W triodowym, gdy

VGS > VTn

VGS > VTn

VDS > VGS – VTn > 0 V

0 V < VDS < VGS - VTn

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

I D = βn ⋅

(VGS − VTn )2

2

β n = μ nCox

ID

Cox =

D

Obszar nasycenia

G

W

L

ε SiO 2ε 0

tox

Charakterystyka

idealnego MOSFETa, VTn

= 1,0 V

S

VGS < VTn

odcięcie

ID ≈ 0

• Charakterystyki współczesnych MOSFETów w układach scalonych odbiegają od tego modelu.

• Ale jest on nadal użyteczny, gdy chcemy wymyśleć jakiś układ.

Charakterystyki przejściowe tranzystora MOS

– tranzystor MOS z kanałem typu n wzbogacanym

38

D

Obszar nasycenia

G

VGS > VTn

S

Charakterystyka

idealnego MOSFETa, VTn

= 1,0 V

VGS < VTn

odcięcie

ID ≈ 0

VDS > VGS – VTn > 0 V

I D = βn ⋅

(VGS − VTn )2

2

Obszar

liniowy (triodowy)

VGS > VTn

0 V < VDS < VGS - VTn

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

β n = μ nCox

Cox =

W

L

ε SiO 2ε 0

tox

19

Charakterystyki przejściowe tranzystora MOS

– tranzystor MOS z kanałem typu n

Charakterystyki przejściowe - 2

39

Obszar nasycenia

D

VGS > VTn

G

VDS > VGS – VTn > 0 V

S

I D = βn ⋅

ID

(VGS − VTn )2

β n = μ n Cox

2

Charakterystyka

idealizowana

W

L

Wpływ rezystancji

szeregowych

Charakterystyka

rzeczywista

VGS < VTn

odcięcie

ID ≈ 0

VGS

Wpływ temperatury na charakterystyki tranzystora MOS

40

W zakresie dużych prądów ujemny temperaturowy

współczynnik prądu drenu ID:

D

dI D

<0

I D dT

G

Korzystny dla konstrukcji tranzystorów dużej mocy i

równoległego ich łączenia. – W przypadku wzrostu

temperatury jednej części prąd nie kumuluje się w tej

części.

S

nMOSFET

ID

I D ∝ μ n ∝ T −3 / 2

W zakresie małych prądów ID , gdzie

istotne jest wstrzykiwanie nośników nad

barierą potencjału, temperaturowy

współczynnik prądu drenu jest dodatni.

q ΨB

I D ∝ exp −

k BT

dI D

>0

I D dT

1,5

dI D

≈−

I D dT

T

(z dokładnością ok. 50%)

Obszar nasycenia

VGS

20

Napięcie progowe VTn tranzystora MOS z indukowanym

kanałem typu n

41

• Krzem pod powierzchnią SiO2 w stanie silnej

inwersji - „zakrzywienie pasm” 2ΦFBulk .

• Wpływ związanego z tym spadku napięcia

na tlenku bramki:

- QB/Cox

• gdzie QB – ładunek zjonizowanych

akceptorów w warstwie opróżnionej pod

tlenkiem bramki.

• Wpływ różnicy prac wyjścia metalpółprzewodnik Φms;

• Wpływ ładunku elektrycznego uwięzionego

na granicy tlenek-półprzewodnik i w tlenku

bramki Qf :

VTn 0 ≈ Φ ms −

Qf

Cox

+ 2Φ FBulk −

QB

Cox

Idealizowany wykres pasmowy

Wplyw VBS

Wpływ napięcia podłoże – źródło VBS

42

• Przyłożenie napięcia VBS ≠ 0 powoduje zmianę

grubości warstwy opróżnionej źródło-podłoże i

pod bramką, przy granicy SiO2.

• Zmiana ładunku zjonizowanych domieszek w

warstwie opróżnionej wpływa na wartość

napięcia progowego VTn .

• Podłoże może być używane jako dodatkowa

bramka, ale o małej skuteczności

(transkonduktancji)

Modelowanie wpływu VBS w programie SPICE: VTn ≈ VTn 0 + γ

(

2Φ FBulk − VBS − 2Φ FBulk

)

VBS = 0 V

21

2nd Generation 32-nm High-k + Metal Gate Transistors - Intel 2010

Metalowe

doprowadzenie

źródła/drenu

43

Tranzystor MOS z kanałem typu n.

Tranzystor MOS z kanałem typu p.

metalowa

bramka

metalowa

bramka

-kanał

-kanał

Epitaksjalne

pogrubienie krzemu w

źródle i drenie

zmniejsza rezystancję

szeregową.

krzem

krzem

Dielektryk bramki – SiO2/HfO2

o grubości ok. 2 nm

P. Packan i in., IEDM 2009 ss.659-662

Dla pMOS:

źródło i dren z SiGe

selektywnie wyhodowanego

w wytrawionch

wgłębieniach. SiGe ściska

krzem kanału, co zwiększa

ruchliwość dziur.

2nd Generation 32-nm High-k + Metal Gate Transistors - Intel 2010

Tranzystor MOS z kanałem typu n.

44

Tranzystor MOS z kanałem typu p.

-ID(VDS)

[mA/µm]

ID(VDS)

[mA/µm]

VGS =1.0V

Charakterystyki ID(VDS) przy ustalonych

wartościach VGS

0.8V

Uwaga:

• Prąd drenu |ID | nie wzrasta z kwadratem

|VGS|.

0.6V

• Napięcie VDS ma znaczący wpływ na ID

czyli rDS ≠ ∞.

• To są skutki bardzo krótkiego kanału, 32

nm.

ID(VDS)

[mA/µm]

-ID(VDS)

[mA/µm]

Charakterystyki przejściowe ID(VGS) przy

ustalonych wartościach VDS

P. Packan i in., IEDM 2009 ss.659-662

22

Wpływ silnego pola elektrycznego E w kanale

45

Dla dużych natężeń pola elektrycznego E, w krzemie E > 104 V/cm, prędkości unoszenia

elektronów i dziur osiągają wartości nasycenia vdriftn ≈ vdriftp ≈ vsat ≈ 107 cm/s. Tak jest w

nowoczesnych tranzystorach z krótkimi kanałami.

W obszarze nasycenia

Przy założeniu vdriftn≈ vsat

Przy założeniu µn = const.

W (VGS − VTn )

⋅

2

L

2

I D = μ nCox

Kwadratowa zależność ID od VGS .

I D = vsat CoxW (VGS − VTn )

Liniowa zależność ID od VGS .

S.M.Sze, Kwok K.Ng, Physics of

Semiconductor Devices, 3 ed, Wiley, 2006

2nd Generation 32-nm High-k + Metal Gate Transistors - Intel 2010

Tranzystor MOS z kanałem typu n.

ID(VDS)

[mA/µm]

46

Tranzystor MOS z kanałem typu p.

Długość kanału L = 32 nm.

-ID(VDS)

[mA/µm]

Charakterystyki ID(VDS) przy ustalonych

wartościach VGS

• Prąd drenu |ID | nie wzrasta z kwadratem

|VGS|.

VGS =1.0V

0.8V

0.6V

• Napięcie VDS ma znaczący wpływ na ID

czyli rDS ≠ ∞.

• To są skutki bardzo krótkiego kanału, 32

nm.

Niech VDS = 0,5 V, oszacujmy natężenie pola

elektrycznego E :

E ≈

0,5V

≈ 1,5 ⋅105 V/cm

32nm

E > 104 V/cm, zatem prędkości unoszenia elektronów i dziur zbliżają się do

wartości nasycenia vdriftn ≈ vdriftp ≈ vsat ≈ 107 cm/s.

I D = vsat CoxW (VGS − VTn )

P. Packan i in., IEDM 2009 ss.659-662

Stąd niemal liniowa zależność ID od VGS .

23

Przykładowy procesor firmy INTEL z tranzystorami „tri-gate” (FinFET)

47

2013 r.: Procesor Core i7-4770K

(Haswell)

z tranzystorami CMOS tri-gate

(FinFET) wykonanymi w

technologii o rozmiarze

charakterystycznym 22 nm.

source: Intel, 2013

electrode

Gate high-k

dielectric

source: M. Bohr, K. Mistry,

Intel’s Revolutionary 22 nm Transistor Technology, May, 2011

nMOSFET z kanałem wzbogacanym

(indukowanym, normalnie wyłączony)

Sept. 2013:

Intel – 14-nm Broadwell

Processor Consuming 30%

Less Power Than 22nm

Haswell

nMOSFET z kanałem zubażanym

(opróżnianym, normalnie włączony)

48

zubażany nMOS - 2

• Napięcie progowe, przy którym tranzystor ulega

zatkaniu – wchodzi w stan odcięcia - jest dodatnie

VTn > 0 V

• Napięcie progowe, przy którym tranzystor ulega

zatkaniu – wchodzi w stan odcięcia - jest ujemne

VTn < 0 V

24

nMOSFET z kanałem wzbogacanym

(indukowanym, normalnie wyłączony)

nMOSFET z kanałem zubażanym

(opróżnianym, normalnie włączony)

49

zubażany nMOS - 3

• Napięcie progowe, przy którym tranzystor ulega

zatkaniu – wchodzi w stan odcięcia - jest dodatnie

VTn > 0 V

ID

• Napięcie progowe, przy którym tranzystor ulega

zatkaniu – wchodzi w stan odcięcia - jest ujemne

VTn < 0 V

ID

0

VGS

0

VGS

nMOS i pMOS - 1

nMOSFET i pMOSFET – porównanie charakterystyk wyjściowych

MOSFET z kanałem

indukowanym typu n

MOSFET z kanałem

zubażanym typu n

50

MOSFET z kanałem

indukowanym typu p

MOSFET z kanałem

zubażanym typu p

25

nMOS i pMOS - 2

nMOSFET i pMOSFET – porównanie charakterystyk wyjściowych

MOSFET z kanałem indukowanym typu n

MOSFET z kanałem indukowanym typu p

ID

ID

D

D

G

G

S

VTn > 0

ID > 0

51

ID < 0

VTp < 0

S

µp = µn/3 - dlatego |ID| ok. 3 razy

mniejszy dla pMOS niż dla nMOS

przy jednakowych |VGS – VTn(p)|

nMOS i pMOS - 3

nMOSFET i pMOSFET – porównanie charakterystyk wyjściowych

MOSFET z kanałem indukowanym typu n

obszar odcięcia: VGS <= VTn

obszar nasycenia: VGS > VTn , VDS > VGS – VTn > 0 V

obszar triodowy: VGS < VTp , 0 V > VDS > VGS - VTp

W

β p = μ p Cox

L

ID

ID > 0

V2

I D = − β p ⋅ (VGS − VTp )⋅ VDS − DS

2

obszar nasycenia: VGS < VTp , VDS < VGS – VTp < 0 V

(VGS − VTn )

2

I D = βn ⋅

ID ≈ 0

ID ≈ 0

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

W

β n = μ nCox

L

MOSFET z kanałem indukowanym typu p

obszar odcięcia: VGS >= VTp

obszar triodowy: VGS > VTn , 0 V < VDS < VGS - VTn

52

I D = −β p ⋅

2

(V

GS

− VTp )

2

2

VTn > 0

ID

D

D

G

S

ID < 0

VTp < 0

µp = µn/3 - dlatego |ID| ok. 3 razy

mniejszy dla pMOS niż dla nMOS

przy jednakowych |VGS – VTn(p)|

G

S

26

nMOS i pMOS - 4

nMOSFET i pMOSFET – porównanie charakterystyk przejściowych 53

ID

ID

ID

ID

D

nMOSFET z kanałem

indukowanym

nMOSFET z kanałem

zubażanym

G

ID

D

G

S

S

0

pMOSFET z kanałem

indukowanym

VGS

pMOSFET z kanałem

zubażanym I

D

ID

D

D

G

G

S

S

Stałoprądowy punkt pracy tranzystora MOS

54

Niech na przykład VGG = VGS0 = 0,5 V.

Rozwiązujemy układ dwóch równań:

I D (VDS , VGS ) = f (VDS , VGS )

- równanie charakterystyki statycznej

tranzystora

VDS + I D RL = VDD - równanie prostej obciążenia

UWAGA:

Opisy analityczne charakterystyk statycznych zwykle

dane są różnymi funkcjami w zakresach triodowym,

nasycenia i odcięcia.

Szukając analitycznie punktu pracy (ID0 , VDS0 , VGS0)

wygodnie jest:

• założyć np. że tranzystor pracuje w obszarze nasycenia,

• rozwiązać równanie charakterystyk z równaniem prostej

obciążenia,

• sprawdzić poprawność założenia,

• jeśli trzeba, to zmienić złożenie o obszarze pracy i

rozwiązać ponownie odpowiedni układ równań.

27

Odpowiedź na niewielką zmianę napięcia bramka źródło ΔVGS

55

Niech na przykład VGG = VGS0 = 0,5 V.

Niech napięcie VGS zmieni się: VGS2 = VGS0 + ΔVGS.

Poszukujemy: ID2 , VGS2.

ΔI D = I D 2 − I D 0

ΔI D = (I D1 − I D 0 ) + (I D 2 − I D1 )

I D1 − I D 0 ≈

∂I D

∂VGS

∂I D

∂VDS

I D 2 − I D1 ≈

ΔI D ≈

∂I D

∂VGS

⋅ ΔVGS

VDS = const .

⋅ ΔVDS

VGS = const .

⋅ ΔVGS

+

VDS = const .

∂I D

∂V DS

⋅ ΔV DS

VGS = const .

Odpowiedź na niewielką zmianę napięcia bramka źródło ΔVGS

56

Odpowiedź DVGS -2

Niech na przykład VGG = VGS0 = 0,5 V.

Niech napięcie VGS zmieni się: VGS2 = VGS0 + ΔVGS.

Poszukujemy: ID2 , VGS2.

ΔI D ≈

∂I D

∂VGS

⋅ ΔVGS

+

VDS = const .

∂I D

∂VDS

⋅ ΔVDS

VGS = const .

Definiujemy transkonduktancję gm:

gm ≈

∂I D

∂VGS

VDS =const .

Definiujemy konduktancję i rezystancję wyjściową gDS , rDS :

g DS =

∂I

1

≈ D

rDS ∂VDS

VGS =const .

zatem:

ΔI D ≈ g m ⋅ ΔVGS + g DS ⋅ ΔVDS

Ale z prostej

obciążenia:

ΔVDS = − RL ⋅ ΔI D

ΔI D ≈

Ostatecznie:

g m rDS

⋅ ΔVGS

rDS + RL

ΔVDS ≈ −

g m rDS RL

⋅ ΔVGS

rDS + RL

28

Małosygnałowy schemat zastępczy dla małych częstotliwości

57

schemat malosygn m.cz.

Dokonaliśmy linearyzacji opisu charakterystyk tranzystora dla poszukiwania odpowiedzi na

małe pobudzenia wokół stałoprądowego punktu pracy (ID0 , VDS0 , VGS0).

id = I D 0 + I d sin(ωt + α )

VGG =

V DD = VDD 0

VGG 0 + Vgg sin(ωt )

= const.

v ds = VDS 0 + Vds sin(ωt + β )

Amplitudy składowych zmiennych:

Id ≈

g m rds

⋅ Vgs

rds + RL

Vds ≈ −

gdzie

rds ≈ rDS

g m rds RL

⋅ Vgs

rds + RL

Schemat zastępczy dla średnich częstotliwości

58

- uzupełniony o pojemności bramka-źródło CGS oraz bramkadren CGD a także o elementy pasożytnicze

pasożyt

pasożyt

pasożyt

Bramka

pasożyt

Dren

Dla stałoprądowego punktu

pracy w obszarze nasycenia:

1

CGS ≈ WL ⋅ Cox

2

1

CGD < WL ⋅ Cox

2

Źródło

Pojemności reprezentują wpływ

elektrycznego ładunku przepływających

nośników oraz ładunku zgromadzonego w

warstwie opróżnionej pod tlenkiem

bramki.

29

Częstotliwości graniczne przy pobudzeniu małymi sygnałami

Bramka

59

Dren

Uwzględnijmy tylko niezbędne do działania

tranzystora pojemności bramka-źródło CGS

oraz bramka-dren CGD , a także rezystancję

szeregową bramki rgg’ . Resztę

kondensatorów i rezystorów pomińmy.

Źródło

Graniczna częstotliwość wzmocnienia prądowego tranzystora MOS fT to taka częstotliwość

przy której ekstrapolowane wzmocnienie prądowe tranzystora spada do wartości 1.

fT ≈

gm

gm

=

2πWLCox 2π (CGS + CGD )

Graniczna częstotliwość wzmocnienia mocy tranzystora MOS fmax to taka częstotliwość

przy której ekstrapolowane wzmocnienie mocy tranzystora spada do wartości 1.

f max ≈

fT

8π ⋅ rgg 'CGD

Modele czwórnikowe tranzystora

ig

Bramka

Dren

id

wy

we

Źródło

Vgs = h11S I g + h12 SVds

I d = h21S I g + h22 SVds

I g = y11SVgs + y12 SVds

I d = y21SVgs + y22 SVds

Vgs = z11S I g + z12 S I d

Vds = z 21S I g + z 22 S I d

równania mieszane

(hybrydowe)

równania

admitancyjne

równania

impedancyjne

Macierze [hij], [yij] i [zij] można wzajemnie przekształcać.

Dla częstotliwości mikrofalowych wygodnie jest stosować

równoważną im macierz [Sij]

60

Małosygnałowy schemat zastępczy

tranzystora jest czwórnikiem.

Źródło jest wspólne dla wejścia i wyjścia

- układ ze wspólnym źródłem.

ig = i1 , vgs = v1

id = i2 , vds = v2

Wzmocnienie prądowe:

h21S ( f ) =

Id ( f )

Ig ( f )

Vds = 0

Dla tranzystorów polowych zachodzi:

f →0

h21S ( f ) → ∞

Transkonduktancja tranzystora:

g m = y21S =

Id

Vgs

Vds = 0

30

Rekordowo duże wartości częstotliwości granicznych fT w

tranzystorach CMOS wykonanych w technologii 45 nm - IBM 2007

Moduł

wzmocnienia prądowego

w układzie wspólnego źródła

h21S ( f ) =

id ( f )

ig ( f )

61

pMOS

nMOS

vds =0

Rekord fT w tranzystorach CMOS IBM 2007 - a

IEDM 2007, art. s10p04, IBM

Praca tranzystora MOS w nieliniowym układzie impulsowym

62

Zmiana napięcia vgs powoduje zmianę

prądu drenu id oraz napięcia vds. Punkt

pracy przesuwa się wzdłuż prostej

obciążenia ze zwłoką wynikającą z

ładowania pojemności tranzystora przez

prądy o ograniczonych wartościach.

v gs = VIN > VTn

VDD

Ro

id = I DON

MOS_switch_1

id =

VDD − vds

Ro

v gs = 0 < VTn

31

Praca tranzystora MOS w nieliniowym układzie impulsowym

63

Zmiana napięcia vgs powoduje zmianę

prądu drenu id oraz napięcia vds. Punkt

pracy przesuwa się wzdłuż prostej

obciążenia ze zwłoką wynikającą z

ładowania pojemności tranzystora przez

prądy o ograniczonych wartościach.

D

CGD

CDS

G

CGS

S

Hipoetyczny tranzystor

bezinercyjny z

dołączonymi

pojemnościami.

MOS_switch_2

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

64

Końcówka Rin przełączana jest od masy do VIN.

vgs<VTn - pojemność Cgs ładowana jest od 0 V do VTn.

id ≈ 0 dla czasu krótszego niż td(ON) od początku impulsu

(td(ON) – czas opóźnienia włączania).

IDON

id ≈ 0, vds ≈ VDD

MOS_switch_3

32

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

65

vgs>VTn - pojemność Cgs jest nadal ładowana, vgs

wzrasta.

Punkt pracy przesuwa się w obszarze nasycenia.

id wzrasta w czasie tr (czas narastania – rise time) do

wartości bliskiej IDON.

id

IDON

vds

MOS_switch_4

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

66

vgs>VTn - pojemność Cgs jest nadal ładowana, vgs

wzrasta aż ustali się wartość vgs=VIN .

Punkt pracy wchodzi w obszar triodowy.

id nieznacznie wzrasta osiągając wartość ustaloną

id=IDON gdy ustali się wartość vgs=VIN .

VDD

Ro

id = I DON

≈

VDD

Ro

IDON

vds

MOS_switch_5

33

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

•

67

Końcówka Rin przełączana jest od VIN do masy.

Punkt pracy przechodzi przez obszar triodowy do

granicy z obszarem nasycenia.

vgs>VTn - pojemność Cgs jest rozładowywana.

id prawie nie zmienia się (nieznacznie maleje) w czasie

td(OFF) od przełączenia (czas przeciągania, OFF delay time).

VDD

Ro

id = I DON

≈

VDD

Ro

IDON

vds

MOS_switch_6

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

68

Punkt pracy przechodzi przez obszar nasycenia do

granicy z obszarem odcięcia.

vgs>VTn - pojemność Cgs jest rozładowywana.

id maleje prawie do 0 w czasie tf (czas opadania prądu

drenu, fall time).

id

IDON

vds

MOS_switch_7

34

Praca tranzystora MOS w nieliniowym układzie impulsowym

•

•

•

69

Punkt pracy w odcięciu: vgs<VTn

pojemność Cgs jest nadal rozładowywana do czasu gdy

vgs = 0.

id ≈ 0.

IDON

id ≈ 0, vds ≈ VDD

MOS_switch_8

Praca impulsowa inwertera CMOS

70

VDD > 0 V

Vwe

MpA

VDD

0

VDD > 0 V

CL

Vwy

Przy skoku Uwe od UDD do 0 V tranzystor Mn

szybko jest zatykany. Pojemność obciążenia

CL jest ładowana do napięcia UDD przez Mp.

MpA

MnA

Vwe

CL

Vwy

VDD

0

Vwe

VDD

0

MnA CL

Vwy

0

Przy skoku Uwe od 0 V do UDD tranzystor Mp

szybko jest zatykany. Pojemność obciążenia CL

jest rozładowywana do napięcia 0 V przez Mn.

35

Oscylator Pierścieniowy

71

• Nieparzysta ilość inwerterów

tworzy oscylator pierścieniowy

(ring oscillator).

• Z generowanej częstotliwości f

określa się czas przełączania

bramki, czyli czas opóźnienia

pojedynczego stopnia (delay

time)

f oscil =

1

n ⋅ (t pLH + t pHL )

• gdzie tpLH oraz tpHL – czasy

przełączania ze stanu niskiego do

wysokiego i odwrotnie.

• Czas przełączania bramek z

większą ilością wejść jest trochę

dłuższy.

Vk/VDD - znormalizowane napięcia wyjściowe

bramek w funkcji znormalizowanego czasu

Szybkość Przełączania Inwerterów CMOS

72

Opóźnienie stopnia [pS]

Inwertery CMOS tranzystorami o

długości kanałów 32 nm (wykonane

w technologii 45 nm, Intel - 2009r.)

mają czas opóźnienia td = 5,1 pS.

=VDD

=VDD

Prąd w stanie odcięcia tranzystorów [nA/µm]

IEDM 2007, art. s10p02, Intel

36

Przewidywane skalowanie „wewnętrznej” szybkości tranzystorów

73

Oszacowanie 1/τ = I/(CV)

Przewidywane szybkości

oscylatorów pierścieniowych

International Technology Roadmap for Semiconductors, ITRS 2009 Edition

Maksymalna częstotliwość zegara, maksymalne napięcie zasilania VDD i (maksymalne

wymagane) napięcie progowe VTn , VTp dla układów scalonych CMOS

74

High performance – najlepsze właściwości.

Technology Node [nm] – połowa sumy szerokości

najwęższego paska i wajwęższej przerwy we

wzorze na powierzchni półprzewodnika, w danej

technologii.

Mniejsza długość kanału:

Rok

pozwala stosować większe częstotliwości zegara

wewnątrz układu scalonego;

wymaga stosowania niższych napięć zasilania VDD

aby uniknąć przebić elektrycznych i przegrzania,

a napięcia progowe tranzystorów VTn i VTp muszą

być mniejsze niż VDD/2.

S.Chatterjee et al., Circuit Design Techniques

at 0.5V, Springer 2007

37

75

Przykłady obliczeń

Przykład wzmacniacza z tranzystorem MOS

76

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

1. etap rozwiązania – znalezienie

stałoprądowego punktu pracy tranzystora

(VGSdc , VDSdc , IDdc)

Tranzystor MOS ma izolowaną bramkę – składowa stała prądu bramki IGdc = 0. Zatem

składową stałą napięcia bramka-źródło VGSdc wyznaczamy z dzielnika napięciowego:

VGSdc = VDD ·R2/(R2+R1)

VGSdc = 1,2 V

Zauważamy, że VGS > VTn oraz VDS > 0.

Oznacza to, że tranzystor pracuje w obszarze nasycenia lub nienasycenia.

Zakładamy, że tranzystor pracuje w obszarze nasycenia:

38

Przykład wzmacniacza z tranzystorem MOS

77

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

1. etap rozwiązania – znalezienie

stałoprądowego punktu pracy tranzystora

(VGSdc , VDSdc , IDdc)

VGSdc = 1,2 V

Zakładamy, że tranzystor pracuje w obszarze nasycenia:

I Ddc = β n ⋅

(VGSdc − VTn )2

dla VGSdc > VTn

; VDSdc ≥ VGSdc – VTn > 0

V

2

Podstawiamy znane wartości VTn = 0,2V oraz βn = 1 mA/V2 i otrzymujemy:

IDdc = 0,5 mA

Z równania oczkowego

otrzymujemy

VDSdc + I Ddc R0 = VDD

VDSdc = 1,5 V

Przykład wzmacniacza z tranzystorem MOS

78

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

1. etap rozwiązania – znalezienie

stałoprądowego punktu pracy tranzystora

(VGSdc , VDSdc , IDdc)

VGSdc = 1,2 V

Założyliśmy, że tranzystor pracuje w

obszarze nasycenia. Wyznaczyliśmy:

IDdc = 0,5 mA

VDSdc = 1,5 V

Sprawdzamy czy nasze rozwiązanie należy do obszaru nasycenia, t.j. czy spełnione są warunki:

VGSdc > VTn

Tak,

1,2 V = VGSdc > VTn = 0,2 V ;

; VDSdc ≥ VGSdc – VTn > 0 V

1,5 V = VDSdc > VGSdc – VTn = 1,2 V – 0,2 V > 0 V

Założenie o pracy tranzystora w obszarze nasycenia jest spełnione. Stałoprądowy punkt pracy

został wyznaczony poprawnie. Gdyby założenie nie było spełnione, należałoby szukać p.

pracy w obszarze triodowym używając odpowiedniego równania charakterystyk.

39

Przykład wzmacniacza z tranzystorem MOS

79

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

1. etap rozwiązania – znalezienie

stałoprądowego punktu pracy tranzystora

(VGSdc , VDSdc , IDdc)

VGSdc = 1,2 V

UWAGA:

Gdyby założenie o pracy tranzystora w obszarze nasycenia nie było spełnione, należałoby

szukać p. pracy w obszarze triodowym używając odpowiedniego równania charakterystyk.

I Ddc = β n ⋅

dla VGSdc > VTn ; 0 V < VDSdc < VGSdc - VTn

(VGSdc − VTn )2

dla VGSdc > VTn

2

V2

I Ddc = β n ⋅ (VGSdc − VTn ) ⋅VDSdc − DSdc

2

; VDSdc ³ VGSdc – VTn > 0 V

VDSdc + I Ddc R0 = VDD

Przykład wzmacniacza z tranzystorem MOS

80

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

2. etap rozwiązania – dla składowej zmiennej

Wyznaczony stałoprądowy punkt pracy

tranzystora pozwala nam określić wartość

transkonduktancji gm w małosygnałowym

schemacie zastępczym tranzystora MOS

gm =

dI Ddc

dVGSdc

VGSdc ,VDSdc

czyli, dla pracy w obszarze nasycenia:

(V − V )

d

β n GSdc Tn = β n (VGSdc − VTn )

dVGSdc

2

2

gm =

W naszym przypadku gm = 1 mS.

Małosygnałowy schemat zastępczy tranzystora MOS dla

małych częstotliwości i znikomej wartości gDS

40

81

Przykład wzmacniacza z tranzystorem MOS

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

2. etap rozwiązania – dla składowej zmiennej

Wykorzystujemy schemat zastępczy tranzystora MOS

tworząc małosygnałowy schemat zastępczy układu, dla

małych częstotliwości – słuszny dla pracy tranzystora w

o. nasycenia.

82

Przykład wzmacniacza z tranzystorem MOS

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

2. etap rozwiązania – dla składowej zmiennej

Z obwodu wejściowego:

Vgs = Em

Z oczka wyjściowego:

W obszarze nasycenia:

g m = β n ⋅ (VGSdc − VTn )

Vds = -Id ·R0 = -gmR0Em

Vds = -βn ·(VGSdc - VTn)R0Em

Podstawienie wartości liczbowych daje amplitudę składowej zmiennej

Vds = -3 mV

Znak "-" w wyniku interpretujemy jako odwrócenie fazy przez nasz wzmacniacz.

41

Przykład wzmacniacza z tranzystorem MOS

83

Tranzystor MOS z kanałem typu n w układzie jak na rysunku ma napięcie progowe VTn =

0,2V oraz współczynnik βn = 1 mA/V2. Określić wartość chwilową napięcia dren-źródło

vds(t). Pojemność Cz można uważać za zwarcie dla składowej zmiennej.

Nasz wzmacniacz odwraca fazę napięcia

wyjściowego w stosunku do napięcia

wejściowego.

Wartość chwilowa napięcia dren-źródło vds

vds(t) = VDSdc + Vds · sin(ωt) = 1,5 V - 3 mV · sin(ωt)

Małosygnałowy schemat zastępczy układu, dla

małych częstotliwości – słuszny dla pracy

tranzystora w obszarze nasycenia.

(co kończy rozwiązanie)

Wpływ rezystancji obciążenia na obszar pracy tranzystora

84

Tranzystor MOS z kanałem typu p, o wartości współczynnika βp = 1 mA/V2 i wartości VTp =

-0,2V pracuje w układzie jak na rysunku. Wyznaczyć zakresy wartości rezystancji R dla

których tranzystor pracuje w obszarze nasycenia i zakresy wartości R dla których tranzystor

pracuje w obszarze nienasycenia.

ID tranzystora MOS z kanałem typu p można wyrazić w funkcji VGS

oraz VDS jako:

ID = 0

dla VGS > VTp

V

I D = − β p ⋅ (VGS − VTp ) ⋅ VDS −

2

2

DS

I D = −β p ⋅

(V

GS

− VTp )

dla VGS ≤ VTp i 0 ≥ VDS > VGS - VTp

2

2

dla VGS ≤ VTp i VDS ≤ VGS - VTp

42

Wpływ rezystancji obciążenia na obszar pracy tranzystora

85

Tranzystor MOS z kanałem typu p, o wartości współczynnika βp = 1 mA/V2 i wartości VTp =

-0,2V pracuje w układzie jak na rysunku. Wyznaczyć zakresy wartości rezystancji R dla

których tranzystor pracuje w obszarze nasycenia i zakresy wartości R dla których tranzystor

pracuje w obszarze nienasycenia.

Z równania oczka drenu - prosta obciążenia:

VDS = VDD - IDR

dla różnych wartości R

Przy ustalonym VGS punkty pracy wypadają:

w obszarze nienasycenia (triodowym) dla

dużych wartości R,

w obszarze nasycenia dla małych wartości

R.

Wpływ rezystancji obciążenia na obszar pracy tranzystora

86

Tranzystor MOS z kanałem typu p, o wartości współczynnika βp = 1 mA/V2 i wartości VTp =

-0,2V pracuje w układzie jak na rysunku. Wyznaczyć zakresy wartości rezystancji R dla

których tranzystor pracuje w obszarze nasycenia i zakresy wartości R dla których tranzystor

pracuje w obszarze nienasycenia.

Widzimy, że dla tranzystora M1 z kanałem typu p

VGS < VTp

oraz VDD < VGS – VTp

Tranzystor M1 może zatem pracować w obszarze nasycenia. Warunkiem jest aby:

VDS ≤ VGS - VTp

Wartość VDS wyznaczamy jako

VDS = VDD - IDR

Otrzymujemy dla obszaru nasycenia

R≤

VGS − VTp − VDD

Podstawiamy wartość ID w obszarze nasycenia

− ID

R≤

2(VGS − VTp − VDD )

β p (VGS − VTp )2

Po podstawieniu wartości liczbowych otrzymujemy warunek

R ≤ 3,75 kΩ

dla tranzystora w obszarze nasycenia

43

Przyrządy elektronowe i jonowe – półprzewodniki z tkanką mózgową

87

Nerve cells on silicon chips. (a) Nerve cell from snail on

a large circular electrolyte/oxide/semiconductor (EOS)

capacitor. The silicon is insulated by a 10 nm thick film

of HfO2. (b) Nerve cell from rat on a linear array of EOS

field-effect transistors. Electronmicrograph after fixation.

The whole chip (gates, sources, drains) is insulated with a

10 nm thick film of SiO2.

P. Fromherz,International Electron Devices Meeting, 2008

• Praca mózgu związana jest z przetwarzaniem

sygnałów elektrycznych.

• Sygnały przenoszone są przez przepływ jonów w

wodzie.

• W półprzewodnikach i metalach prądy

przenoszone przez elektrony.

• Zróbmy przyrządy łączące te dwa środowiska i

próbujmy robić protezy nerwów.

Neuron steruje przepływem prądu w

tranzystorze

• A dlaczego nie dołączyć automatyki i nie

próbować systemów mikro/nano-bio-elektroautomatycznych (-mechanicznych -chemicznych)?

Mikroelektrody wszczepialne do nerwów

Mikroelektrody i układy mikroelektroniczne wszczepialne do nerwów

88

A 64-site eight-channel stimulating probe with sites on

400 µm centers and with CMOS electronics for stimulus

generation, recording, and self-test.

K.D. Wise i in. Proc. IEEE, vol. 96, 1184, 2008

44

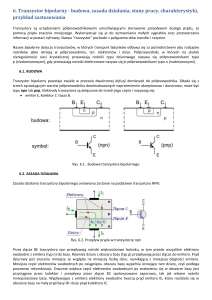

Tranzystory MOS dużej mocy

• Struktura pionowa z kanałem typu n.

Podłoże Si typu n stanowi dren.

89

• Struktura pozioma z kanałem typu n, o

zwiększonym napięciu przebicia.

• Małe pojemności CGS , CGD i CDS.

• Wykorzystywana w układach małej i

średniej częstotliwości dużej mocy.

• Wykorzystywana w układach mocy

wysokiej częstotliwości.

• Dobre wykorzystanie powierzchni Si,

duże pojemności.

• Komplementarne tranzystory z kanałami

typu p możliwe, ale niestosowane z uwagi

na niższe ruchliwości dziur niż

elektronów, co prowadzi do niższych fmax.

• Istnieją komplementarne tranzystory z

kanałami typu p.

Tranzystory MOS jako czujniki chemiczne

Przykład -

90

Ion-sensitive field-effect transistor (ISFET)

• W tranzystorze ISFET metal bramki jest zastąpiony przez badany elektrolit.

• Jony osadzające się na dielektryku bramki zmieniają napięcie progowe tranzystora,

co jest wykrywane elektrycznie.

• W MOSFETach wykorzystywanych jako czujniki chemiczne jony, cząsteczki lub

rodniki wiążące się z materiałem bramki lub kanału powodują zmianę

charakterystyk elektrycznych tranzystora.

45

91

Inne tranzystory polowe

92

Złączowy tranzystor polowy

JFET – junction field effect transistor

46

Złączowy tranzystor polowy

JFET – junction field effect transistor

93

• Dopóki złącze pn nie jest spolaryzowane w

kierunku przewodzenia, to jego prąd, czyli

prąd bramki IG ≈ 0.

• Warstwa opróżniona złącza pn

spolaryzowanego zerowo lub zaporowo

tworzy izolację pomiędzy bramką a źródłem

i drenem.

• Ale elektrony mogą przewodzić prąd w

nieopróżnionym obszarze typu n, pomiędzy

źródłem a drenem.

Złączowy tranzystor polowy

JFET – junction field effect transistor

94

• Elektrony mogą przewodzić prąd w

nieopróżnionym obszarze typu n, pomiędzy

źródłem a drenem.

• Zaporowa polaryzacja bramki względem

źródła zwiększa szerokość w. opróżnionej –>

zwiększa rezystancję kanału -> zmniejsza ID .

• Zwiększenie VDS zwiększa szerokość w.

opróżnionej w kanale, w pobliżu drenu –

„zaciska” tam kanał.

47

Złączowy tranzystor polowy z kanałem typu n

95

Prosty model przy założeniu skupienia elektronów w kanale w jednej płaszczyźnie i małego natężenia E

• W obszarze nasycenia, gdy

• W obszarze triodowym, gdy

VGS > VTn

VGS > VTn

VDS > VGS – VTn > 0 V

0 V < VDS < VGS - VTn

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

ID

I D = βn ⋅

(VGS − VTn )2

2

β n = μ nC pn

W

L

Cpn – pojemność złączowa

bramka-kanał na

jednostkę powierzchni

Obszar nasycenia

VGS < VTn

odcięcie

ID ≈ 0

Złączowy tranzystor polowy z kanałem typu n

96

Prosty model przy założeniu skupienia elektronów w kanale w jednej płaszczyźnie i małego natężenia E

• W obszarze nasycenia, gdy

β n = μ n C pn

VGS > VTn

VDS > VGS – VTn > 0 V

I D = βn ⋅

(VGS − VTn )2

2

W

L

Cpn – pojemność złączowa

bramka-kanał na

jednostkę powierzchni

ID

VGS < VTn

odcięcie

ID ≈ 0

48

Złączowe tranzystory polowe (JFET)

z kanałami typu n i typu p

97

• JFET z kanałem typu n

VTn < 0

• JFET z kanałem typu p

VTp > 0

Typowa polaryzacja

Typowa polaryzacja

VGS < 0

VGS > 0

VDS > VGS – VTn > 0 V

VDS < VGS – VTn < 0 V

ID

Przeciwne znaki

napięcia progowego,

prądów i napięć!

ID

98

Tranzystory MESFET

(metal semiconductor field effect transistors)

49

J.E Lilienfeld - wynalazek tranzystora MESFET – 1930 r.

Tranzystory MESFET

99

100

(metal semiconductor field effect transistors)

Wykorzystują warstwę opróżnioną

złącza metal-półprzewodnik do

sterowania szerokością kanału

(ładunkiem nośników prądu w kanale).

Przebieg charakterystyk w pierwszym

przybliżeniu podobny jak dla JFET.

Tranzystor z kanałem typu n ma

ujemne napięcie progowe.

Najszersze zastosowanie –

niskoszumowe wzmacniacze w

telefonii komórkowej, wykonane na

podłożu GaAs lub InP.

50

Półprzewodnik o dużej szerokości przerwy energetycznej może być

wykorzystany zamiast tlenku w strukturze podobnej do MOS

101

• Ruchliwość elektronów w związkach półprzewodnikowych IIIV

np. InxGa1-xAs jest dużo większa niż w krzemie.

• Pożądane jest więc wykorzystanie tego materiału na kanały

tranzystorów MOS dużo szybszych niż krzemowe.

• Ale znane tlenki na powierzchni większości półprzewodników

innych niż Si są niestabilne elektrycznie tworzą niemożliwe do

kontrolowania pułapki ładunku elektrycznego.

• Zamiast dielektryka bramki w postaci tlenku używa się więc

półprzewodnika o szerokości przerwy energetycznej większej niż

Eg kanału.

• Na przykład w tranzystorach HEMT z kanałami z InxGa1-xAs

zamiast dielektryka bramki używa się In0.52Al0.48As.

HEMT 2008 ft 600

GHz - overshoot

Tranzystor HEMT (high electron mobility transistor)

102

Tranzystor HEMT (high electron mobility transistor) o rekordowo wysokiej częstotliwości

granicznej fT = 628 GHz (2008 r.)

- z kanałem z InAs

- oraz In0.52Al0.48As jako materiałem bramki o dużej szerokości przerwy energetycznej – w

roli izolatora bramki

Au – metal bramki

Au – metal drenu

pasywacja

Bramka o długości

LG = 30 - 50 nm.

źródło

In0.52Al0.48As jako

izolator bramki

kanał

In0.53Ga0.47As/InAs/In0.53Ga0.47A

s

2/5/3 nm

- na podłożu InP

Obraz przekroju z transmisyjnego

mikroskopu elektronowego

MIT - Kim, Alamo, IEEE Electron Dev. Lett, v.29, p830, 2008

51

HEMT 2008 ft 600

GHz – overshoot -2

Tranzystor HEMT (high electron mobility transistor)

103

HEMT o rekordowo wysokim fT = 628 GHz (2008 r.)

- z kanałem z InAs , oraz In0.52Al0.48As jako materiałem bramki, LG = 30 – 50 nm

Au – metal bramki

Au – metal drenu

pasywacja

Bramka o długości

LG = 30 - 50 nm.

źródło

In0.52Al0.48As jako

izolator bramki

kanał

In0.53Ga0.47As/InAs/In0.53Ga0.47A

s

2/5/3 nm

- na podłożu InP

MIT - Kim, Alamo, IEEE Electron Dev. Lett,

v.29, p830, 2008

• W półprzewodnikach III-V, w temperaturze pokojowej λmn > 100 nm.

• Ale tylko dla niewielkich napięć dren – źródło.

• Ocenia się, że dla realnie pracujących przyrządów transport balistyczny

powinien dominować przy długości kanału Lg < 20 nm.

• Jesteśmy blisko!

HEMT o rekordowo wysokim fT = 628 GHz (2008 r.)

104

- z kanałem z InAs , oraz In0.52Al0.48As jako materiałem bramki, LG = 30 – 50 nm

HEMT 2008 ft 600

GHz – overshoot - 3

fmax – graniczna częstotliwość przy której tranzystor może wzmacniać moc,

to jest przy której Pwy / Pwe > 1

fT – graniczna częstotliwość przy której tranzystor może wzmacniać prąd, to

jest przy której, dla składowej zmiennej Id / Ig > 1

MIT - Kim, Alamo, IEEE Electron Dev. Lett, v.29, p830, 2008

52

HF transistors fmax-fT

Rekordowe częstotliwości fT i fmax tranzystorów oraz częstotliwości pracy układów fcircuit

105

(2015 r)

fmax – graniczna częstotliwość przy której tranzystor może wzmacniać moc,

to jest przy której, dla składowej zmiennej Pout / Pin > 1

fT – graniczna częstotliwość przy której tranzystor może wzmacniać prąd, to

jest przy której, dla składowej zmiennej Id / Ig > 1

sub-mm HEMT amp 320GHz - 3

Wzmacniacze z tranzystorami HEMT dla zakresu fal submilimetrowych 106

0,5 mm

Parametry tranzystorów HEMT we wzmacniaczu

1,2 mm

Czterostopniowy scalony monolityczny

wzmacniacz dla f = 320 GHz z tranzystorami

HEMT na podłożu z InP.

Pojedynczy stopień wzmacniacza – kaskoda.

A. Tessmann et al., IMS 2010, pp. 53-56

Parametry wzmacniacza z tranzystorami HEMT

o długości kanałów L = 35 nm.

53

sub-mm HEMT amp 320GHz - 4

Wzmacniacze z tranzystorami HEMT dla zakresu fal submilimetrowych 107

0,5 mm

Parametry tranzystorów HEMT we wzmacniaczu

1,2 mm

Czterostopniowy scalony monolityczny

wzmacniacz dla f = 320 GHz z tranzystorami

HEMT na podłożu z InP.

G0 = S 21

= 10

S 21 db

10

2

S 21dB = 20 log S 21

G0 – hipotetyczna wartość

wzmocnienia mocy przy

dopasowaniu impedancji

na wejściu i wyjściu oraz

przy transmisji sygnału

tylko z wejścia do wyjścia

Parametry wzmacniacza z tranzystorami HEMT

o długości kanałów L = 35 nm.

A. Tessmann et al., IMS 2010, pp. 53-56

sub-mm HEMT amp 480GHz - 1

Wzmacniacze z tranzystorami HEMT dla zakresu fal submilimetrowych 108

0,32 mm

Metal z falowodami WR-2.2

- wejściowym i wyjściowym.

Płytka InP 0,9 mm × 0,32 mm ze

wzmacniaczem. Sygnały sprzężone z

falowodami przy pomocy dipoli.

0,9 mm

Niskoszumowy pięciostopniowy scalony

monolityczny wzmacniacz dla f = 480 GHz z

tranzystorami HEMT na podłożu z InP.

HEMT: dugość kanału < 50 nm,

transkonduktancja 2300 S/mm,

fmax = 1200 GHz, fT = 580 GHz.

1 fF = 10-15 F

W.R.Deal et al., IEEE MWCL, vol. 20,

pp. 289-291, 2010

Pojemności bramka-źródło CGS oraz bramka-dren

CGD tranzystorów HEMT we wzmacniaczu

54

sub-mm HEMT amp 480GHz - 2

Wzmacniacze z tranzystorami HEMT dla zakresu fal submilimetrowych 109

W.R.Deal et al., IEEE MWCL, vol. 20,

pp. 289-291, 2010

0,32 mm

Metal z falowodami WR-2.2

- wejściowym i wyjściowym.

Płytka InP 0,9 mm × 0,32 mm ze

wzmacniaczem. Sygnały sprzężone z

falowodami przy pomocy dipoli.

S 21dB = 20 log S 21

0,9 mm

Niskoszumowy pięciostopniowy scalony

monolityczny wzmacniacz dla f = 480 GHz z

tranzystorami HEMT na podłożu z InP.

HEMT: dugość kanału < 50 nm,

transkonduktancja 2300 S/mm,

fmax = 1200 GHz, fT = 580 GHz.

G0 = S 21

= 10

S 21 db

10

2

G0 – hipotetyczna wartość wzmocnienia

mocy przy dopasowaniu impedancji na

wejściu i wyjściu oraz przy transmisji

sygnału tylko z wejścia do wyjścia

Parametry S wzmacniacza

Chemiczna modyfikacja przewodności powierzchni diamentu

110

Dołączenie odpowiedniej cząsteczki do powierzchni diamentu może

powodować powstanie powierzchniowej warstwy z dziurami –

przewodzącego kanału

R.S. Sussmann, CVD Diamond for Electronic Devices and Sensors, Wiley 2009

55

Tranzystory polowe

111

(z kanałami typu n)

Prosty model przy założeniu skupienia elektronów w kanale w jednej płaszczyźnie i małego natężenia E

• W obszarze nasycenia, gdy

• W obszarze triodowym, gdy

VGS > VTn

VGS > VTn

VDS > VGS – VTn

0 V < VDS < VGS - VTn

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

(VGS − VTn )

2

I D = βn ⋅

β n = μ nCchar

W

L

Cchar – pojemność

bramka-kanał na

jednostkę powierzchni

2

ID

Obszar nasycenia

VGS < VTn

odcięcie

ID ≈ 0

Małosygnałowy schemat zastępczy tranzystora polowego

112

(prosty)

Bramka

Dren

Źródło

Graniczna częstotliwość wzmocnienia prądowego tranzystora fT to taka częstotliwość przy

której ekstrapolowane wzmocnienie prądowe tranzystora spada do wartości 1.

fT ≤

1

2π ⋅ tt

fT ≈

gdzie tt – czas przelotu elektronów (dziur) od źródła do drenu.

gm

gm

=

2πWLCox 2π (CGS + CGD )

Graniczna częstotliwość wzmocnienia mocy tranzystora MOS fmax to taka częstotliwość

przy której ekstrapolowane wzmocnienie mocy tranzystora spada do wartości 1.

f max ≈

fT

8π ⋅ rgg 'CGD

56

113

Dziękuję za uwagę!

57