Podstawy Mikroelektroniki

dr hab. inż Piotr Płotka

pok. 301

tel. 347-1634

e-mail: [email protected]

konsultacje:

środa

8:15 - 9:00

czwartek 13:15 – 14:00

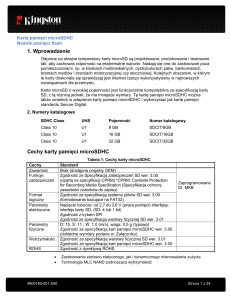

Podstawy Mikroelektroniki - materiały pomocnicze:

eti.pg.edu.pl

O Wydziale

Katedry

Katedra Systemów Mikroelektronicznych

Dydaktyka

Przedmioty

Podstawy Mikroelektroniki

(materiały dla studentów)

1

Literatura:

B. Razavi, "Fundamentals of Microelectronics", Wiley, 2006

H. Veendrick, "Nanometer CMOS ICs: from Basics to ASICs", Springer, 2008

R. Jacob Baker, "CMOS: Circuit Design, Layout, and Simulation", Wiley, 2008,

- rysunki, przykłady, modele Spice i Cadence: http://cmosedu.com/cmos1/book.htm

Literatura dodatkowa:

A.S. Sedra, K.C. Smith, "Microelectronic Circuits", Oxford, 2007

J.C. Whitaker, "Microelectronics", 2nd. ed., CRC Press 2006

B. El-Kareh, "Silicon Devices and Process Integration. Deep Submicron and NanoScale Technologies", Springer 2009

N. Collaert, "CMOS Nanoelectronics: Innovative Devices, Architectures, and

Applications", Pan Stanford Publ. 2012

G. Cerofolini, "Nanoscale Devices. Fabrication, Functionalization, and

Accessibility from the Macroscopic World", Springer 2009

A. Korkin, F. Rosei, "Nanoelectronics and Photonics. From Atoms to Materials,

Devices, and Architectures", Springer 2008

4

Technologia Waszych Układów

Scalonych CMOS?

2

5

2014 r. - Rynek

układów

scalonych

ok. USD 340E+9.

Rynek systemów

- ok. 4 razy

więcej.

P. Garrou, Solid State Technology,

May 05, 2015

6

Zamiast składać systemy z wielu typowych

układów lub programować programowalne

tablice bramek FPGA (Field Programable

Gate Arrays) inżynier elektronik projektuje

specjalizowane układy scalone.

(ASICs – Application Specific Integrated

Circuits)

I będzie to robił coraz częściej.

3

7

Największe firmy

półprzewodnikowe w 2010 r.

(wartość sprzedaży w milionach US$)

- foundry – firmy

produkujące wyroby

zaprojektowane i

sprzedawane przez

inne (fabless)

- fabless – firmy

projektujące i

sprzedające wyroby,

nie mają własnych

fabryk, wytwarzanie

zlecają innym

(foundry)

"Analysis: Memory, foundries gain in 1H10 chip ranks",

Solid State Technology, Aug. 2, 2010

Fabless – Foundry Industry.

8

W 2011 r. łączne dochody półprzewodnikowych firm "fabless" i

"foundry" przekroczyły łączne dochody firm projektujących i

wytwarzających swoje wyroby, w tym procesory i pamięci.

Najwięcej tranzystorów, ponad 109, miał układ zaprojektowany w

firmie "fabless" i wykonany w firmie "foundry".

4

Fabless – Foundry Industry.

9

Pete Singer

Solid State Technology, May 2012

Fabless – Foundry

Industry.

10

2012 r.

Pete Singer

Solid State Technology,

May 2012

5

Koszt budowy fabryki układów scalonych

11

Samsung has announced a

$14.7B (USD 14.7 E+9)

plan to build a new wafer fab south

of Seoul - slated to begin production

in 2H17.

P. Garrou, Solid State Technology,

May 05, 2015

Style projektowania układów scalonych CMOS

Specjalizowane układy

scalone (ASICs)

Całkowicie

specjalizowane

Logiki

programowalne

Pół specjalizowane

Standardowe

komórki

12

Standardowe układy

scalone

FPGA

połączenia między

bramkami programowane

po wytworzeniu

CPLD – złożone

programowalne

przyrządy logiczne

Tablice i zbiory

bramek

6

Style projektowania układów scalonych CMOS

13

Specjalizowane układy

scalone (ASICs)

Całkowicie

specjalizowane

Wszystkie elementy i warstwy układu projektowane przez zamawiającego.

Daje to wiele możliwości, ale wymaga olbrzymiego wysiłku projektowego.

Duże ryzyko niepowodzenia

ASIC – Application Specific Integrated Circuit

ASIC_full_custom

ASIC_std_cell

Style projektowania układów scalonych CMOS

14

Specjalizowane układy

scalone (ASICs)

Całkowicie

specjalizowane

Pół specjalizowane

Standardowe

komórki

Wykorzystuje się biblioteki wzorów masek i opisów elektrycznych dla

rozmieszczenia standardowych komórek (standard cell) lub podukładów

na płytce krzemu. Możliwe różne stopnie złożoności podukładów.

7

ASIC_gate_array

Style projektowania układów scalonych CMOS

15

Specjalizowane układy

scalone (ASICs)

Pół specjalizowane

Tablice

bramek

Wykorzystują prefabrykowane tablice bramek (gate arrays) rozmieszczone na

płytce krzemowej. Projektuje się połączenia elektryczne – warstwy metalizacji

FPGA

Style projektowania układów scalonych CMOS

16

Logiki

programowalne

FPGA

połączenia między

bramkami programowane

po wytworzeniu

FPGA (Field Programable Gate Arrays) wykorzystują prefabrykowane tablice

bramek rozmieszczone na płytce krzemowej łącznie z wielu krzyżującymi się

liniami metalizacji. Bramki są łączone z tymi liniami przez uruchomienie

specjalnych programów. Na przykład poprzez włączenie bramek transmisyjnych,

czyli pełniących rolę zwór. Coraz częściej używane są układy reprogramowalne.

8

FPGA w porównaniu z ASIC

FPGA

17

ASIC

• Tańsze w małych seriach

i/lub przy niewielkich

ilościach bramek.

• Szybsze.

• Dużo mniejszy pobór mocy.

• Wymagają pracochłonnego

projektowania przez wysoko

kwalifikowanych inżynierów,

przy użyciu drogiego

oprogramowania.

• Łatwe i szybkie

projektowanie i poprawianie.

• Opłacalne w dużych seriach

przy dużych ilościach

bramek.

Liczba bramek (miliony)

Średnia Liczba Bramek w Specjalizowanych Układach Scalonych (ASIC) 18

Pamięć

Logika

Rok produkcji

•

Przy odpowiednio dużej ilości bramek stosowanie specjalizowanych układów

scalonych (ASIC) jest tańsze niż programowalnych tablic bramek (FPGA).

•

Pobór mocy może być 10 razy mniejszy.

9

Development activities at a fabless IC company

ES

19

QS

ES - Engineering Sample

QS - Qualifiable Samples, Customer Samples or Shippable Samples

RTL - Register Transfer Level

NL – Netlist

GDSII - Graphic Data System II, photomask description format

IP - intellectual property block

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

Typical ASIC development time diagram at a fabless IC company

20

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

10

Schemat blokowy systemu Bluetooth zrealizowanego z komórek

standardowych

21

SoC – System on Chip

Źródło: Texas Instruments

Powiązania firmy „fabless” z innymi przy wytwarzaniu produktu

22

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

11

Firma „fabless” może zlecić fizyczny projekt lub nadzór

wyspecjalizowanej firmie

FABLESS

23

Schemat

ideowy

Gotowe

częśći

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

24

Typowe etapy

projektowania systemu w

chipie (SoC)

R. Kumar, Fabless Semiconductor

Implementation, McGraw-Hill, 2008

12

Przykładowy podział bloków telefonu komórkowego na układy scalone

25

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

Many designs on one wafer

26

Photograph of an MPW wafer along with

an enlarged image of one reticle

containing approximately 40 designs.

(Source: MOSIS)

R. Kumar, Fabless

Semiconductor Implementation,

McGraw-Hill, 2008

Plot of nine different designs assembled as

one MPW reticle. (Source: EuroPractice)

13

Ewolucja obudów układów scalonych

27

BGA – Ball Grid Array

R. Kumar, Fabless

Semiconductor Implementation,

McGraw-Hill, 2008

Through Silicon Via (TSV) and Through Silicon Stacking (TSS)

28

TSV (Through Silicon Via) process implemented after complete fabrication of the

silicon IC where large vias are etched from the backside. (Source: IMEC)

Four die stack using TSV process. (Source IMEC)

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

14

Through Silicon Via (TSV) and Through Silicon Stacking (TSS)

29

A 3-die stack using TSVs etched prior to completion of the BEOL (back end of

line) processing in the silicon wafer fab. (Source: IMEC)

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

30

Przykładowe koszty

opracowania ASIC w

technologii 180 nm

(w 2007 r.)

R. Kumar, Fabless

Semiconductor Implementation,

McGraw-Hill, 2008

15

Przykładowe układy scalone wyprodukowane z użyciem celowo wprowadzanych

naprężeń sieci krystalicznej krzemu dla zwiększenia ruchliwości (szybkości przelotu)

dziur i elektronów

31

Technology Node [nm] – rozmiar charakterystyczny, połowa sumy szerokości najwęższego paska i

najwęższej przerwy we wzorze na powierzchni półprzewodnika, w danej technologii.

Procesory firm Intel i AMD

INTEL 2010 r.

D.M. Fleetwood et al., Defects in Microelectronic Materials and Devices, CRC Press 2008

Przykładowy procesor firmy INTEL z tranzystorami „tri-gate” (FinFET)

32

2014:

Intel –procesor Broadwell z

tranzystormi o rozmiarze

charakterystyczym 14 nm.

Pobiera o 30% mniej mocy niż

Haswell (22 nm)

Oct. 07 2013:

TSMC – 16-nm FinFET

technology

source: Intel, 2014

electrode

Gate high-k

dielectric

source: M. Bohr, K. Mistry,

Intel’s Revolutionary 22 nm Transistor Technology, May, 2011

16

33

Nagrody Nobla za odkrycia i wynalazki

związane z przyrządami – 1/2

?

?

2014

Isamu Akasaki, Hiroshi Amano i Shuji Nakamura

- za sprawne diody świecące niebieskim

światłem, co pozwoliło wytworzyć jasne i

energooszczędne źródła światła

2010

Andre Geim, Konstantin Novoselov – za

doświadczenia nad dwuwymiarowym grafenem

2009

Charles K. Kao – za włókna optyczne do

przesyłania światła na duże odległości

2007

A. Fert, P. Grünberg- za odkrycie zjawiska

gigantycznego magnetooporu

2000

A. J. Heeger, A. G. MacDiarmid, H.

Shirakawa - za odkrycie i rozwijanie

polimerów przewodzących

2000

Z. I. Alferov - za opracowanie heterostruktur

półprzewodnikowych dla optoelektroniki

1998

R. B. Laughlin, H. L. Störmer, D. C. Tsui - za

odkrycie cieczy kwantowej ze wzbudzeniami

o ładunkach ułamkowych - ułamkowe

kwantowe zjawisko Halla

1987

J. G. Bednorz, K. A. Müller - za odkrycie

wysokotemperaturowego nadprzewodnictwa

w materiałach ceramicznyc

1985

K. von Klitzing - za kwantowe zjawisko Halla

1973

Leo Esaki - za doświadczalne okrycia

dotyczące tunelowania w półprzewodnikach

1972

J. Bardeen, L. N. Cooper, R. Schrieffer - za

teorię zjawiska nadprzewodnictwa (teorię

BCS)

1964

C. H. Townes, N. G. Basov, A. M. Prokhorov za badania, które doprowadziły do laserów i

maserów

1956

W. B. Shockley, J. Bardeen, W. H. Brattain za badania nad półprzewodnikami i odkrycie

tranzystora

Willard S. Boyle, George E.

Smith - za wynalezienie –

sensora CCD

34

Nagrody Nobla za odkrycia i wynalazki

związane z przyrządami – 2/2

H. Kroemer - za opracowanie

tranzystora heterozłączowego

Jack S. Kilby - za wkład w

wynalezienie układu

scalonego

I. Giaever - za doświadczenia

nad tunelowaniem w

nadprzewodnikach

B. D. Josephson - za teorię

tunelowania w złączu

nadprzewodników

17

Historia rozwoju przyrządów i głównych rodzin cyfrowych układów scalonych

35

V.F. Pavlidis, E.G. Friedman, "Three-dimensional Integrated Circuit Design", MK 2008

Klasyfikacja nowych przyrządów dla technologii informacyjnych

36

International Technology Roadmap for Semiconductors, ITRS 2013 Edition

18

Układy Scalone

37

Wynalezione przez

Jacka Kilby

1958r. - Texas Instruments

• Elementy wykonane w pojedynczej płytce Ge,

• trawionej na wskroś dla izolacji elementów;

• drutowe połączenia między elementami

Strona z notatnika J.S. Kilby ukazująca

generator z przesuwnikiem fazy

wykonany z płytki Ge metodą dyfuzji.

Strona z notatnika J.S. Kilby ukazująca

przerzutnik wykonany z płytki Ge metodą

dyfuzji.

J.S. Kilby, IEEE Trans. Electron Dev., v.23, s.648, 1976

Wczesne układy scalone – Texas Instruments

Pierwszy układ scalony na germanie

wykonany przez J. Kilby

w Texas Instruments - 1958

38

Pierwszy planarny krzemowy układ scalony

wykonany techniką planarną. Przerzutnik z

aluminiową metalizacją, Fairchild, 1961 –

pomysł Roberta Noyce, 1958

“A Solid State of Progress,”

Fairchild Camera and Instrument Corporation, 1979,

G.E.Moore, Proc. IEEE, v.86,s.53-62, 1998

19

Przykładowy inwerter CMOS z tranzystorami o długości kanałów 50 nm

39

VDD = 1,2 V

MP

IDp

IDn

Vwy

Vwe

MN

nMOS w CMOS _1

Idealny tranzystor nMOS w inwerterze CMOS

40

IDN

MN

Obszar nasycenia

VGS < VTn

odcięcie

ID ≈ 0

VDD > 0 V

MP

Vwy

Vwe

MN

Prąd drenu ID idealnego tranzystora nMOS w

funkcji napięcia dren-źródło VDS (charakterystyki

wyjściowe). Napięcie progowe VTn=1,0 V.

20

Prosty model charakterystyk tranzystora MOS

– tranzystor MOS z kanałem typu n wzbogacanym

D

IDn

G

• W zakresie nasycenia, gdy

• W triodowym, gdy

β n = μ nCox

VGS > VTn

W

L

VGS > VTn

VDS > VGS – VTn > 0 V

0 V < VDS < VGS - VTn

V2

I D = β n ⋅ (VGS − VTn ) ⋅VDS − DS

2

S

41

I D = βn ⋅

(VGS − VTn )2

2

Cox =

Obszar nasycenia

ε SiO 2ε 0

tox

Charakterystyka

idealnego MOSFETa,

VTn = 1,0 V

VGS < VTn

odcięcie

ID ≈ 0

gdzie:

VTn – napięcie progowe nMOS,

Cox – pojemność bramki na jednostkę powierzchni,

L, W – długość i szerokość kanału,

µn - ruchliwość elektronów

Tranzystor pMOS w inwerterze CMOS

obszar odcięcia: VGS >= VTp

MP

42

I Dp ≈ 0

obszar triodowy: VGS < VTp , 0 V > VDS > VGS - VTp

V2

I Dp = − β p ⋅ (VGS − VTp )⋅VDS − DS

2

VDD > 0 V

IDp

β p = μ p Cox

W

L

obszar nasycenia: VGS < VTp , VDS < VGS – VTp < 0 V

I Dp = − β p ⋅

MP

(V

− VTp )

2

GS

2

ID

Vwy

D

MN

Vwe

IDp < 0

VTp < 0

µp = µn/3 - dlatego |ID| ok. 3 razy

mniejszy dla pMOS niż dla nMOS

przy jednakowych |VGS – VTn(p)|

G

S

21

Przełączanie inwertera CMOS

VDD > 0 V

0

Przy skoku Vwe od 0 V do VDD tranzystor Mp

szybko jest zatykany. Pojemność obciążenia CL

jest rozładowywana od Vwy = VDD do 0 V przez

Mn.

Mp

VDD

Mn

CL

43

Vwy

Vwe

przełączanie_nMOS_w_CMOS

Przełączanie inwertera CMOS

Przy skoku Vwe od 0 V do VDD tranzystor Mp

szybko jest zatykany. Pojemność obciążenia CL

jest rozładowywana od Vwy = VDD do 0 V przez

Mn.

VDD

0

44

Mn

Vwe

CL

Vwy Rozpatrzmy na razie pracę Mn w zakresie

nasycenia, przy Vwy > VDD – VTN

Pojemność CL jest rozładowywana prądem drenu

tranzystora Mn

CL

dVwy

dt

=−

μ n*Cox W

2

⋅

L

⋅ (VDD − VTN )

2

Konstruktorom zależy często na zwiększaniu częstotliwości pracy układu, czyli

zwiększaniu dVwy/dt. Zależność powyższa wskazuje, że w tym celu należy

zmniejszać L.

Należy też pamiętać, że czas przełączania Mn nie może być krótszy niż czas

przelotu elektronów ze źródła do drenu. To też wymaga skracania L dla skracania

czasu przełączania.

Zmniejszenie długości kanału L nazywamy „skalowaniem tranzystora”.

przełączanie_nMOS_w_CMOS - 2

22

Pobór mocy przez inwerter CMOS

45

W nowszych rozwiązaniach technologicznych, przy grubości tlenku bramki

mniejszej od 5 nm i przy zastosowaniu cienkiego dwutlenku hafnu moc

związana z prądem upływu bramki może być porównywalna z mocą pobieraną

na przeładowanie pojemności w układzie. Przy długościach kanałów krótszych

niż 50 nm istotna może być też strata mocy związana z prądem upływu drenźródło.

2

Ptot = (I D )VGS =0 ⋅VDD + (I G )VGS =VDD ⋅VDD + C L ⋅ VDD

⋅f

moc związana z

prądem upływu D-S

moc związana z

prądem upływu bramki

moc tracona na przeładowanie CL

Zmniejszenie rozmiarów tranzystorów, skalowanie, czyli zwiększenie upakowania

na jednostce powierzchni krzemu, przy zachowaniu VDD prowadzi do zwiększania

wydzielanej mocy na jednostce powierzchni. Wzrasta temperatura układu, co

może prowadzić do zniszczenia.

Skalując tranzystory należy zmniejszać moc wydzielaną w pojedynczej bramce.

Obniżać VDD, a zatem również napięcia progowe VTn i VTp. To powoduje

konieczność zmniejszania grubości tlenku bramki tox.

Skalowanie tranzystorów CMOS przy zachowaniu

stałego natężenia pola elektrycznego

46

Chcemy:

• Produkować szybsze tranzystory w układach scalonych;

• produkować bardziej skomplikowane układy – zmieścić więcej tranzystorów

na jednostce powierzchni półprzewodnika.

Osiągamy to przez:

Zmniejszenie rozmiarów tranzystorów – długości kanałów w tranzystorach

MOS λ razy. Zwiększenie upakowania tranzystorów – oczywiste.

Zmniejszenie długości kanałów prowadzi do zmniejszenia czasów przelotu

elektronów i dziur ze źródeł do drenów tranzystorów – w efekcie do

zwiększenia „szybkości”.

Należy to robić przy :

• zachowaniu stałych natężeń pola elektrycznego w tranzystorach – aby uniknąć

przebić elektrycznych;

• zachowaniu stałej wartości mocy wydzielanej na jednostce powierzchni

układu scalonego – aby uniknąć przegrzania układu i jego stopienia.

P.K.K. Ko, "Approaches to scaling", Advanced MOS device physics, VLSI electronics

microstructure science, Vol. 18, Academic Press, pp. 1-37, 1989

23

47

30 Years of CMOS Scaling 1978 - 2008

Mark Bohr, The New Era of Scaling in an SoC World, 2009 ISSCC

Współczynniki skalowania tranzystorów CMOS przy zachowaniu stałych

natężeń pól elektrycznych i gęstości mocy

Otrzymujemy

Zmieniamy

Parametr

Skalowanie

Rozmiar (tox, rj, W, L)

48

Parametr w j. angielskim

przed

po

L ...

L/s ...

Dimension (tox, rj, W, L)

Napięcie zasilania (VDD)

VDD

VDD/s

Supply voltage (VDD)

Napięcie progowe (VTn, VTp)

VTn ..

VTn/s ...

Threshold voltage (VTn, VTp)

Koncentracje domieszek (NA, ND) ND ..

ND ·s ..

Dopant concentrations (NA, ND)

Pojemność charakt. bramki (Cox)

Cox

Cox·s

Specific gate capacitance (Cox)

Pojemność bramki (CG)

CG

CG/s

Gate capacitance (CG)

s – współczynnik skalowania

Po skalowaniu

Przed skalowaniem

Cox 0 =

CG 0 =

tox1 = tox 0 / s

ε SiO 2ε 0

tox 0

ε SiO 2ε 0 LW

tox 0

Cox1 =

CG 1 =

L1 = L0 / s

ε SiO 2ε 0 ⋅ s

tox1

= Cox1 ⋅ s

ε SiO 2ε 0 s ⋅ LW

tox1 ⋅ s ⋅ s

W1 = W0 / s

=

CG 0

s

24

Współczynniki skalowania tranzystorów CMOS przy zachowaniu stałych

natężeń pól elektrycznych i gęstości mocy

Parametr

Skalowanie

Otrzymujemy

Zmieniamy

przed

Parametr w j. angielskim

po

Rozmiar (tox, rj, W, L)

L ...

L/s ...

Dimension (tox, rj, W, L)

Napięcie zasilania (VDD)

VDD

VDD/s

Supply voltage (VDD)

Napięcie progowe (VTn, VTp)

VTn ..

VTn/s ...

Threshold voltage (VTn, VTp)

Koncentracje domieszek (NA, ND) ND ..

ND ·s ..

Dopant concentrations (NA, ND)

Pojemność charakt. bramki (Cox)

Cox

Cox·s

Specific gate capacitance (Cox)

Pojemność bramki (CG)

CG

CG/s

Gate capacitance (CG)

Prąd drenu (ID)

ID

ID/s

Drain current (ID)

Gęstość prądu (J)

J

J ·s

Current density (J)

Po skalowaniu

Przed skalowaniem

tox1 = tox 0 / s

L1 = L0 / s

VDD1 = VDD 0 / s

W0 (VGS 0 − VTn 0 )

⋅

2

L0

2

I D 0 = μ nCox 0

W1 = W0 / s

VTn , p1 = VTn , p 0 / s

W0 ⋅ s (VGS 0 / s − VTn 0 / s )

⋅

= I D0 / s

s ⋅ L0

2

2

J=

I D1 = μ nCox 0 ⋅ s

ID

W ⋅ rj

Współczynniki skalowania tranzystorów CMOS przy zachowaniu stałych

natężeń pól elektrycznych i gęstości mocy

Zmieniamy

Parametr

Otrzymujemy

49

Rozmiar (tox, rj, W, L)

Skalowanie

przed

po

L ...

L/s ...

50

Parametr w j. angielskim

Dimension (tox, rj, W, L)

Napięcie zasilania (VDD)

VDD

VDD/s

Supply voltage (VDD)

Napięcie progowe (VTn, VTp)

VTn ..

VTn/s ...

Threshold voltage (VTn, VTp)

Koncentracje domieszek (NA, ND) ND ..

ND ·s ..

Dopant concentrations (NA, ND)

Pojemność charakt. bramki (Cox)

Cox

Cox·s

Specific gate capacitance (Cox)

Pojemność bramki (CG)

CG

CG/s

Gate capacitance (CG)

Prąd drenu (ID)

ID

ID/s

Drain current (ID)

Gęstość prądu (J)

J

J ·s

Current density (J)

Opóźnienie bramki (td)

td

td /s

Gate delay (td)

Przed skalowaniem

g m 0 = μ nCox 0 ⋅

td 0 ∝

CG 0

g m0

W0

⋅ (VGS 0 − VTn 0 )

L0

Po skalowaniu

g m1 = μ n Cox 0 ⋅ s

td1 ∝

W0 ⋅ s

⋅ (VGS 0 / s − VTn 0 / s ) = g m 0

s ⋅ L0

CG 1 CG 0 1

t

=

⋅

∝ d0

g m1

s g m0

s

25

Współczynniki skalowania tranzystorów CMOS przy zachowaniu stałych

natężeń pól elektrycznych i gęstości mocy

Parametr

Skalowanie

Otrzymujemy

Zmieniamy

przed

Parametr w j. angielskim

po

Rozmiar (tox, rj, W, L)

L ...

L/s ...

Dimension (tox, rj, W, L)

Napięcie zasilania (VDD)

VDD

VDD/s

Supply voltage (VDD)

Napięcie progowe (VTn, VTp)

VTn ..

VTn/s ...

Threshold voltage (VTn, VTp)

Koncentracje domieszek (NA, ND) ND ..

ND ·s ..

Dopant concentrations (NA, ND)

Pojemność charakt. bramki (Cox)

Cox

Cox·s

Specific gate capacitance (Cox)

Pojemność bramki (CG)

CG

CG/s

Gate capacitance (CG)

Prąd drenu (ID)

ID

ID/s

Drain current (ID)

Gęstość prądu (J)

J

J ·s

Current density (J)

Opóźnienie bramki (td)

td

td /s

Gate delay (td)

Moc zasilania (P)

P

P

/s2

Gęstość mocy (P/A)

P/A

(P/A)·1

Po skalowaniu

Przed skalowaniem

2

P0 ∝ CG 0 ⋅ VDD

0⋅ f

Power consumption (P)

Power density (P/Area)

2

CG 0 VDD

⋅ 20 ⋅ f ⋅s

s

s

P0 s s

P0

P1

= ⋅ ⋅ =

Area1 s 2 L W Area0

P1 ∝ CG1 ⋅ VDD1 ⋅ f =

Współczynniki skalowania tranzystorów CMOS przy zachowaniu stałych

natężeń pól elektrycznych i gęstości mocy

Zmieniamy

Parametr

Otrzymujemy

51

Skalowanie

Rozmiar (tox, rj, W, L)

przed

po

L ...

L/s ...

52

Parametr w j. angielskim

Dimension (tox, rj, W, L)

Napięcie zasilania (VDD)

VDD

VDD/s

Supply voltage (VDD)

Napięcie progowe (VTn, VTp)

VTn ..

VTn/s ...

Threshold voltage (VTn, VTp)

Koncentracje domieszek (NA, ND) ND ..

ND ·s ..

Dopant concentrations (NA, ND)

Pojemność charakt. bramki (Cox)

Cox

Cox·s

Specific gate capacitance (Cox)

Pojemność bramki (CG)

CG

CG/s

Gate capacitance (CG)

Prąd drenu (ID)

ID

ID/s

Drain current (ID)

Gęstość prądu (J)

J

J ·s

Current density (J)

Opóźnienie bramki (td)

td

td /s

Gate delay (td)

Moc zasilania (P)

P

/s2

Gęstość mocy (P/A)

P/A

(P/A)·1

Iloczyn moc·opóźnienie (td·Pg)

td·Pg

td·Pg

/s3

Ilość tranzystorów na cm2

Ilość

Ilość · s2

P

Power consumption (P)

Power density (P/Area)

Power-delay product (td·Pg)

Integration density (transistors/cm2)

P.K.K. Ko, "Approaches to scaling", Advanced MOS device physics, VLSI

electronics microstructure science, Vol. 18, Academic Press, pp. 1-37, 1989

26

32 nm CMOS

FUJITSU - 2007

53

Obrazy przekrojów z

elektronowego mikroskopu

transmisyjnego

nMOS

pMOS

Wykonane w technologii 45 nm.

Struktura z minimalnym odstępem,

140 nm, między bramkami z

polikrystalicznego krzemu. Widoczne

również obszary epitaksjalnego SiGe,

o kształtach jak S.

FUJITSU - T.Miyashita et al. IEDM 2007 S10P03

Reguły Projektowania 32 nm CMOS - FUJITSU - 2007

54

FUJITSU - T.Miyashita et al. IEDM 2007 S10P03

27

Przewidywane długości bramek w procesorach CMOS

55

International Technology Roadmap for Semiconductors, ITRS 2013 Edition

Przewidywane skalowanie „wewnętrznej” szybkości tranzystorów

56

Oszacowanie 1/t = I/(CV)

Przewidywane szybkości

oscylatorów pierścieniowych

International Technology Roadmap for Semiconductors, ITRS 2009 Edition

28

Maksymalna częstotliwość zegara, maksymalne napięcie zasilania VDD i (maksymalne

wymagane) napięcie progowe VTn , VTp dla układów scalonych CMOS

57

High performance – najlepsze właściwości.

Technology Node [nm] – połowa sumy szerokości

najwęższego paska i najwęższej przerwy we

wzorze na powierzchni półprzewodnika, w danej

technologii.

Mniejsza długość kanału:

Rok

pozwala stosować większe częstotliwości zegara

wewnątrz układu scalonego;

wymaga stosowania niższych napięć zasilania VDD

aby uniknąć przebić elektrycznych i przegrzania,

a napięcia progowe tranzystorów VTn i VTp muszą

być mniejsze niż VDD/2.

S.Chatterjee et al., Circuit Design Techniques

at 0.5V, Springer 2007

Maksymalna częstotliwość zegara, maksymalne napięcie zasilania VDD i (maksymalne

wymagane) napięcie progowe VTn , VTp dla układów scalonych CMOS

58

Procesory są konstruowane dla dużej szybkości

działania lub małego poboru mocy. Dopuszczalne

są prądy upływu bramek. Obie optymalizacje

wymagają cienkiego tlenku bramki (thin-oxide).

Rok

Duża szybkość działania wymaga krótkiego

kanału, co wymaga stosowania niskich napięć

zasilania VDD . Napięcia progowe tranzystorów

VTn i VTp muszą być mniejsze niż VDD/2.

Bloki wejścia/wyjścia wymagają wyższych napięć

przebicia, czyli dłuższych kanałów i grubszego

tlenku bramki (thick-oxide), co wymaga

stosowania wyższych napięć zasilania VDD .

Pamięci wymagają małych prądów upływu bramki,

czyli grubszego tlenku bramki (thick-oxide), co

wymaga stosowania wyższych napięć zasilania

VDD . Wiążą sią z tym wyższe napięcia progowe

tranzystorów VTn i VTp.

S.Chatterjee et al., Circuit Design Techniques at 0.5V, Springer 2007

29

TEM Images of High Performance MOSFETs

59

All TEM images here have the same scale

90 nm node

65 nm node

45 nm node

32 nm node

100 nm

• Very little change in physical gate length, only ~0.9x per node

• The gate pitch is scaling fast, as 0.7x per node and area scales as 0.5x

• Most of the transistor innovation is in stress engineering and HKMG

source: V. Moroz, SYNOPSYS

Berkeley Seminar 2011

Skalowanie tranzystorów w układach CMOS

60

Zbliżanie się do granic możliwości materiałowych

krzemu i dwutlenku krzemu wymusza odstępstwa

od „klasycznych” reguł skalowania.

30

Difficult to Solve Problem – Gate Current Due to Electron

Tunneling in Thin Oxide

61

Modern MOS FETs can not be scalled with the classical rules

because of the quantum-mechanical tunneling of electrons in a

gate dielectric.

At very thin gate dielectric layers, about 1 nm, this effect results

in a gate-source and gate-drain current flow.

To avoid excessively large gate leak currents of this type:

• SiO2 gate dielectrics should not be made thinner than

1.5 nm;

• or, better, instead of SiO2 , other dielectric of large

permittivity (large dielectric constant), like HfO2

should be applied.

Tunelowy Prąd Bramki W Tranzystorze MOS

62

Grubość SiO2 to tylko 5 atomów. Obraz SiO2

bramki z transmisyjnego mikroskopu

elektronowego (TEM) o atomowej rozdzielczości.

Tunelowy prąd bramki w tranzystorze

MOS z cienkim SiO2. W technologii 65

nm stosowano SiO2 bramki o grubości 2

nm.

Zmniejszenie grubości SiO2 było z jednej

strony konieczne aby zmniejszyć długość

kanału do 32 nm ( w technologii 45 nm), a

z drugiej strony niemożliwe z uwagi na

niedopuszczalnie duży prąd upływu

bramki.

Gate_Tunneling_1a

Gęstość prądu bramki w funkcji naięcia bramka źródło

H.Momose i in, IEEE Trans. Electron Devices v50 s.1001 2003

31

Gate_Tunneling_1b

Tunelowy Prąd Bramki W Tranzystorze MOS

63

Znormalizowany prąd

upływu bramki

Problem dużego prądu bramki rozwiązano

stosując HfO2 jako izolator bramki.

• HfO2 ma większą przenikalność

dielektryczną niż SiO2

• więc może być grubszy przy tych

samych VGS i ID

• większa grubość dielektryka bramki

prowadzi do mniejszego prądu

tunelowego.

SiO2

IEDM 2007, art. s10p02, Intel

Tunelowy Prąd Bramki W Tranzystorze MOS

64

SiO2

Skalowanie grubości równoważnej

grubości tlenku bramki tranzystora

MOS w Intelu

IEDM 2007, art. s10p02, Intel

Gate_Tunneling_2

32

Gęstość Prądu Bramki JG [A/cm2]

Tunelowy Prąd Bramki W Tranzystorze MOS

65

maksymalna

dopuszczalna gęstość

prądu bramki

Równoważna Grubość SiO2 tox,eq [nm]

Yeo, King, Hu, IEEE Trans. Electron Devices, v.50, s.1027-1035, 2003

Trudne do rozwiązania problemy dla Lg < 16 nm

66

Opracowanie zawansowanych nowatorskich krzemowych struktur CMOS:

• Nieplanarne MOSFETy z wieloma bramkami krótszymi od 10 nm.

• Opanowanie zjawisk krótkiego kanału.

• Inżynieria drenu dla zmniejszenia rezystancji szeregowych.

• Prędkość termiczna elektronów zwiększona przez naprężenia, niemal

balistyczny transport.

Przyrządy inne niż krzemowy MOSFET?

• Opracować przyrządy i architektury układów scalonych.

• Zintegrować je na sposób Si-CMOS.

International Technology Roadmap for Semiconductors, ITRS 2009 Edition

33

Difficult to Solve Problem – Subthreshold Conduction and Drain

Induced Barrier Lowering

67

Modern MOS FETs can not be scalled with the classical rules

because of:

• subthreshold conduction

• and drain induced barrier lowering (DIBL).

These effects can be partially avoided in MOS FETs:

• of FinFET, or TriGate type,

• of gate surround, or quantum-wire type,

• or fabricated in extremely thin layers of semiconductor

on insulator.

Wpływ napięcia dren-żródło na wysokość bariery potencjału ΨB

DIBL - 0

68

N.Collaert, CMOS Nanoelectronics: Innovative Devices,

Architectures, and Applications, Pan Stanford Publ. 2012

34

Przewodnictwo podprogowe dren-źródło – przy VGS < VTn

69

Przewodnictwo podprogowe - 1

średnia

inwersja

silna inwersja

słaba

inwersja

Nachylenie

podprogowe

w inwerterze CMOS

VTn

• W tranzystorze MOS ID nie jest całkowicie odcięty (płynie) nawet przy VGS<VTn.

• Podprogowa wielkość ID jest ograniczana przez wysokość bariery potencjału YB pomiędzy

żródłem a kanałem, a nie przez transport w kanale jak w dla VGS<VTn.

• Podprogowa wielkość ID zależy wykładniczo od VGS.

• Przewodnictwo podprogowe problemem dla MOSów z krótkimi kanałami. Krótki kanał –

małe nachylenie

R.J.Baker, CMOS Circuit Design, Layout, and Simulation, Wiley 2008

Przewodnictwo podprogowe dren-źródło w 30 nm CMOS – TSMC 2007 70

pMOS nMOS

pMOS

Charakterystyki przewodzenia

podprogowego w tranzystorach MOS z

kanałami typu n i p przy VDS = 1,0 V

Przewodnictwo podprogowe - 30nm CMOS – TSMC 2007 - 2

nMOS

Zależności pomiędzy prądami

Ion-Ioff w technologii 45 nm

CMOS przy VDS = 1,0 V

IEDM 2007, art. s10p01, TSMC

35

Obniżanie bariery potencjału ΨB indukowane przez dren

(DIBL – drain induced barrier lowering)

źródło Ψ

B

VDS=0V

dren

źródło Ψ

B

71

dren

VDS

=0V

MOSFET

z długim kanałem

VDS>0V

MOSFET

z krótkim kanałem

VDS>0V

• Wysokość bariery potencjału ΨB pomiędzy żródłem a kanałem może być zmniejszona

przez elektrostatyczne oddziaływanie obszaru drenu.

• W starych tranzystorach z długimi kanałami problem nieistotny wskutek ekranującego

oddziaływania bramki.

• Wysokość bariery potencjału ΨB zmniejsza się ze wzrostem VDS.

• W tranzystorach z krótkimi kanałami, np. 50 nm, ΨB zmniejszone nawet przy VDS=0V.

• Mniejsza wysokość bariery potencjału ΨB prowadzi do zwiększenia ID.

DIBL - 1

DIBL - 2

S.M.Sze, Kwok K.Ng, Physics of Semiconductor Devices, 3ed. Wiley 2006

Obniżanie bariery potencjału ΨB indukowane przez dren

(DIBL – drain induced barrier lowering)

72

• Wysokość bariery potencjału ΨB zmniejsza się ze wzrostem VDS.

• W tranzystorach z krótkimi kanałami, np. 50 nm, ΨB zmniejszone nawet przy VDS=0V.

• Mniejsza wysokość bariery potencjału ΨB prowadzi do zwiększenia ID.

• Skutki DIBL można ograniczyć zwiękaszając domieszkowanie podłoża.

W. Fichtner, IEEE Solid St. Circ. and Tech. Workshop on Scaling and Microlithography, New York 1980.

36

Obniżanie bariery potencjału ΨB indukowane przez dren

(DIBL – drain induced barrier lowering)

73

Odpornosc CMOS na zaklocenia - 3

Vout1

Vout2

Odporność inwertera na zakłócenia

VNMH

Przyjmijmy standardowo, że

VoLmax = 0,1·VDD oraz

VoHmin = 0,9·VDD .

VNML

VNML – VNoise_Margin_Low - margines stanu

niskiego na zakłócenia

VNMH – VNoise_Margin_High - margines stanu

wysokiego na zakłócenia

VNML

VNMH

Vout2

Odporność inwertera na zakłócenia (marginesy na zakłócenia) oceniamy rysując statyczną

charakterystykę przenoszenia Vout1(Vin) , a następnie, w tym samym układzie współrzędnych Vout2(Vout1).

CMOS z 30 nm kanałem – TSMC 2007 - 2

Obniżanie bariery potencjału ΨB indukowane przez dren

(DIBL – drain induced barrier lowering)

74

CMOS z 30 nm kanałem – TSMC 2007

VDD=

pMOS

nMOS

Charakterystyki wyjściowe tranzystorów

MOS z kanałami typu n i p.

Statyczne marginesy zakłóceń w

inwerterze CMOS.

IEDM 2007, art. s10p01, TSMC

37

Difficult to Solve Problem – Difficulties in Development of

Fabrication Methods for Short Enough Gates

75

Modern MOS FETs can not be scalled with the classical rules

because

using classical lithography we can not fabricate gates

(channels) that scale down according to the technological

node scaling.

• We can use methods for gate/channel length definition that do

not rely on the lithography resolution.

• We use engineering of strain in semiconductor to increase the

transconductance and decrease the transit time of electric

charge carriers.

Skalowanie efektywnej długości kanału (od złącza do złącza)

Rozmiar charakterystyczny 90 nm.

(90 nm node)

76

Rozmiar charakterystyczny 32 nm.

(32 nm node)

• Lgate shrinks very slow

• S/D overlap shrinks fast

• Leff stays almost fixed

source: V. Moroz, SYNOPSYS

Berkeley Seminar 2011

38

W nanotranzystorach długość drogi przelotu elektronów (długość

kanału) może być znacznie większa od długości bramki

77

długość kanału – ponad 30 nm,

elektrony muszą pokonać tę

długość przy przełączaniu

długość bramki 16 nm

OFF

Długość kanału krótsza, gdy

wysokie koncentracje domieszek

w źródle i drenie.

ON

R. Gusmeroli i in., IEDM 2003, pp. 225 - 228

78

Naturalne bariery miniaturyzacji tranzystorów

• Niedługo zbliżymy się do barier związanych z

możliwymi do osiągnięcia wartościami koncentracji

atomów donorów i akceptorów,

•

• a także z przypadkowością ich rozkładów w sieci

krystalicznej.

• W dalszej przyszłości przyjdzie się zmierzyć z

ograniczeniami miniaturyzacji związanymi z

odległościami atomów tworzących kryształ

półprzewodnika.

• Istnieją też fundamentalne ograniczenia nakładane

przez prawa fizyki, jakie znamy.

39

Naturalne bariery miniaturyzacji tranzystorów

źródło

S

dren 100 nm MOSFET

D - struktura może być

uznana za ciągłą

bramka

G

bramka

G

źródło

S

dren

D

79

0,25 nm – odległość między

atomami w sieci krystalicznej Si

bramka

G

źródło

S

dren

D

donor

donor

25 nm MOSFET

-pomiędzy źródłem a drenem

mieści się ok. 100 atomów w

sieci krystalicznej Si

Kolorami niebieskim i czerwonym wyróżniono atomy akceptorów i

donorów, szarym - krzemu

A. Asenov i in. IEEE Trans. Electron Dev. v.50, s.1837, 2003

atom Si

akceptor

4 nm MOSFET

-pomiędzy źródłem a

drenem mieści się ok. 16

atomów w sieci

krystalicznej Si

bariery_miniaturyzacji_2

Naturalne bariery miniaturyzacji tranzystorów

0,25 nm – odległość między

atomami w sieci krystalicznej Si

bramka

G

dren

D

źródło

S

80

• Typowa koncentracja akceptorów 1e19 cm-3

• 1 atom przypadkowo ułożonej domieszki

akceptorowej lub donorowej na ok. 5000

atomów krzemu,

donor

• odległość pomiędzy atomami domieszek

średnio 4,6 nm,

• w przybliżeniu równa metalurgicznej odległości

źródło-dren.

donor

atom Si

akceptor

4 nm MOSFET

-pomiędzy źródłem a

drenem mieści się ok.

16 atomów w sieci

krystalicznej Si

• Różne wysokości bariery potencjału w różnych

częściach tranzystora,

• niemożliwe do kontrolowania i niepowtarzalne

wielkości napięć progowych tranzystorów,

• niemożliwe do kontrolowania i niepowtarzalne

prądy upływu tranzystorów.

40

Possible "fundamental physical limits" for digital information processing 81

τ

Emin

Minimum switching energy Emin

Thermodynamics

(Shannon-von Neumann-Landauer)

Emin > k BT ⋅ ln(2)

Δx ⋅ Δp ≥

xmin

Min. size of device

Integration

density

Min. switching time

Information

throughput

xmin

Heisenberg uncertainty

relationships

ΔE ⋅ Δt ≥

T =300 K

τ

Emin ≈ 3·10-21 J ≈ 17 meV, τ ≈ 3·10-14 s

M. Brillouet in S.Luryi et al. (ed.), "Future Trends in Microelectronics...", Wiley 2007, pp. 179-191

82

Tranzystory w układach scalonych

- wdrożone rozwiązania i wyniki

- stan w 2010r.

41

Napr_Si_konstrukcja_nMOS

Tranzystory MOS Z Naprężonym Krzemem

Dla Zwiększenia Ruchliwości Dziur i Elektronów

83

Tranzystor nMOS z bramką o metalurgicznej długości 35 nm (INTEL – w technologii 45 nm)

bramka

• Si3N4 osadzony w

odpowiednich warunkach na

krzemie rozciąga krzem

• Naprężenia rozciągające krzem

typu n powodują zwiększenie

ruchliwości elektronów µn w

kanale tranzystora – o 40%.

rozciąganie

źródło

• Zwiększenie µn powoduje

zmniejszenie czasu przelotu

elektronów przez kanał

dren tranzystora.

• Wzrasta częstotliwość

graniczna wzmocnienia mocy

fmax.

Si

Tyagi et al. IEDM 2005 s.1070

Obraz z elektronowego mikroskopu transmisyjnego (TEM)

Napr_Si_konstrukcja_pMOS

Tranzystory MOS Z Naprężonym Krzemem

Dla Zwiększenia Ruchliwości Dziur i Elektronów

84

Tranzystor pMOS z bramką o metalurgicznej długości 35 nm (INTEL – w technologii 45 nm)

źródło

bramka

SiO2/Si3N4

ściskanie

Si

• Atom germanu ma większą

średnicę od atomu krzemu.

• Tak osadzony SiGe w sieci

krystalicznej Si ściska więc

krzem.

dren • Naprężenia ściskające krzem

typu p powodują zwiększenie

ruchliwości dziur µp w kanale

tranzystora – o 100%.

• Zwiększenie µp powoduje

zmniejszenie czasu przelotu

dziur przez kanał tranzystora.

• Wzrasta częstotliwość

graniczna wzmocnienia mocy

fmax.

Obraz z elektronowego mikroskopu transmisyjnego (TEM)

Tyagi et al. IEDM 2005 s. 1070

42

Wpływ naprężeń krzemu, metalowej bramki i dielektryka bramki o dużej

85

stałej dielektrycznej na szybkość pMOSFETa

Klasyczne reguły skalowania zawodzą.

Poprawa szybkości działania wynika ze

zwiększenia prądu drenu na jednostkę

szerokości kanału, co bierze się w

podobnej mierze z:

• celowo wprowadzanych do krzemu

naprężeń oraz

• zastosowania metalowej bramki i

dielektryka bramki o dużej stałej

dielektrycznej.

source: K. Kuhn et. al, ECS 2010

- Intel

Tranzystory MOS Intela - 2010r.

Tranzystor MOS z kanałem typu p.

metalowa

bramka SiO /Si N

2

3 4

źródło

dren

86

• 32 nm – metalurgiczna długość bramki w

tranzystorach nMOS i pMOS (w technologii

45 nm).

• HfO2 / SiO2 użyty jako izolator bramki o dużej

stałej dielektrycznej.

• Dzięki temu tunelowy prąd bramki nie jest

zbyt duży.

SiGe

Si

SiGe

izolator bramki

o dużej stałej

dielektrycznej HfO2.

• Celowe naprężanie krzemu dla zwiększenia

µp o 100% oraz µn o 40%.

• Uzyskana poprawa ruchliwości dziur i

elektronów pozwala na zwiększenie

częstotliwości pracy tranzystorów.

• 9 warstw metalizacji dla zmniejszenia

rezystancji i pojemności połączeń oraz

dobrego wykorzystania powierzchni krzemu.

IEDM 2007, art. s10p02, Intel

43

2nd Generation 32-nm High-k + Metal Gate Transistors - Intel 2010

Metalowe

doprowadzenie

źródła/drenu

87

Tranzystor MOS z kanałem typu n.

Tranzystor MOS z kanałem typu p.

metalowa

bramka

metalowa

bramka

-kanał

-kanał

Epitaksjalne

pogrubienie krzemu w

źródle i drenie

zmniejsza rezystancję

szeregową.

krzem

krzem

Dielektryk bramki – SiO2/HfO2

o grubości ok. 2 nm

P. Packan i in., IEDM 2009 ss.659-662

Dla pMOS:

źródło i dren z SiGe

selektywnie wyhodowanego

w wytrawionch

wgłębieniach. SiGe ściska

krzem kanału, co zwiększa

ruchliwość dziur.

2nd Generation 32-nm High-k + Metal Gate Transistors - Intel 2010

Tranzystor MOS z kanałem typu n.

88

Tranzystor MOS z kanałem typu p.

-ID(VDS)

[mA/µm]

ID(VDS)

[mA/µm]

VGS =1.0V

Charakterystyki ID(VDS) przy ustalonych

wartościach VGS

0.8V

Uwaga:

• Prąd drenu |ID | nie wzrasta z kwadratem

|VGS|.

0.6V

• Napięcie VDS ma znaczący wpływ na ID

czyli rDS ≠ ∞.

• To są skutki bardzo krótkiego kanału, 32

nm.

ID(VDS)

[mA/µm]

-ID(VDS)

[mA/µm]

Charakterystyki przejściowe ID(VGS) przy

ustalonych wartościach VDS

P. Packan i in., IEDM 2009 ss.659-662

44

Wielowarstwowa Metalizacja

89

Dielektryk między warstwami metalizacji,

o możliwie małej stałej dielektrycznej,

mniejszej od SiO2.

powierzchnia krzemu

z tranzystorami niewidocznymi

metal (Cu)

-ścieżka

-przewodząca

IEDM 2007, art. s10p02, Intel

Warstwy miedzi po strawieniu dielektryka.

Obraz ze skaningowego mikroskopu

elektronowego (SEM)

IBM Corp.

90

Powierzchnia Komórki SRAM

Odległość pomiędzy bramkami

Bramki i Komórki Pamięci Statycznej CMOS

Z tranzystorami o długości kanałów 32 nm; Intel - 2009r.

Węzeł technologiczny

Trend w skalowaniu bramek i komórek

SRAM z 6 tranzystorami.

Warstwy dyfuzyjne i polikrystaliczne

sześciotranzystorowej komórki SRAM o

powierzchni 0,346 µm2.

IEDM 2007, art. s10p02, Intel

45

CMOS z 30 nm kanałem – TSMC 2007 - 3

CMOS z 30 nm kanałem – TSMC 2007

91

Tranzystory CMOS z 30 nm kanałem wykonane w technice 45 nm. Do litografii

użyto światła o l = 193 nm w próżni, przy NA=1,2. Długość fali światła skrócono,

63%, wykonując naświetlanie w cieczy.

Widok z góry 6-tranzystorowej komórki pamięci statycznej, zajmującej

powierzchnię 0,242 µm2

IEDM 2007, art. s10p01, TSMC

Rekordowo duże wartości częstotliwości granicznych fT w

tranzystorach CMOS wykonanych w technologii 45 nm - IBM 2007

92

pMOS

nMOS

Rekord fT w tranzystorach CMOS IBM 2007 - a

IEDM 2007, art. s10p04, IBM

46

Oscylator Pierścieniowy

93

• Nieparzysta ilość inwerterów

tworzy oscylator pierścieniowy

(ring oscillator).

• Z generowanej częstotliwości f

określa się czas przełączania

bramki, czyli czas opóźnienia

pojedynczego stopnia (delay

time)

td = 1/(2×n×f)

• Czas przełączania bramek z

większą ilością wejść jest trochę

dłuższy.

Vk/VDD - znormalizowane napięcia wyjściowe

bramek w funkcji znormalizowanego czasu

Szybkość Przełączania Inwerterów CMOS

94

Opóźnienie stopnia [pS]

Inwertery CMOS z tranzystorami o

długości kanałów 32 nm (wykonane

w technologii 45 nm, Intel – 2010 r.)

mają czas opóźnienia td = 5,1 pS.

=VDD

=VDD

Prąd w stanie odcięcia tranzystorów [nA/µm]

IEDM 2007, art. s10p02, Intel

47

Porównanie częstotliwości granicznych wzmocnienia prądowego

fT przyrządów wykonanych w technologiach CMOS i SiGe przy

różnych rozmiarach charakterystycznych procesów wytwarzania

95

R. Kumar, Fabless Semiconductor Implementation, McGraw-Hill, 2008

Historical Trend of Si MOSFET Performance Scaling

96

Historical trend of the intrinsic transistor delay for some benchmark technologies.

Filled symbols represent strain-engineered devices. Saturation of performance

scaling is seen in the recent technology nodes, if strain engineering is not used.

A. Khakifirooz, D. A. Antoniadis, "CMOS Performance Scaling", in R.Murali (ed.), "Graphene

Nanoelectronics: From Materials to Circuits", p. 10, Springer 2012

48

Historical Trend of Si MOSFET Performance Scaling

97

Extracted virtual source velocity of electrons and holes for different

technological nodes. Filled symbols represent strain-engineered devices.

Saturation of virtual source velocity is seen for unstrained devices below a gate

length of about 100 nm.

A. Khakifirooz, D. A. Antoniadis, "CMOS Performance Scaling", in R.Murali (ed.), "Graphene

Nanoelectronics: From Materials to Circuits", p. 11, Springer 2012

Expected Electron & Hole Velocities for non-Si MOSFETs

Electrons - Comparison of virtual source

velocity in deeply scaled III–V HEMTs

and historical Si data.

98

Hole virtual source velocity extracted from shortchannel Ge PFETs from literature (symbols)

compared with historical data for relaxed and

uniaxially strained Si. Experimental data for both

relaxed and biaxially strained Ge are included,

demonstrating that without uniaxial strain, Ge

does not offer any benefit over relaxed Si.

A. Khakifirooz and D. A. Antoniadis, “MOSFET Performance scaling – Part II: Future directions,” IEEE

Trans. Electron Devices, vol. 55, no. 6, pp. 1401–1408, 2008.

49

HF transistors fmax-fT

Rekordowe częstotliwości fT i fmax tranzystorów oraz częstotliwości pracy układów fcircuit 99

(2015 r)

fmax – graniczna częstotliwość przy której tranzystor może wzmacniać

moc, to jest przy której, dla składowej zmiennej Pout / Pin > 1

fT – graniczna częstotliwość przy której tranzystor może wzmacniać prąd,

to jest przy której, dla składowej zmiennej Id / Ig > 1

100

FinFET – solution to DIBL – drain induced barrier

lowering and subthreshold conduction

Node

Year

90 nm

(2003)

65 nm

(2005)

45 nm

(2007)

32 nm

(2009)

22 nm

(2011)

source: M. Bohr, K. Mistry,

Intel’s Revolutionary 22 nm Transistor Technology, May, 2011

50

Traditional planar MOS FET vs. tri-gate MOS FET (FinFET)

Planar MOS FET

101

Tri-gate MOS FET (FinFET)

electrode

electrode

Gate

Gate high-k

dielectric

Traditional 2-D planar transistors

form a conducting channel in the

silicon region under the gate

electrode when in the “on” state.

3-D Tri-Gate transistors form

conducting channels on three sides

of a vertical fin structure, providing

“fully depleted” operation.

source: M. Bohr, K. Mistry,

Intel’s Revolutionary 22 nm Transistor Technology, May, 2011

Traditional planar MOS FET vs. tri-gate MOS FET (FinFET)

32 nm planar MOS FET

102

22 nm tri-gate MOS FET (FinFET)

source: M. Bohr, K. Mistry,

Intel’s Revolutionary 22 nm Transistor Technology, May, 2011

51

INTEL processor with fully depleted 22-nm tri-gate MOS

FET (FinFET)

103

TEM Image of nMOS Gate and Fin

Structure

source: Chris Auth, et. al., 2012 Symposium on VLSI Technology, Hawaii

2014 Aug. - 14-nm Intel Broadwell Processor with Trigate

CMOS Transistors (FinFETs)

104

D. Jame, Intel’s 14nm Parts are Finally Here!, Solid State Technology, 2014.10.27

52

14-nm Intel Trigate CMOS Transistors (FinFETs)

105

scale

S/D

contact

13 layers of metal + a MIM (MetalIsolator-Metal) cap. Previously Intel used

9 metal layers (IBM used 15 metal layers)

G

S/D

metal &

contact

contact

The gate metallisation looks similar to the 22

nm, with tungsten gate fill as in the earlier

process.

D. Jame, Solid State Technology, 2014.10.27

Przyrządy wysokiej częstotliwości

106

International Technology Roadmap for Semiconductors, ITRS 2009 Edition

53

650 GHz, 160 GHz SiGe circuits

Mieszacz na 650 GHz z diodami metal-półprzewodnik z SiGe

0,6 mm

107

1,2 mm

Układ scalony mieszacza wejściowego odbiornika na 650 GHz.

Zawiera tranzystory, diody metal-półprzewodnik z SiGe oraz linie transmisyjne, sprzęgacze i

dipol anteny sygnału wielkiej częstotliwości.

Heterozłączowe tranzystory bipolarne z SiGe o częstotliwościach granicznych fT= 260 GHz,

fmax= 380 GHz wzmacniają sygnał LO o częstotliwości fLO=162,5 GHz.

Częstotliwość f=650 GHz jest przetwarzana przez mieszacz z diodą metal-półprzewodnik.

Układ wykonano w technologii BiCMOS 130 nm na podłożu Si.

E. Öjefors et al., ISSCS 2010

SiGe BiCMOS 160 GHz circuits

Układy na 160 GHz z heterozłączowymi tranzystorami bipolarnymi z SiGe

108

Układ scalony odbiornika na 160 GHz.

Układ scalony nadajnika na 160 GHz – w technologii BiCMOS na podłożu Si.

Sygnały o częstotliwości 160 GHz są przetwarzane przez heterozłączowe

tranzystory bipolarne z SiGe o częstotliwościach granicznych fT= 260 GHz,

fmax= 380 GHz.

Tranzystory wykonane w technologii 130 nm.

U.R.Pfeiffer et al., ISSCS 2010

54

sub-mm HEMT amp 480GHz - 2

Wzmacniacze z tranzystorami HEMT dla zakresu fal submilimetrowych 109

W.R.Deal et al., IEEE MWCL, vol. 20,

pp. 289-291, 2010

0,32 mm

Metal z falowodami WR-2.2

- wejściowym i wyjściowym.

Płytka InP 0,9 mm × 0,32 mm ze

wzmacniaczem. Sygnały sprzężone z

falowodami przy pomocy dipoli.

S 21dB = 20 log S 21

0,9 mm

Niskoszumowy pięciostopniowy scalony

monolityczny wzmacniacz dla f = 480 GHz z

tranzystorami HEMT na podłożu z InP.

HEMT: dugość kanału < 50 nm,

transkonduktancja 2300 S/mm,

fmax = 1200 GHz, fT = 580 GHz.

G0 = S 21

= 10

S 21 db

10

2

G0 – hipotetyczna wartość wzmocnienia

mocy przy dopasowaniu impedancji na

wejściu i wyjściu oraz przy transmisji

sygnału tylko z wejścia do wyjścia

Parametry S wzmacniacza

Current-gain cutoff frequency fT vs. gate length for different field effect

transistor technologies (InP, GaAs, Si)

110

Breakdown voltage vs. current

gain cutoff frequency fT

G.Ghione,Semiconductor Devices for HighSpeed Optoelectronics, Cambridge 2009

W. Snodgrass et al., 2006 IEDM, pp.1-4

55

Obecnie produkowane procesory z krzemowymi tranzystorami CMOS

source: Intel, 2014

Intel 22–nm.

2014:

Intel – procesor Broadwell z

tranzystorami CMOS tri-gate

(FinFET) wykonanymi w

technologii o rozmiarze

charakterystycznym 14 nm.

111

Tranzystory z 14 płetwami w

technologii o rozmiarze

charakterystycznym 16 nm w

procesorze Apple A9 –

TSMC, 2016 r.

Zaprojektujcie układy lepsze dla Waszych

potrzeb, szybsze i zużywające mniej energii!

112

Dziękuję za uwagę!

56