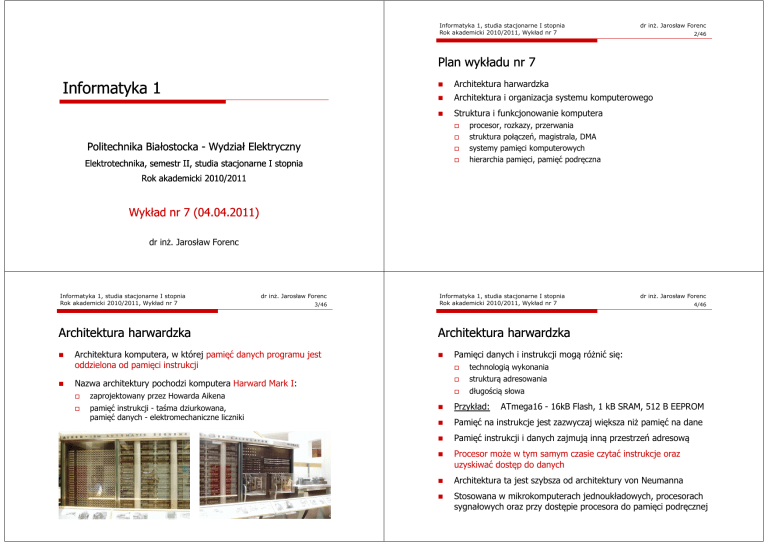

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

2/46

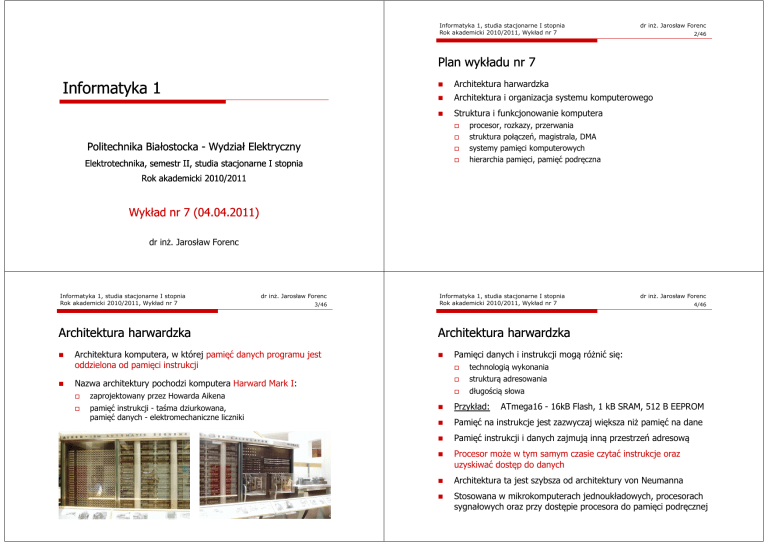

Plan wykładu nr 7

Informatyka 1

Architektura harwardzka

Architektura i organizacja systemu komputerowego

Struktura i funkcjonowanie komputera

Politechnika Białostocka - Wydział Elektryczny

Elektrotechnika, semestr II, studia stacjonarne I stopnia

procesor, rozkazy, przerwania

struktura połączeń, magistrala, DMA

systemy pamięci komputerowych

hierarchia pamięci, pamięć podręczna

Rok akademicki 2010/2011

Wykład nr 7 (04.04.2011)

dr inż. Jarosław Forenc

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

3/46

Architektura harwardzka

Architektura komputera, w której pamięć danych programu jest

oddzielona od pamięci instrukcji

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

zaprojektowany przez Howarda Aikena

pamięć instrukcji - taśma dziurkowana,

pamięć danych - elektromechaniczne liczniki

4/46

Architektura harwardzka

Nazwa architektury pochodzi komputera Harward Mark I:

dr inż. Jarosław Forenc

Pamięci danych i instrukcji mogą różnić się:

technologią wykonania

strukturą adresowania

długością słowa

Przykład:

ATmega16 - 16kB Flash, 1 kB SRAM, 512 B EEPROM

Pamięć na instrukcje jest zazwyczaj większa niż pamięć na dane

Pamięć instrukcji i danych zajmują inną przestrzeń adresową

Procesor może w tym samym czasie czytać instrukcje oraz

uzyskiwać dostęp do danych

Architektura ta jest szybsza od architektury von Neumanna

Stosowana w mikrokomputerach jednoukładowych, procesorach

sygnałowych oraz przy dostępie procesora do pamięci podręcznej

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

5/46

Architektura harwardzka i von Neumanna

zajmują różne przestrzenie adresowe

mają oddzielne szyny (magistrale) do procesora

zaimplementowane są w inny sposób

Pamięć programu

(instrukcje programu)

Architektura von Neumanna

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Magistrala danych

Zmodyfikowana architektura harwardzka łączy w sobie cechy

architektury harwardzkiej i architektury von Neumanna

W architekturze tej oddzielone są pamięci danych i rozkazów,

lecz wykorzystują one wspólną magistralę danych i adresową

Architektura ta pozwala na dostęp do pamięci instrukcji tak jakby

były to dane

Część pamięci instrukcji może zawierać stałe dane, np. łańcuchy

znaków, które mogą być przesyłane bezpośrednio do procesora

z pominięciem pamięci na dane - zapewnia to oszczędność

pamięci na dane

Pamięć danych

(dane programu)

Architektura harwardzka

dr inż. Jarosław Forenc

7/46

Architektura von Neumanna i harwardzka

6/46

Procesor

Magistrala instrukcji

dr inż. Jarosław Forenc

Zmodyfikowana architektura harwardzka

W architekturze harwardzkiej pamięć instrukcji i pamięć danych:

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

W obecnie stosowanych procesorach występują elementy obu

architektur:

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

8/46

Architektura i organizacja systemu komputerowego

Przedstawienie struktury i zasady działania komputerów jest

zagadnieniem dość skomplikowanym, gdyż:

pamięć operacyjna (RAM) komputera jest to typowa architektura

von Neumanna

istnieje ogromna różnorodność sprzętu komputerowego

(od komputerów masywnie równoległych do komputerów PC)

pamięć podręczna (cache) podzielona jest na pamięć instrukcji

i pamięć danych

technika komputerowa rozwija się bardzo szybko, ciągle pojawiają

się nowe technologie, interfejsy, standardy

komputer jest systemem złożonym z bardzo dużej liczby elementów

Z punktu widzenia programisty posługujemy się architekturą

von Neumana, zaś implementacje sprzętowe zawierają

architekturę harwardzką

Stosowane obecnie mikrokontrolery są oparte na zmodyfikowanej

architekturze harwardzkiej (AVR, ZiLOG Z8Encore!)

Z powyższych powodów zazwyczaj przedstawia się hierarchiczną

strukturę systemu komputerowego

system hierarchiczny jest to układ wzajemnie powiązanych

podsystemów, z których każdy ma również strukturę hierarchiczną

na każdym poziomie określana jest struktura składników systemu

(sposób ich wzajemnego powiązania) oraz funkcje składników

systemu (działanie poszczególnych składników jako części struktury)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

9/46

Architektura komputera a organizacja komputera

Architektura komputera

odnosi się do atrybutów systemu, które są widzialne dla programisty

i mają bezpośredni wpływ na logiczne wykonywanie programu

do atrybutów architektury należą m.in. lista rozkazów, liczba bitów

wykorzystywanych do prezentacji różnych typów danych,

mechanizmy wejścia/wyjścia, metody adresowania pamięci

odnosi się do jednostek operacyjnych i ich połączeń, które stanowią

realizację specyfikacji typu architektury

atrybuty organizacyjne są to rozwiązania sprzętowe niewidzialne dla

programisty, np. sygnały sterujące, interfejsy między komputerem

a urządzeniami peryferyjnymi, wykorzystywana technologia pamięci

dr inż. Jarosław Forenc

11/46

Struktura komputera

Komputer składa się z czterech głównych składników:

procesor (jednostka centralna, CPU)

- steruje działaniem komputera

i realizuje funkcje przetwarzania danych

pamięć główna - przechowuje dane

wejście-wyjście - przenosi dane

między komputerem a jego

otoczeniem zewnętrznym

połączenia systemu - wszystkie

mechanizmy zapewniające komunikację

między jednostką centralną, pamięcią

główną a wejściem-wyjściem

Wszystkie powyższe składniki mogą występować w komputerze

pojedynczo lub w większej liczbie

10/46

Funkcje realizowane przez komputer:

przetwarzanie danych

przechowywanie danych

(krótkotrwałe lub długotrwałe)

przenoszenie danych

(pomiędzy komputerem

a światem zewnętrznym)

Organizacja komputera

dr inż. Jarosław Forenc

Funkcjonowanie komputera

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

urządzenia peryferyjne

(proces wejścia-wyjścia)

duża odległość

(transmisja danych)

sterowanie

(powyższymi funkcjami)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Struktura procesora

Główne składniki strukturalne procesora to:

jednostka sterująca - steruje działaniem

procesora i pośrednio całego komputera

jednostka arytmetyczno-logiczna (ALU)

- realizuje funkcję przetwarzania danych

przez komputer

rejestry - realizują wewnętrzne

przechowywanie danych w procesorze

połączenia procesora - wszystkie

mechanizmy zapewniające komunikację

między jednostką sterującą, ALU

i rejestrami

dr inż. Jarosław Forenc

12/46

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

13/46

Działanie komputera

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

14/46

Działanie komputera

Podstawowe zadanie komputera to wykonywanie programu

Podstawowe zadanie komputera to wykonywanie programu

Program składa się z rozkazów przechowywanych w pamięci

Program składa się z rozkazów przechowywanych w pamięci

Rozkazy są przetwarzane w dwu krokach:

Rozkazy są przetwarzane w dwu krokach:

Cykl pobierania (ang. fetch):

odczytanie rozkazu z pamięci

do śledzenia, który rozkaz ma

być pobrany służy rejestr zwany

licznikiem rozkazów (PC) lub

wskaźnikiem instrukcji (IP)

jeśli procesor nie otrzyma innego

polecenia, to powoduje

inkrementację licznika PC

po każdym pobraniu rozkazu

i wykonuje następny rozkaz

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

15/46

Działanie komputera

CW1

CP1

CW1

CP2

CP2

CW2

CW2

CP3

CW3

może zawierać kilka operacji,

jest zależny od natury rozkazu

pobrany rozkaz jest ładowany

do rejestru w procesorze

zwanego rejestrem rozkazu (IR)

rozkaz ma formę kodu binarnego

określającego działania, które ma

podjąć procesor

procesor interpretuje rozkaz

i przeprowadza wymagane działania

dr inż. Jarosław Forenc

16/46

Działanie komputera

W celu przyspieszenia pracy systemu stosuje się tzw. wstępne

pobranie instrukcji (ang. prefetching)

CP1

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Cykl wykonywania (ang. execution):

CP3

CW3

Graf stanów cyklu wykonania rozkazu ma następującą postać:

CP - cykl pobierania

CW - cykl wykonywania

prefeching

czas

Działania procesora można podzielić na cztery grupy:

przesłanie danych z procesora do pamięci lub odwrotnie

przesłanie danych z procesora do modułu we-wy lub odwrotnie

operacje arytmetyczne lub logiczne na danych

sterowanie (np. zmiana sekwencji wykonywania programu)

Wykonywanie rozkazów może zawierać kombinacje powyższych

działań

(3) - analiza rozkazu w celu określenia rodzaju operacji, która ma być

wykonana oraz w celu określenia argumentu (jednego lub kilku)

(8) - zapisanie wyniku w pamięci lub skierowanie go do we/wy

Nie wszystkie stany z powyższego schematu muszą występować

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

17/46

Działanie komputera

dr inż. Jarosław Forenc

18/46

Działanie komputera

Graf stanów cyklu wykonania rozkazu ma następującą postać:

Każdy rozkaz przechowywany jest w postaci binarnej, ma

określony format i używa określonego trybu adresowania

Format to sposób rozmieszczenia informacji w kodzie rozkazu

Rozkaz zawiera kod operacji (rodzaj wykonywanej operacji)

i argumenty (lub adresy argumentów) wykonywanych operacji

Tryb adresowania jest to sposób określania miejsca

przechowywania argumentów rozkazu (operandów):

Mogą wystąpić sytuacje, w których jeden rozkaz może określać

operacje na wektorze liczb lub na szeregu znaków, co wymaga

powtarzania operacji pobrania i/lub przechowywania

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

19/46

Działanie komputera - przerwania

Wykonywanie kolejnych rozkazów przez procesor może być

przerwane poprzez wystąpienie tzw. przerwania

Można wyróżnić kilka klas przerwań:

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

programowe - generowane po wystąpieniu błędu podczas

wykonania rozkazu (np. dzielenie przez zero)

zegarowe - generowane przez wewnętrzny zegar procesora

we-wy - generowane przez sterownik we-wy w celu

zasygnalizowania normalnego zakończenia operacji lub błędu

uszkodzenie sprzętu - generowane przez uszkodzenie,

np. defekt zasilania, błąd parzystości pamięci

Przerwania zostały zaimplementowane w celu poprawienia

efektywności przetwarzania - procesor może wykonywać inne

rozkazy, gdy jest realizowana operacja we-wy

natychmiastowe - argument znajduje się w kodzie rozkazu

bezpośrednie - adres argumentu znajduje się w kodzie rozkazu

rejestrowe - argument znajduje się w rejestrze

pośrednie - adres argumentu znajduje się w rejestrze

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

20/46

Działanie komputera - przerwania

Aby dostosować się do przerwań do cyklu rozkazu jest dodawany

cykl przerwania:

Po sygnale przerwania procesor:

zawiesza wykonanie bieżącego

programu i zachowuje jego

kontekst

ustawia licznik programu na

początkowy adres programu

obsługi przerwania

wykonuje program obsługi

przerwania

wznawia wykonywanie

programu użytkowego

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

21/46

Działanie komputera - przerwania

dr inż. Jarosław Forenc

22/46

Działanie komputera - przerwania wielokrotne

Jak działa przerwanie?

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

23/46

Działanie komputera - struktura połączeń

Podczas obsługi jednego przerwania może pojawić się sygnał

kolejnego przerwania

Problem przerwań wielokrotnych rozwiązywany jest na dwa

sposoby:

uniemożliwienie innych przerwań,

jeśli jakiekolwiek inne przerwanie

jest przetwarzane

określenie priorytetów przerwań przerwanie o wyższym priorytecie

powoduje przerwanie programu

obsługi przerwania o niższym

priorytecie

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

24/46

Działanie komputera - struktura połączeń

Struktura połączeń jest to zbiór ścieżek łączących podstawowe

moduły komputera, tj. procesor, pamięć i urządzenia we-wy

Struktura połączeń jest to zbiór ścieżek łączących podstawowe

moduły komputera, tj. procesor, pamięć i urządzenia we-wy

Pamięć:

Procesor:

odczytuje rozkazy i dane

wysyła dane po przetworzeniu

słowa umieszczone są pod

konkretnymi adresami

steruje pracą całego systemu

poprzez sygnały sterujące

słowo może być odczytane

z pamięci lub do niej zapisane

otrzymuje sygnały przerwań

typ operacji określają sygnały

sterujące odczyt i zapis

pamięć składa się z określonej

liczby słów o jednakowej długości

Rozkazy

Sygnały ster.

Dane

Procesor

Dane

Sygnały przerw.

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

25/46

Działanie komputera - struktura połączeń

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Struktura połączeń jest to zbiór ścieżek łączących podstawowe

moduły komputera, tj. procesor, pamięć i urządzenia we-wy

Moduł wejścia-wyjścia:

Struktura połączeń musi umożliwiać przesyłanie następujących

danych:

DMA - bezpośredni dostęp do pamięci:

Odczyt

istnieją dwie operacje:

zapis i odczyt

każdy z interfejsów z urządzeniem

zewnętrznym określany jest

portem i ma jednoznaczny adres

Zapis

Adres

Dane zew.

w pewnych przypadkach pożądane jest

umożliwienie bezpośredniej wymiany

danych między we-wy a pamięcią

podczas takiego przesyłania moduł we-wy

odczytuje lub zapisuje rozkazy w pamięci,

uwalniając procesor od odpowiedzialności

za tę wymianę

powyższe operacje nazywane są

bezpośrednim dostępem do pamięci

(ang. DMA - Direct Memory Access)

Sygnał przerw.

Dane zew.

D

an

e

moduł może wysyłać sygnały

przerwań do procesora

an

e

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

27/46

Działanie komputera - magistrala

Najczęściej stosowana struktura połączeń to magistrala

Magistrala jest wspólnym nośnikiem transmisji, do którego

dołączonych jest wiele urządzeń, a sygnały wysyłane przez jedno

z nich mogą być odbierane przez pozostałe urządzenia

Magistrala składa się z wielu linii komunikacyjnych, którym

przypisane jest określone znaczenie i określona funkcja

Fizycznie magistrala jest zbiorem równoległych połączeń

elektrycznych

System komputerowy zawiera pewną liczbę różnych magistrali

najczęściej procesor bezpośrednio

odczytuje dane z pamięci i zapisuje

oraz komunikuje się z urządzeniami we-wy

D

Dane wew.

Moduł

we/wy

Dane wew.

26/46

Działanie komputera - struktura połączeń

dr inż. Jarosław Forenc

Magistrala łącząca główne zasoby komputera (procesor, pamięć,

wejście-wyjście) nazywana jest magistralą systemową

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

28/46

Działanie komputera - magistrala

Linie dzielą się na trzy grupy: linie danych, adresów i sterowania

Linie danych:

przenoszą dane między modułami systemu

wszystkie linie danych nazywane są szyną danych

liczba linii określa szerokość szyny danych (8, 16, 32, 64 bity)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

29/46

Działanie komputera - magistrala

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

30/46

Działanie komputera - magistrala

Linie dzielą się na trzy grupy: linie danych, adresów i sterowania

Linie dzielą się na trzy grupy: linie danych, adresów i sterowania

Linie adresowe:

Linie sterowania:

służą do określania źródła i miejsca przeznaczenia danych

przesyłanych magistralą

liczba linii adresowych (szerokość szyny adresowej) określa

maksymalną możliwą pojemność pamięci systemu

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

31/46

Działanie komputera - struktury wielomagistralowe

W przypadku większej liczby urządzeń podłączonych do

magistrali znacząco spada jej wydajność

Rozwiązaniem tego

problemu są struktury

wielomagistralowe

o określonej hierarchii

służą do sterowania dostępem do linii danych i linii adresowych

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

32/46

Działanie komputera - typy magistral

ISA (ang. Industry Standard Architecture)

1981 rok

8-bitowa (XT) i 16-bitowa (AT) szyna danych

24-bitowa szyna adresowa

teoretyczna przepustowość: 8 MB/s (praktycznie: 1,6-1,8 MB/s)

PCI (ang. Peripheral Component Interconnect)

Wersja

Rok

Szyna danych

Przepustowość

PCI 2.0

1993

32-bitowa

133 MB/s

PCI 2.1

1994

64-bitowa

528 MB/s

PCI 2.2

1999

64-bitowa

528 MB/s

PCI 2.3

2002

64-bitowa

528 MB/s

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

33/46

Działanie komputera - typy magistral

2004 rok

magistrala lokalna typu szeregowego, łącząca dwa punkty

występuje w kilku wariantach: x1 (250 MB/s), x2 (500 MB/s),

x4 (1000 MB/s), x8 (2000 MB/s), x16 (4000 MB/s), x32

(8000 MB/s)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

35/46

Systemy pamięci komputerowych

dr inż. Jarosław Forenc

34/46

Systemy pamięci komputerowych

PCI-Express (PCIe, PCI-E)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Ze względu na sposób dostępu do danych wyróżniamy:

Ze względu na położenie pamięci w stosunku do komputera

wyróżniamy pamięć:

procesora (rejestry)

wewnętrzną (pamięć główna)

zewnętrzną (pamięć pomocnicza - pamięci dyskowe i taśmowe)

Parametry charakteryzujące pamięć:

pojemność - maksymalna liczba informacji jaką można

przechowywać w danej pamięci

czas dostępu - czas niezbędny do zrealizowania operacji

odczytu lub zapisu

czas cyklu pamięci - czas dostępu plus dodatkowy czas, który musi

upłynąć zanim będzie mógł nastąpić kolejny dostęp

szybkość przesyłania (transferu) - maksymalna liczba danych jakie

można odczytać z pamięci lub zapisać do pamięci w jednostce czasu

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

36/46

Systemy pamięci komputerowych

Dostęp bezpośredni:

dostęp sekwencyjny (pamięci taśmowe)

odczyt i zapis realizowany jest za pomocą tego samego mechanizmu

dostęp bezpośredni (pamięci dyskowe)

dostęp swobodny (pamięć główna)

poszczególne bloki (rekordy) mają unikatowy adres oparty na

fizycznej lokacji

dostęp skojarzeniowy (pamięć podręczna)

dostęp jest realizowany przez bezpośredni dostęp do najbliższego

otoczenia, po którym następuje sekwencyjne poszukiwanie, liczenie

lub oczekiwanie w celu osiągnięcia lokacji finalnej

Dostęp sekwencyjny:

jednostka danych to rekord

dostęp do rekordów jest możliwy w określonej sekwencji liniowej

przejście z jednego rekordu do następnego następuje poprzez

przepuszczenie i odrzucenie rekordów pośrednich

czas dostępu do różnych rekordów może bardzo różnić się

Dostęp swobodny:

każda adresowalna lokacja w pamięci ma unikatowy fizycznie

wbudowany mechanizm adresowania

czas dostępu jest stały i niezależny od poprzednich operacji dostępu

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

37/46

Systemy pamięci komputerowych

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

38/46

Hierarchia pamięci

Dostęp skojarzeniowy:

każda lokacja ma własny mechanizm adresowania

Istnieją wzajemne zależności pomiędzy parametrami pamięci:

kosztem, pojemnością i czasem dostępu:

czas dostępu jest stały i niezależny od poprzednich operacji dostępu

słowa są wprowadzane na podstawie części swojej zawartości, a nie

na podstawie całego adresu

mniejszy czas dostępu - większy koszt na bit

większa pojemność - mniejszy koszt na bit

większa pojemność - dłuższy czas dostępu

W systemach komputerowych nie stosuje się jednego typu

pamięci, ale hierarchię pamięci

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

39/46

Półprzewodnikowa pamięć główna

RAM (Random Access Memory) - pamięć o dostępie swobodnym

Rozpatrując hierarchię od góry

do dołu obserwujemy zjawiska:

malejący koszt na bit

rosnącą pojemność

rosnący czas dostępu

malejącą częstotliwość dostępu

do pamięci przez procesor

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

Półprzewodnikowa pamięć główna

ROM (ang. Read-Only Memory) - pamięć stała

odczyt i zapis następuje za pomocą sygnałów elektrycznych

pamięć o dostępie swobodnym przeznaczona tylko do odczytu

pamięć ulotna - po odłączeniu zasilania dane są tracone

dane są zapisywane podczas procesu wytwarzania

DRAM:

pamięć nieulotna

przechowuje dane podobnie jak kondensator ładunek elektryczny

wymaga operacji odświeżania

PROM (ang. Programmable ROM) - programowalna pamięć ROM

jest mniejsza, gęściej upakowana i tańsza niż pamięć statyczna

pamięć nieulotna, może być zapisywana tylko jeden raz

stosowana jest do budowy głównej pamięci operacyjnej komputera

zapis jest realizowany elektrycznie po wyprodukowaniu

SRAM:

przechowuje dane za pomocą przerzutnikowych konfiguracji bramek

logicznych

nie wymaga operacji odświeżania

jest szybsza i droższa od pamięci dynamicznej

stosowana jest do budowy pamięci podręcznej

40/46

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

41/46

Półprzewodnikowa pamięć główna

EPROM - pamięć wielokrotnie programowalna, kasowanie następuje

przez naświetlanie promieniami UV

EEPROM - pamięć kasowana i programowana na drodze czysto

elektrycznej

Flash - rozwinięcie koncepcji pamięci EEPROM, możliwe kasowanie

i programowanie bez wymontowywania pamięci z urządzenia,

występuje w dwóch odmianach:

Zastosowanie pamięci podręcznej ma na celu przyspieszenie

dostępu procesora do pamięci głównej

W systemie komputerowym występuje względnie duża i wolniejsza

pamięć główna oraz mniejsza i szybsza pamięć podręczna

pamięć podręczna zawiera kopię części

zawartości pamięci głównej

przed odczytaniem słowa z pamięci

następuje sprawdzenie czy znajduje się

ono w pamięci podręcznej

jeśli tak, to jest przesyłane do procesora

jeśli nie, to blok pamięci głównej

(ustalona liczba słów) jest wczytywany

do pamięci podręcznej, a następnie słowo

jest przesyłane do procesora

NAND (pen drive, karty pamięci)

dr inż. Jarosław Forenc

43/46

Pamięć podręczna

42/46

NOR (Flash BIOS)

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

Pamięć podręczna

Inne typy pamięci:

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Do pamięci podręcznej jest przesyłany cały blok, gdyż ze względu

na tzw. zjawisko lokalności odniesień, istnieje duże

prawdopodobieństwo, że przyszłe odniesienia będą dotyczyły

innych słów w tym samym bloku

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

44/46

Pamięć podręczna

Porównanie różnych typów pamięci

Level

Access Time

Typical Size

Technology

Managed By

Registers

1-3 ns

~1 KB

Custom CMOS

Compiler

Level 1 Cache

(on-chip)

2-8 ns

8 KB-128 KB

SRAM

Hardware

Level 2 Cache

(off-chip)

5-12 ns

0.5 MB - 8 MB

SRAM

Hardware

Main Memory

10-60 ns

64 MB - 1 GB

DRAM

Operating

System

Hard Disk

3,000,000 10,000,000 ns

20 - 100 GB

Magnetic

Operating

System/User

źródło: http://arstechnica.com/old/content/2002/07/caching.ars/2

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

Pamięć zewnętrzna

dr inż. Jarosław Forenc

45/46

Informatyka 1, studia stacjonarne I stopnia

Rok akademicki 2010/2011, Wykład nr 7

dr inż. Jarosław Forenc

Koniec wykładu nr 7

Do pamięci zewnętrznych zaliczane są:

dyski twarde - HDD

pamięci optyczne - CD, DVD

magnetyczne pamięci taśmowe

Budowa dysku twardego:

nośnik danych

część mechaniczna

kontroler

Dziękuję za uwagę!

46/46