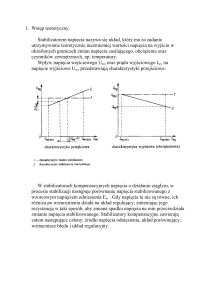

8. UKŁADY UZALEŻNIEŃ CZASOWYCH

8.1. CEL ĆWICZENIA

Zagadnienia związane z pomiarem czasu stanowią ważną klasę

zadań realizowanych przez układy cyfrowe. Do typowych zaliczamy:

zapewnienie odpowiedniego czasu trwania impulsu sterującego, realizację odstępu czasowego między dwoma impulsami, generację ciągu

impulsów, zapewnienie reakcji układu na impuls o określonym czasie

trwania itp. Układy realizujące powyższe zadania można podzielić na

dwie klasy:

• układy licznikowe, dokonujące pomiaru czasu przez zliczane ilości

impulsów o znanym czasie trwania,

• układy relaksacyjne, w których pomiar czasu jest wykonywany

techniką analogową, najczęściej poprzez dobór stałych czasowych

układu RC, natomiast wejście i wyjście układu odpowiadają standardowi sygnałów cyfrowych.

Przedmiotem ćwiczenia jest zbadanie układów z drugiej grupy.

Do realizacji ćwiczenia wykorzystywany jest modułowy zestaw elementów logicznych UNILOG-2.

8.2. PODSTAWOWE WIADOMOŚCI TEORETYCZNE

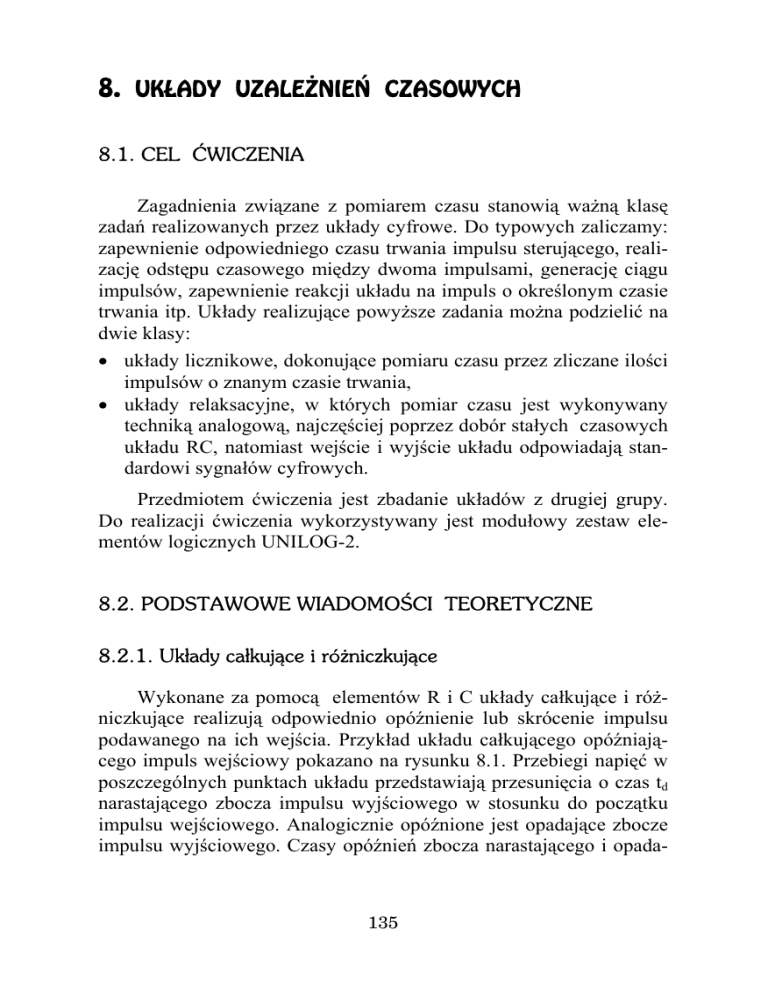

8.2.1. Układy całkujące i różniczkujące

Wykonane za pomocą elementów R i C układy całkujące i różniczkujące realizują odpowiednio opóźnienie lub skrócenie impulsu

podawanego na ich wejścia. Przykład układu całkującego opóźniającego impuls wejściowy pokazano na rysunku 8.1. Przebiegi napięć w

poszczególnych punktach układu przedstawiają przesunięcia o czas td

narastającego zbocza impulsu wyjściowego w stosunku do początku

impulsu wejściowego. Analogicznie opóźnione jest opadające zbocze

impulsu wyjściowego. Czasy opóźnień zbocza narastającego i opada-

135

jącego na ogół nie będą jednakowe. Z wartości czasu opóźnienia td

wynika maksymalna szybkość zmian przebiegu wejściowego Uwej,

przy której będzie następowało przechodzenie sygnału przez układ.

Należy ją tak dobrać, aby czas pomiędzy zboczami narastającym i

opadającym impulsu wejściowego był większy niż opóźnienie impulsu td określone stałą RC. Kształt impulsu wyjściowego będzie idealnie

prostokątny tylko wówczas, gdy B2 jest bramką z wejściem Schmitta.

W innych przypadkach w celu uzyskania odpowiedniej stromości

impulsu wyjściowego należy dołączyć do wyjścia układu dwie bramki

zwykłe.

Uwej

U1

Uwej

R

Uc

UwyjU 1

t

B2

B1

Uc

C

t

U wyj

t

td

t

Rys. 8.1. Układ całkujący opóźniający impuls wejściowy oraz przebiegi napięć

w poszczególnych punktach układu

Przykład realizacji układu różniczkującego pokazano na rysunku

8.2. Uwidocznione na nim przebiegi napięć pokazują reakcję układu

na opadające zbocze impulsu wejściowego. Przedstawione rozwiązanie może być zastosowane w układach, w których ujemne zbocze

impulsu ma sterować wejściem wyzwalanym poziomem, np. wejściami zerującymi lub ustawiającymi licznika. Istotne jest, że czas trwania

impulsu wyjściowego to nie zależy od czasu trwania impulsu wejściowego, ale od wartości elementów R i C.

Efekt różniczkowania narastającego zbocza impulsu można uzyskać w układzie z rysunku 8.3. Wykorzystywane jest tu opóźnienie

136

wnoszone przez układ zbudowany z nieparzystej liczby bramek logicznych, a nie przez układ RC.

Uwej

Uwyj

1цF

U1

Uc

200Ω

Uwej

U1

Uc

Uwyj

Rys.8.2. Układ różniczkujący opadające zbocze impulsu wejściowego oraz przebiegi napięć w poszczególnych punktach układu

Rys.8.3. Układ różniczkujący narastające zbocze impulsu wejściowego z wykorzystaniem czasu opóźnienia propagacji bramek

Na rysunku 8.4 przedstawiono układ generujący krótki impuls

dodatni w odpowiedzi zarówno na zbocze narastające, jak i opadające

impulsu wejściowego. Wykorzystano w nim układy całkujące opóźniające impuls wejściowy; elementy R1, C1 opóźniają zbocze narastające impulsu wejściowego, jednocześnie ich wartości określają czas

trwania impulsu będącego odpowiedzią na zbocze narastające, nato-

137

miast elementy R2, C2 analogicznie działają przy zboczu opadającym.

Układ ten jest powielaczem częstotliwości przez dwa. Przebieg wyjściowy nie jest symetryczny, wypełnienie różni się od 50%. Aby

układ działał poprawnie, stałe R1, C1 i R2, C2 muszą być odpowiednio dobrane do częstotliwości przebiegu wejściowego.

UB1 =Uwej. U C1

U wej

B1

R1

U wyj

U C1

B0

B3

C1

B2

R2

UC2

U B2=U wej. UC2

C2

Rys.8.4. Układ dwuzboczowy generujący krótki impuls dodatni

dla narastającego i opadającego zbocza przebiegu wejściowego

8.2.2. Przerzutnik monostabilny

Przerzutnik monostabilny (uniwibrator, monoflop) jest układem,

który generuje w odpowiedzi na pobudzenie pojedynczy impuls, samoczynnie kończący się po czasie Tw , gdzie Tw jest stałym, niezależnym od sygnału wejściowego, czasem trwania impulsu. Z określenia tego wynika, że przerzutnikiem monostabilnym może być układ z

rysunku 8.2 po wprowadzeniu sprzężenia zwrotnego w sposób, który

uniezależnia czas trwania impulsu wyjściowego od czasu trwania impulsu wejściowego.

Przykładowe rozwiązanie przerzutnika monostabilnego wraz z

przebiegami w charakterystycznych punktach przedstawiono na rysunku 8.5. Zasadniczym przerzutnikiem jest układ złożony z bramek

B1, B2 i elementów R i C, którego pobudzeniem jest ujemny impuls

UR1. Do prawidłowej pracy tego przerzutnika wymagane jest, aby

138

długość impulsu U R1 była mniejsza od Tw, dlatego na wejściu układu

dołączono dodatkowe elementy B0, R1 i C1 negujące i różniczkujące

impuls Uwe. Przy jednakowych wartościach rezystorów R=R1 wartość

C1 musi być znacznie mniejsza od C.

Uwe

C

UR1

t

UR

B1

B2

Q

t

C1<C

R<3k Ω

R1=R

UR

t

Q

B0

TH

Uwe

Uwyj (Q)

t

Uwyj (Q)

Rys.8.5. Przerzutnik monostabilny z układem różniczkującym RC i sprzężeniem

zwrotnym

Przerzutniki monostabilne są wykonywane w wersji scalonej i

oznaczone numerem katalogowym UCY 74121 (pojedynczy układ,

bez wejścia zerującego, bez przedłużania impulsu wyjściwego) oraz

UCY 74123 (układ podwójny z wejściami zerującymi oraz możliwością przedłużenia impulsu w trakcie jego trwania).

Schemat przerzutnika monostabilnego UCY 74121 przedstawiono na rysunku 8.6. Przerzutnik ma wejścia A1 i A2, reagujące na zbocze opadające, oraz wejście B, reagujące na zbocze narastające. Wejścia A1 i A2 wymagają odpowiednio dużej stromości zbocza impulsu

wyzwalającego (nie mniejszej niż 1 V/µs), natomiast wejście B jest

wejściem Schmitta i zmiana sygnału może być na nim wolna (nie

mniejsza niż 1 V/s). Na rysunku 8.7 pokazano trzy sposoby dołączenia

zewnętrznych elementów R i C, służących do ustalenia czasu trwania

impulsu wyjściowego.

Rezystancja wewnętrzna Ri nie charakteryzuje się dużą stałością,

dlatego też w układach o wysokich wymaganiach stałości czasu trwa-

139

nia generowanego impulsu nie należy jej wykorzystywać. Typowa

wartość Ri wynosi 2 kΩ.

Do celów inżynierskich wygodnie jest korzystać z nomogramów

przedstawionych między innymi w [4]. Na ich podstawie można określić długość impulsu dla pary wartości R i C lub dobrać wartość jednego elementu dla danej wartości drugiego i zadanego czasu trwania

impulsu.

+5V

We A1 lub A2

(B=1)

R

C

11

t

10

Q

3

4

We B

6

t

( A1 lub A2=0)

t

A1

_

A2

5

Q

Q

1

B

t

Rys.8.6. Schemat przerzutnika monostabilnego UCY 74121 oraz przebiegi czasowe

+5V

+5V

+5V

11

10 9

Ri

3

4

A1

A2

5

B

R

C

C

6

_

Q

1

Ri

3

4

A1

A2

5

B

T = C Ri ln2

Q

_

Q

10 9

11

10 9

11

Q

C

6

1

Ri

3

4

A1

A2

5

T = C(Ri+R) ln2

6

Q

_ 1

Q

B

T = R C ln2

Rys. 8.7. Sposoby dołączenia kondensatora zewnętrznego C

i rezystora zewnętrznego R do przerzutnika monostabilnego UCY 74121

Układ UCY 74123 zawiera dwa niezależne, identyczne przerzutniki monostabilne. Na rysunku 8.8 przedstawiono jego schemat funk-

140

cjonalny oraz przykładowe przebiegi czasowe. Przerzutnik ten posiada

dwie, ważne z punktu widzenia użytkownika, funkcje:

• możliwość regeneracji (ang. retriggerable) impulsu wyjściowego,

• możliwość zakończenia generacji impulsu wyjściowego w dowolnej chwili poprzez podanie impulsu zerującego R = 0.

b1)

b1)

a)a)

A

R

B

Q

R=1

Q

T

T

b2)

b2)

A

_

A

Q

B

R=1

B=1

C

R

Q

T

b3)

b3)

+5V

B

R=1

A=0

Q

T

Rys.8.8. Przerzutnik monostabilny UCY 74123: a) schemat funkcjonalny,

b1÷b3) przykładowe przebiegi czasowe

Jeżeli w układzie UCY 74123 wykorzystuje się kondensatory elektrolityczne, to należy dodatkowo włączyć diodę krzemową. Sposób jej

dołączenia został pokazany na rysunku 8.9. Czas trwania impulsu

wyjściowego T należy wówczas obliczyć na podstawie zależności:

T = 0,28 RC (1+ 0,7/ R)

Przy zastosowaniu kondensatorów nieelektrolitycznych o wartości

C < 1000 pF czas trwania impulsu należy określić na podstawie nomogramów, które zostały przedstawione między innymi w [4]. Natomiast dla C > 1000 pF czas ten określa się z zależności:

T = 0,32 RC (1 + 0,7/ R)

141

Przerzutnik monostabilny może być stosowany do realizacji układu

selektora impulsów. Przykład selektora impulsów, który odfiltrowuje

sygnały o czasie trwania mniejszym niż zadany, przedstawia rysunek 8.10. Układ taki może służyć

do odfiltrowywania krótkotrwałych

impulsów zakłócających. Chcąc

uzyskać impuls wyjściowy o stałej

standardowej długości, należy dołączyć do wyjścia układu z rysunku

8.10 jeszcze jeden przerzutnik

monostabilny.

Rys.8.9. Sposób dołączenia kondensatora elektrolitycznego do układu 74123

142

t

Rys.8.10. Selektor impulsów o czasie trwania Twe > Tw

oraz przebiegi czasowe

8.2.3. Przerzutnik astabilny

Przerzutnik astabilny, zwany multiwibratorem, to układ, który

posiada dwa stany niestabilne i jest cyklicznie przełączany z jednego

stanu w drugi i z powrotem, wyjście układu przyjmuje cyklicznie wartości 0 i 1. Wykorzystywany jest jako generator fali prostokątnej.

Generatory takie są stosowane jako zegary układów sekwencyjnych,

zegary pomiarowe, źródła przebiegu o zadanej częstotliwości dla monitorów, wyświetlaczy itp. W układach o wymaganej wysokiej dokładności częstotliwości używane są multiwibratory stabilizowane

rezonatorami kwarcowymi.

Przykłady rozwiązań układowych przerzutnika astabilnego

przedstawiono na rysunku 8.11. Podano na nim zależności lub tablice

umożliwiające określenie częstotliwości generowanej fali prostokątnej. W układzie z rysunku 8.11c zastosowana jest bramka zlinearyzowana (B1), będąca w zasadzie wzmacniaczem liniowym, z kolei w

układzie z rysunku 8.11d użyto zlinearyzowanej bramki Schmitta.

143

a)

b)

Rys.8.11a,b

144

c)

R=200Ω

c)

Uwyj

B1

1

~

f=

B2

3RC

C

R

d)d)

390Ω

C

Uwyj

C

UCY74132 lub UCY7413

f

20pF 21,7MHz

100pF 10,6MHz

1nF

1,6MHz

10nF

195kHz

100nF 21,6kHz

Rys.8.11. Przykłady rozwiązań układowych przerzutnika astabilnego: a) multiwibrator z dwoma układami różniczkującymi, b) multiwibrator z układem opóźniającym RC, c) multiwibrator ze zlinearyzowaną bramką, d) multiwibrator z bramką Schmitta

8.3. PRZEBIEG ĆWICZENIA

1. Zbudować układ z rysunków 8.1 i 8.2. Układy pobudzać prostokątnym przebiegiem okresowym z zewnętrznego generatora. Zaobserwować na oscyloskopie przebiegi w charakterystycznych punktach

układu dla kilku wartości pojemności C i oporności R.

UWAGA: Elementy R i C należy określić przed przystąpieniem do ćwiczenia (w domu). W sprawozdaniu zamieścić oscylogramy.

2. Zbudować układ z rysunku 8.3 zawierający 5 oraz 11 negatorów. Badanie układu przeprowadzić analogicznie jak w punkcie 1. Dla

obu przypadków określić czas trwania impulsu na wyjściu układu.

145

3. Zbadać układ przedstawiony na rysunku 8.4. Zaobserwować

na oscyloskopie dwukanałowym zjawisko powielania częstotliwości.

W sprawozdaniu zamieścić przebiegi czasowe.

4. Zbadać układ przerzutnika monostabilnego z rysunku 8.5.

Zbadać zależność czasu trwania impulsu wyjściowego od wartości

pojemności C. Sprawdzić, jak będzie zachowywał się układ, gdy C1

będzie większa od C. Uzasadnić uzyskany efekt. W sprawozdaniu

zamieścić przebiegi czasowe.

5. Zbadać układy UCY 74121 oraz UCY 74123. Zaobserwować

zmianę długości impulsu wyjściowego w funkcji zmian R i C. Dobrać

wartości R i C tak, aby uzyskać długość impulsu określoną przez prowadzącego. W sprawozdaniu przedstawić przebiegi czasowe.

6. Zbadać układ z rysunku 8.10. Płynnie zmniejszać częstotliwość impulsów wejściowych aż do zaniku obrazu na ekranie oscyloskopu (Twe < Tw). W sprawozdaniu przedstawić przebiegi czasowe.

7. Zbudować dwa spośród czterech multiwibratorów z rysunku

8.11. Sporządzić wykresy przedstawiające zależność częstotliwości

oraz współczynnika wypełnienia przebiegu wyjściowego od wartości

pojemności.

8. Zbudować generator fali prostokątnej z wykorzystaniem układów UCY 74121 lub UCY 74123 oraz dowolnych bramek. Układ

powinien być wyposażony w dwa niezależne wejścia START oraz

STOP.

Uwaga !! wszystkie rysunki z przebiegami czasowymi muszą posiadać wyskalowane osie.

146

8.4. ZAGADNIENIA KONTROLNE

1. Uzasadnić, dlaczego czas opóźnienia td w układzie z rysunku 8.1

jest różny dla zbocza narastającego i zbocza opadającego impulsu

wejściowego.

2. Zaprojektować układ analogiczny do układu z rysunku 8.3, ale

reagujący na zbocze opadające. Czas propagacji (tzn. czas pomiędzy zboczem aktywnym sygnału wejściowego a zboczem narastającym impulsu wyjściowego) układu musi również wynosić tp

(czas propagacji pojedynczej bramki), a więc nie wchodzi w grę

trywialne rozwiązanie, polegające na dodaniu jednej bramki na

wejściu.

3. Dobrać taką liczbę bramek w układzie z rysunku 8.3, aby czas

trwania impulsu wyjściowego był równy ~100 ns.

4. Na podstawie układu z rysunku 8.4 zrealizować powielacz częstotliwości przez dwa tak, aby wypełnienie wyjściowej fali prostokątnej wynosiło dokładnie 50% (poprzez dobór elementów RC

wchodzących w skład układu).

5. Omówić różnice pomiędzy układami UCY 74121 oraz UCY

74123.

6. Zaprojektować układ o działaniu przeciwnym do układu z rysunku 8.10, tj. selektor impulsów o czasie trwania Twe < Tw. Przedstawić przebiegi czasowe w poszczególnych punktach układu.

7. Wyjaśnić, jaką funkcję pełnią w układzie na rysunku 8.10 pojemność C1 oraz bramki B1 i B2.

8. Wykorzystując układ UCY 7474 (przerzutnik D) oraz dowolne

bramki, zaprojektować układ różniczkujący zbocze narastające

przebiegu wejściowego. Przedstawić przebiegi czasowe.

9. Przedstawić schemat logiczny uniwibratora o programowanym

czasie trwania impulsu, w którym np. C = const, a R = var. Narysować przykładowe przebiegi czasowe.

10. Przedstawić schemat logiczny generatora fali prostokątnej o niezależnym czasie trwania 0 i 1. Narysować przykładowe przebiegi

czasowe ilustrujące działanie układu.

147

11. Przedstawić schemat logiczny generatora fali prostokątnej o programowalnej liczbie impulsów. Narysować przykładowe przebiegi czasowe ilustrujące działanie układu.

12. Zaprojektować układ opóźniające zbocze rosnące sygnału wejściowego o czas T1 oraz zbocze opadające tego sygnału o czas

T2. Narysować przebiegi czasowe.

LITERATURA

1. KALISZ J., Podstawy elektroniki cyfrowej, WKiŁ, Warszawa 1991

2. Laboratorium podstaw techniki cyfrowej, praca zbiorowa pod red. L. Wasilewskiego WSM, Gdynia 1991

3. MAJEWSKI W., Układy logiczne, WN Warszawa 1993

4. PIEŃKOS J., TURCZYŃSKI J., Układy scalone TTL w systemach cyfrowych, WKIŁ, WARSZAWA 1986

5. SASAL W., Układy scalone UCA 64 / UCY 74. Parametry i zastosowania,

WKiŁ, Warszawa 1985

6. TRACZYK W., Układy cyfrowe. Podstawy teoretyczne i metody syntezy,

WNT, Warszawa 1986

148

9. PODSTAWOWE BRAMKI, GENERATORY ASTABILNE

I MONOSTABILNE C-MOS

9.1. CEL ĆWICZENIA

Celem ćwiczenia jest poznanie podstawowych charakterystyk

oraz parametrów opisujących układy C-MOS. Ćwiczenie umożliwia

również zapoznanie się z budową i zasadą działania wybranych rozwiązań układowych z zastosowaniem elementów C-MOS.

9.2. PODSTAWOWE WIADOMOŚCI TEORETYCZNE

9.2.1.Tranzystory MOS w cyfrowych układach scalonych

W zależności od sposobu wykonania tranzystora MOS możliwe

jest otrzymanie dwóch jego rodzajów:

• tranzystora z kanałem zubażanym, który przewodzi prąd między

źródłem a drenem przy zerowej wartości napięcia między bramką a

źródłem (UGS),

• tranzystora z kanałem wzbogacanym, w którym przewodnictwo

między drenem a źródłem uzyskuje się w przypadku istnienia pomiędzy bramką a źródłem napięcia UGS większego od napięcia progowego.

W zależności natomiast od przewodnictwa kanału wyróżnia się tranzystory z kanałem typu p lub n.

Początkowo w układach scalonych MOS stosowane były przede

wszystkim tranzystory ze wzbogaconym kanałem typu p (P-MOS) o

dużej wartości napięcia progowego. Dla tych tranzystorów napięcie

progowe jest definiowane jako napięcie, które powoduje wytworzenie

takiego kanału, że prąd między źródłem i drenem wynosi 1 µA. Natomiast dla tranzystorów z kanałem zubożonym napięcie progowe jest

określane jako te, które powoduje odcięcie, to znaczy zmniejsza prąd

pomiędzy drenem a źródłem poniżej 1 µA. Rozwój technologii spo-

149

wo-dował produkcję tranzystorów niskoprogowych, a następnie układów z tranzystorami z kanałem typu n (N-MOS). Technologia MOS z

kanałem typu n charakteryzuje się znacznym zmniejszeniem czasów

propagacji (ok. 40 ns dla pojedynczej bramki); związane to jest z trzykrotnie większą ruchliwością elektronów w porównaniu z ruchliwością dziur w kanale typu p. Bramki wykonane w technologii N-MOS

charakteryzują się obniżonym napięciem progowym tranzystorów, co

pozwala na zasilanie układów napięciem +5 V (możliwa jest więc ich

bezpośrednia współpraca z układami TTL). Symbole tranzystorów

MOS stosowane w układach scalonych przedstawiono na rysunku 9.1.

a)

b)

D

c)

d)

B

G

S

Rys 9.1. Symbole tranzystorów MOS: a) z kanałem wzbogaconym typu n,

b) z kanałem wzbogaconym typu p, c) z kanałem zubożonym typu n,

d) z kanałem zubożonym typu p

Układy

C-MOS

(ang. Complementary Metal-OxideSemiconductor) zawierają na wspólnym podłożu jednocześnie tranzystory MOS p-kanałowe i n-kanałowe, które pracują ze wzbogaceniem.

Charakteryzują się one:

• możliwością zasilania niestabilizowanym napięciem,

• możliwością stosowania jednego napięcia zasilania,

• dużą szybkością przełączania (15÷350 ns/bramkę),

• małym rozproszeniem mocy w warunkach statycznych

(ok.1 µW/bramkę),

• dużą odpornością na zakłócenia (ok.45% napięcia zasilania).

Produkowane przez CEMI układy cyfrowe C-MOS są oznaczone

sym-bolem MCY 70 lub MCY 64, po którym następuje trzycyfrowy

numer identyfikacyjny.

9.2.2. Podstawowe właściwości tranzystora MOSFET

150

Analiza charakterystyk układów C-MOS wymaga znajomości

podstawowych własności unipolarnego tranzystora MOSFET z kanałem typu n (rys. 9.2). Tranzystor pozostaje w stanie odcięcia, gdy

napięcie bramki jest niższe od napięcia progowego, które dla tranzystora z kanałem typu n wynosi około +2 V. W stanie przewodzenia,

gdy UDS > UGS - UTN (gdzie UDS to napięcie dren-źródło, UGS – napięcie bramki, a UTN – napięcie progowe), tranzystor jest nasycony i zachowuje się jak źródło prądowe. Natomiast dla niewielkich wartości

UDS, w obszarze nienasycenia, tranzystor można traktować jako opornik.

a)

b)

a)

D

DREN

b)

D

G

G

B

ŹRÓDŁO

109Ω

S

750Ω

1012 Ω

2,5pF

PODŁOŻE

BRAMKA

S

c)

30

IDS[mA]

UGS = 15 V

UTN

20

UTN = 2 V

10 V

UTN

10

5V

UTN

5

10

15

UDS [V]

Rys.9.2. Tranzystor polowy N-MOS: a) symbol, b) schemat zastępczy, c) charakterystyki prądowo-napięciowe

Charakterystyki tranzystora MOS z kanałem typu p są podobne

do charakterystyk przedstawionych na rysunku 9.2. Różnią się napięciem progowym, które w tym przypadku wynosi UTP = -3 V, oraz

151

mniejszą bezwzględną wartością prądu nasycenia przy tych samych

wartościach napięcia drenu i bramki.

9.2.3. Podstawowe charakterystyki i parametry charakzujące bramki C-MOS

tery-

Bramki C-MOS mają następujące podstawowe parametry i charakterystyki:

a/ Napięcie zasilania

Napięcie zasilania układów C-MOS wynosi 3 V÷18 V (czasami

3 V÷15 V lub 0,5 V÷20 V); wybór napięcia zasilania związany jest z

wymaganiami określającymi szybkość działania, moc rozpraszaną w

układzie oraz margines szumów.

b/ Charakterystyki przejściowe

Charakterystyka napięciowa przedstawia zależność napięcia wyjściowego od napięcia wejściowego, czyli U0 = f(UI). Charakterystyka

prądowa określa natomiast zależność prądu drenu (tożsamego z prądem zasilania) od napięcia wejściowego, czyli ID = f(UI).

c/ Charakterystyki wyjściowe

W odniesieniu do inwertera C-MOS dla stanów logicznych 1 i 0

charakterystyki wyjściowe wynikają bezpośrednio z charakterystyk

prądowo-napięciowych tranzystora P-MOS oraz N-MOS (rys. 9.2).

Dla bramek NAND i NOR wypływający prąd wyjściowy w stanie 1

(source current) lub wpływający w stanie 0 (sink current) zależy od

liczby wejść oraz od ich stanów logicznych. Na przykład dla dwuwejściowej bramki NAND stan 1 na wyjściu pojawi się wówczas, gdy

chociaż jedno z wejść ma stan 0; gdy tylko jedno wejście jest w stanie

0, to przewodzi jeden tranzystor, gdy oba wejścia są w stanie 0, to

przewodzą dwa tranzystory połączone równolegle. Wypływający

wówczas prąd wyjściowy może być dwukrotnie większy. Natomiast

prąd wyjściowy wpływający do bramki NAND przy stanie 0 na wyjściu ma wartość stałą. Dla bramki NOR sytuacja jest odwrotna, zmianom może ulegać prąd wyjściowy wpływający w stanie 0, natomiast

prąd wyjściowy wpływający w stanie 1 jest stały. Ze zmianami prądów związany jest problem łączenia nie wykorzystanych wejść w

bramkach wielowejściowych. Dla bramek NAND nie wykorzystane

152

wejścia należy połączyć z sygnałem odpowiadającym jedynce logicznej, natomiast dla bramek NOR – z zerem logicznym. Wówczas występują najmniejsze wartości prądów wyjściowych. Gdy obciążenie w

jednym ze stanów jest duże (gdy jako obciążenie zastosujemy np.

diodę świecącą), celowo należy zastosować w układzie bramkę o

większej liczbie wejść. Zwierając wejścia takiej bramki zwielokrotniamy dopuszczalny wyjściowy prąd (rys. 9.3).

a)

a)

b) b)

UDD

Rys. 9.3. Przykłady możliwości zwiększania prądu wyjściowego bramki C-MOS:

a) w stanie 1, b) w stanie 0

d/ Moc rozpraszana

Składowymi mocy rozpraszanej są:

• straty mocy wynikające z prądu upływu - charakteryzują one pobór

mocy w warunkach statycznych; są proporcjonalne do napięcia zasilania i złożoności układu,

• straty mocy powstałe w wyniku przepływu prądu przez oba tranzystory komplementarne w chwili przełączania; moc ta zależy od

stromości opadania/narastania sygnału oraz od częstotliwości napięcia wejściowego,

• straty mocy wynikające z przeładowania pojemności obciążenia; są

one proporcjonalne do wartości pojemności, częstotliwości przełączania i kwadratu napięcia zasilającego.

e/ Czas przełączania i propagacji

Każdy układ C-MOS jest w zasadzie obciążeniem pojemnościowym. Podczas wzrostu napięcia zasilania, powodującego również

wzrost napięcia wejściowego i wyjściowego w stanie wysokim, bramka C-MOS musi przeładować pojemność obciążenia w szerszym zakresie napięciowym. Ponieważ prąd wyjściowy jest wprost proporcjonalny do kwadratu napięcia wyjściowego, to wraz ze wzrostem napięcia zasilania czas narastania, opadania i propagacji sygnału maleją.

153

Przykładowo dla bramki NAND C-MOS przy napięciu zasilającym 5

V czas propagacji wynosi około 50 ns, natomiast przy napięciu 10 V

czas ten maleje do około 30 ns. W układach C-MOS występuje więc

ścisła zależność pomiędzy szybkością działania a obciążeniem tych

układów.

f/ Odporność szumowa

Margines szumów dla układów C-MOS wynosi około 45% napięcia zasilania.

9.2.4. Podstawowe bramki C-MOS

Najprostszym układem cyfrowym jest inwerter (bramka NOT).

Składa się on z dwóch komplementarnych tranzystorów MOS

(rys. 9.4.) Jeżeli napięcie wejściowe jest niższe od napięcia progowego UTN, to tranzystor T1 przewodzi, a tranzystor T2 jest odcięty. Prąd

płynący przez T1 jest w przybliżeniu równy zeru, ponieważ oporność

kanału T2 lub oporność wejściowa dodatkowego innego układu

C-MOS, obciążającego inwerter, jest duża. Wówczas też napięcie na

małej oporności przewodzącego kanału T1 jest prawie równa zeru

a)

b)b)

+UDD

a)

UDD

S

109Ω

D

UI

750Ω

T1(P)

2,5pF

B

1012 Ω

G

UO

UIL

D

109Ω

T2(N)

750Ω

S

2,5pF

B

1012 Ω

G

UOH=UDD

Rys.9.4. Inwerter C-MOS: a) układ podstawowy, b) schemat zastępczy - położenie kluczy odpowiada niskiemu poziomowi napięcia wejściowego

oraz UOH = UDD. W przeciwnym wypadku, gdy napięcie wejściowe

jest większe niż UDD - ⎮UTP⎮, tranzystor T2 przewodzi, a tranzystor

154

T1 jest odcięty, wtedy UO = UOL = 0. Stabilnymi stanami pracy poszczególnych tranzystorów jest stan odcięcia (oporność kanału jest

bardzo duża) oraz stan nienasycenia (oporność bardzo mała).

Każde wyprowadzone na zewnątrz wejście układu C-MOS jest

zabezpieczone przed przebiciem izolacji podbramkowej. Napięcie

przebicia bramki wynosi około 100 V. Wysoka oporność wejściowa

bramki powoduje podatność na uszkodzenia układu C-MOS nawet

przy małych ładunkach statycznych. Zabezpieczenie inwertera przed

przebiciem zostało przedstawione na rysunku 9.5. Dioda D3 o napięciu przebicia 80 V jest pasożytniczym elementem rozłożonym, który

pojawia się przy dyfuzyjnym kształtowaniu opornika R.

UDD

D3

UI

UZ230V

D2

1kΩ

U0

R

UZ130V

D1

Rys.9.5. Inwerter C-MOS z układem zabezpieczającym

Inwerter C-MOS może pracować w dużym zakresie napięć zasilających, gdyż napięcie progowe nie jest stałe, lecz zależy od napięcia

zasilania UDD (osiąga w przybliżeniu wartość 45% napięcia UDD).

Charakterystyka przejściowa inwertera dla różnych napięć zasilania

została przedstawiona na rysunku 9.6.

Układy C-MOS mogą być więc zasilane napięciem niestabilizowanym, na przykład bezpośrednio z baterii. Jest to oczywiście możliwe

przy wykorzystaniu w urządzeniu samych układów C-MOS. W odniesieniu do urządzeń, w których układy C-MOS współpracują z układami TTL, napięcie zasilania musi podlegać stabilizacji.

155

Rys.9.6. Charakterystyka przejściowa inwertera

Schematy dwuwejściowych bramek NAND oraz NOR zostały

przedstawione na rysunku 9.7. Na wyjściu bramki NOR otrzymamy

napięcie UDD wówczas, gdy tranzystory T1 i T2 będą w stanie przewodzenia, a tranzystory T3 i T4 w stanie odcięcia. Sytuację taka uzyskamy, podając na wejścia UI1 i UI2 napięcie odpowiadające zeru logicznemu.

a)

b)

Rys.9.7. Dwuwejściowa bramka: a) NOR, b) NAND

156

9.2.5. Przykłady zastosowań układów C-MOS

Schematy logiczne omawianych układów cyfrowych są niezależne od techniki realizacji zastosowanych w nich elementów logicznych.

Mogą nimi być zarówno układy scalone wykonane techniką C-MOS,

jak i układy bipolarne TTL. W prezentowanych zastosowaniach układowych skoncentrowano się jednakże na wykorzystaniu układów

scalonych typu C-MOS, co jest bezpośrednio związane z zakresem

ćwiczenia.

9.2.5.1. Generatory astabilne

Schemat logiczny przykładowego bramkowanego generatora

astabilnego przedstawiono na rysunku 9.8. Na wyjściu U2 występuje

ciąg impulsów prostokątnych, gdy na wejściu U1 pojawi się napięcie

odpowiadające zeru logicznemu. Dla napięcia zasilającego UDD = 10 V i

wartości elementów C = 1000 pF, R = 400 k Ω , R1 = 800 k Ω częstotliwość przebiegu wyjściowego wynosi 1 kHz, natomiast dla R1= 0

częstotliwość ta zwiększa się do 1,5 kHz.

U1

MCY 74001N

U2

R1

R

C

Rys.9.8. Generator astabilny

Innym przykładem jest układ scalony MCY 74047N zawierający

bramkowany generator astabilny oraz dodatkowe elementy logiczne

umożliwiające jego pracę w roli generatora monostabilnego wyzwalanego zboczem rosnącym lub malejącym. Strukturę logiczną układu

MCY 74047N przedstawiono na rysunku 9.9. W celu uzyskania poprawnej pracy układu w obu trybach należy do końcówek CTC i RCTC

dołączyć kondensator, a do końcówek RTC i RCTC– rezystor.

157

Układ MCY 74047N pracuje jako generator astabilny wówczas,

gdy na wejście ASTABLE i ASTABLE podamy napięcie odpowiadające jedynce logicznej (rys. 9.10). Oba te wejścia mogą więc być wykorzystywane jako wejścia bramkujące pracę generatora. Częstotliwość na wyjściu OSCILLATOR OUTPUT jest dwa razy większa niż

na wyjściach Q i Q .

Rys.9.9. Struktura logiczna układu MCY 74047N

a)

C

UDD

14

4

b)

R

t1=1,1RC

1

3

CTC

RCTC

2

RTC

UDD

6

OSC

OSC

A

MCY74047N

5

b)

Q

13

Q

10

A

Q

11

T-

USS

7

T+

8

R

9

Q

Ret

12

t2=2,2RC

Rys.9.10. Układ MCY 74047N jako generator astabilny: a) schemat,

b) przebiegi czasowe

9.2.5.2. Generatory monostabilne

158

Praca generatorów monostabilnych, podobnie jak astabilnych,

związana jest z przeładowaniem obwodu RC. W generatorach monostabilnych przeładowanie jest inicjowane impulsem zewnętrznym.

Układ generatora monostabilnego przedstawiono na rysunku 9.11.

UDD

a)

b)

R

We

C

We

Wy

Wy

tw

Rys.9.11. Podstawowy układ generatora monostabilnego: a) schemat,

b) przebiegi czasowe

Warunkiem generacji impulsu wyjściowego jest zmiana wartości sygnału na wejściu We z poziomu niskiego na wysoki. Na wyjściu inwertera pojawi się wysoki poziom napięcia, który będzie trwał tak

długo, aż kondensator nie naładuje się do napięcia progowego inwertera. Czas trwania impulsu wyjściowego jest w przybliżeniu równy

tw ≈ 0,7 RC. Tolerancja czasu tw ze względu na rozrzuty charakterystyk przejściowych inwerterów wynosi około ±50%. W razie konieczności uzyskania dokładniejszego czasu należy zastosować układ

przedstawiony na rysunku 9.12. W układzie tym należy zapewnić

jednakowe stałe czasowe R1 ⋅ C1 = R2 ⋅ C2. Wówczas czas trwania

impulsu wyjściowego określony jest zależnością tw = 1,4 ⋅ R1 ⋅ C1.

a)

We

R1

C1

b)

We

C2

Wy

R2

Wy

tw

Rys.9.12. Zmodyfikowana wersja generatora monostabilnego: a) schemat,

b) przebiegi czasowe

Tolerancja tego czasu zależna jest od różnicy charakterystyk przejściowych obu inwerterów (zaleca się stosowanie bramek z tego układu

scalonego).

159

Jak już wspomniano, układ MCY 74047N może pracować również jako generator monostabilny (rys. 9.13). Wówczas na wejściu

ASTABLE musi być poziom niski, natomiast na wejściu ASTABLE

poziom wysoki. Generator może być wyzwalany rosnącym zboczem

podawanym na wejście +TRIGGER, przy czym na wejściu

-TRIGGER musi być wówczas niski poziom napięcia. Generator

można również wyzwolić za pomocą opadającego zbocza podawanego na wejście -TRIGGER przy wysokim poziomie napięcia na wejściu

+TRIGGER. W przypadku pracy monostabilnej istnieje możliwość

wydłużenia czasu trwania impulsu wyjściowego (tak jak dla układu

TTL UCY 74123N), co uzyskuje się przez jednoczesne podanie rosnących zboczy na wejścia RETRIGGER i +TRIGGER.

a)

a)

C

UDD

14

b)

b)

R

1

3

CTC

RCtC

2

UDD

OSC

4 A

A

MCY74047N

8

5

T+

RTC

Q

13

OSC

Q

T+

Q

t1

10

11

t2

A

USS

7

T-

6

R

9

Q

Ret

12

t1 t==1,38RC

1,38RC

t2 t=12=2,48RC

2,48RC

Rys.9.13. Układ scalony MCY 74047N jako generator monostabilny: a) schemat;

b) przebiegi czasowe

9.2.6. Współpraca układów C-MOS z układami TTL

Bezpośrednie sterowanie podstawowego układu TTL przez układ

C-MOS nie jest możliwe. Obciążalność wyjściowa C-MOS pozwala

tylko na bezpośrednie wysterowanie dwóch wejść układów TTL małej

mocy lub jednego wejścia układu TTL Shottky’ego również małej

mocy. W przypadku współpracy układów C-MOS z układami TTL

należy stosować układy buforowe:

• MCY 74049N (6 inwerterów mocy),

160

• MCY 74050N (6 wzmacniaczy).

Obciążalność wyjściowa tych układów umożliwia wysterowanie

dwóch standardowych wejść typu TTL. Dzięki tym układom możliwa

jest ponadto współpraca elementów TTL z elementami C-MOS, zasilanymi różnymi napięciami. Gdy bramka C-MOS powinna sterować

wejściami więcej niż dwóch bramek TTL, należy zastosować tranzystorowe układy wzmacniające.

Zagadnienia związane ze współpracą układów MOS-TTL oraz

TTL-MOS zostały dokładnie omówione w literaturze [1], [4].

9.2.7. Zasada stosowania układów MOS

Ze względu na dużą stałoprądową rezystancje wejściową układy

scalone MOS są podatne na uszkodzenia wywołane przez akumulację

ładunku statycznego. Przykładowy sposób zabezpieczenia wejścia

inwertera przedstawiono na rysunku 9.5. Metody zabezpieczenia

wejść układów MOS nie zapobiegają uszkodzeniu układów wskutek

gromadzenia się ładunku statycznego, są on bowiem skuteczne tylko

wówczas, gdy końcówki zasilania układu zostały uziemione lub połączone z napięciem zasilania. Stosując układy MOS należy przestrzegać następujących zasad:

• układy muszą być przechowywane wyłącznie w metalowych pojemnikach lub umieszczone w gumie przewodzącej,

• montaż układów MOS na pakietach powinien być wykonany z

pomocą izolowanej lutownicy, stoły robocze muszą być wyłożone

gumą przewodzącą lub folią metalową,

• wejścia układów MOS połączone z łączówkami pakietów powinny

być zabezpieczone rezystorem szeregowym rzędu 1-100 k Ω i rezystorem przyłączonym między wejściem a jednym z napięć zasilania lub masą,

• wejścia, które nie są używane, należy połączyć z napięciem zasilania lub masą (zależnie od rodzaju układu).

9.3. PRZEBIEG ĆWICZENIA

161

1. Wyznaczyć charakterystyki przejściowe i wyjściowe inwertera, bramki NAND i bramki NOR dla różnych napięć zasilających.

Schematy pomiarowe należy przygotować w domu przed przystąpieniem do ćwiczenia.

2. Zbadać działanie generatora astabilnego zbudowanego zgodnie ze schematami na rysunkach 9.8 i 9.10. Zarejestrować przebiegi

wyjściowe.

3. Zbadać działanie generatora monostabilnego zbudowanego

zgodnie ze schematami przedstawionymi na rysunkach 9.11, 9.12 i

9.13. Zarejestrować przebiegi wyjściowe. Elementy R i C należy dobrać przed przystąpieniem do ćwiczenia (w domu).

4. Zaprojektować i zbadać działanie generatora astabilnego mającego możliwość regulacji częstotliwości i współczynnika wypełnienia oraz możliwość blokowania generatora w stanie wysokim lub niskim na wyjściu. Projekt należy przygotować w domu przed przystąpieniem do ćwiczenia.

Sprawozdanie powinno zawierać schematy układów pomiarowych

oraz przebiegi czasowe badanych układów. Należy wykreślić charakterystyki badanych elementów zaznaczając poziomy odpowiadające

jedynce i zeru logicznemu. W sprawozdaniu powinno się ponadto

zamieścić wnioski i uwagi wynikające z przebiegu ćwiczenia.

Uwaga !! wszystkie rysunki z przebiegami czasowymi muszą posiadać wyskalowane osie.

162

9.4. ZAGADNIENIA KONTROLNE

1. Omówić działanie układu zabezpieczającego wejście inwertera

C-MOS.

2. Rozpatrzyć negatywne skutki obecności układu zabezpieczającego

wejście inwertera C-MOS.

3. Omówić czynniki wpływające na straty układu C-MOS. Przedstawić i omówić charakterystykę strat mocy inwertera C-MOS.

4. Omówić działanie dwuwejściowych bramek NAND i NOR.

5. Omówić problemy obciążalności statycznej bramek NAND i

NOR.

6. Podać sposoby zabezpieczenia układów C-MOS przed uszkodzeniami elektrostatycznymi.

7. Określić sposób postępowania z nie wykorzystanymi wejściami

układów C-MOS.

8. Podać przykład zastosowania układów scalonych MCY 74049N i

MCY 74050N.

9. Podać przykłady buforów tranzystorowych.

10. Omówić zasady sterowania układem C-MOS przez układ TTL.

11. Zmodyfikować układ przedstawiony na rysunku 9.8 tak, aby była

możliwość regulowania współczynnika wypełnienia przebiegu

wyjściowego.

12. Podać przykłady zastosowania układów C-MOS w przełącznikach dotykowych.

13. Omówić wady i zalety tranzystorów z kanałem typu n oraz p.

14. Omówić bramki transmisyjne.

15. Omówić charakterystyki statyczne układów C-MOS.

16. Omówić charakterystyki dynamiczne układów C-MOS.

17. Omówić odporność na zakłócenia statyczne i dynamiczne układów C-MOS.

18. Porównać właściwości układów serii C-MOS i TTL.

163

LITERATURA

1. GAJEWSKI P., TURCZYŃSKI J., Cyfrowe układy scalone CMOS, WKiŁ,

Warszawa 1990

2. Laboratorium podstaw techniki cyfrowej, praca zbiorowa pod red. L. Wasilewskiego, WSM, Gdynia 1991

3. ŁAKOMY M., ZABRODZKI J., Układy scalone CMOS, PWN, Warszawa

1991

4. PIEŃKOS J., TURCZYŃSKI J., Układy scalone TTL w systemach cyfrowych, WKiŁ, Warszawa 1986

164