Paweł Bogumił BRYŁA – IV rok

Koło Naukowe Techniki Cyfrowej

Dr inŜ. Wojciech Mysiński – opiekun naukowy

PROGRAMMABLE DEVICES

UKŁADY PROGRAMOWALNE

Keywords: PAL, PLA, PLD, CPLD, FPGA, programmable device, electronic circuit, logic,

array, field

Słowa kluczowe: PAL, PLA, PLD, CPLD, FPGA, układ programowalny, układ elektroniczny,

logiczne, matryca

UKŁADY PROGRAMOWALNE

1. Wprowadzenie

Układy cyfrowe moŜna podzielić na dwie grupy – standardowe układy scalone oraz na

tzw. układy ASIC (Application Specific Integrated Circuit). W przypadku zwykłych układów

scalonych ich właściwości funkcjonalne są ustalane w procesie produkcji i nie mogą być

później zmieniane. Natomiast właściwości układów ASIC są określane w zaleŜności od

potrzeb przez ostatecznego uŜytkownika, a nie przez producenta. Do grona układów ASIC

moŜna zaliczyć układy programowalne PLD (Programmable Logic Devices), ale biorąc pod

uwagę moŜliwość wielokrotnego przeprogramowywania większości układów PLD oraz

łatwość ich wytwarzania, stanowią one jakby odrębną rodzinę.

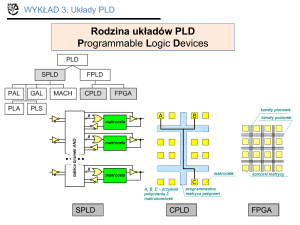

Układy programowalne moŜna podzielić na:

•

SPLD (Simple Programmable Logic Device) – proste układy programowalne

•

CPLD (Complex Programmable Logic Device) – złoŜone układy programowalne

•

FPGA (Field Programmable Gate Array) – programowalne matryce bramkowe

Konfigurowanie układów programowalnych moŜe odbywać się następującymi metodami:

1. Odpowiednio przygotowane ścieŜki do przepalenia (przez przepuszczenie prądu o duŜym

natęŜeniu) – podczas programowania takie zwarcia są usuwane. Układy te mogą być

programowane tylko raz.

2. Elementy nie przewodzące, w których podczas programowania następuje przebicie

dielektryka między warstwami przewodzącymi, połączenia te charakteryzują się małą

rezystancją połączeń. RównieŜ jednokrotnie programowalne. Układy te mogą być

programowane przez końcowego uŜytkownika.

3. Z wykorzystaniem tranzystorów MOS, które po włączeniu w stan przewodzenia zwierają

ścieŜki; istnieje tu kilka moŜliwości wykorzystania tranzystorów: jako komórki pamięci

EPROM, EEPROM, Flash lub zwykłe tranzystory MOS, które są zasilane z pamięci

statycznej RAM. Układy tego typu są reprogramowalne. W układach z pamięcią RAM po

wyłączeniu zasilania konfiguracja logiczna jest tracona. Po ponownym włączeniu

zasilania następuje ładowanie konfiguracji z zewnętrznych pamięci konfiguracyjnej.

Układy FPGA programowane w ten sposób mogą być rekonfigurowane w czasie pracy.

UŜywając układów programowalnych moŜna zaoszczędzić miejsce na płytce drukowanej

oraz stosować zasilanie o mniejszej mocy. Zmniejszony pobór mocy w porównaniu ze

standardowymi układami elektronicznymi uzyskuje się dzięki wysokiemu stopniowi scalenia

oraz mniejszej liczbie zacisków zewnętrznych.

2. Układy PLD (SPLD)

Do układów SPLD zalicza się przede wszystkim układy o architekturach PLA i PAL. Są

to najtańsze i najprostsze układy. WiąŜą się z tym niestety niezbyt duŜe moŜliwości logiczne.

Układy PLD są układami o małej skali integracji. Zawierają nie więcej niŜ 500 bramek

logicznych, 24 makrokomórki i nie więcej niŜ 40 linii I/O. Układy te są produkowane głównie

w technologii CMOS.

PAL (Programmable Array Logic)

Rys. 1. Schemat logiczny układu PAL

Architektura PAL składa się z dwóch matryc: AND i OR. Matryca AND jest

programowalna a matryca OR skonfigurowana na stałe. Funkcje logiczne są realizowane jako

sumy iloczynów sygnałów wejściowych.

PLA (Programmable Logic Array)

Rys. 2. Schemat logiczny układu PLA

Układ ten róŜni się od PAL tylko tym, Ŝe występującą tu matryca OR jest programowalna

tak jak matryca AND.

W większości produkowanych układów PLD, programowalne matryce AND są

wyposaŜane w dodatkowe linie, którymi są doprowadzane sygnały sprzęŜenia zwrotnego

z wyjść matrycy OR, przerzutników wyjściowych lub innych elementów makrokomórek

wyjściowych.

Podstawowe parametry czasowe to: czas propagacji (tPD; to czas, który upływa od

momentu wystąpienia zmiany na zewnętrznych zaciskach układu do momentu ustalenia się

wartości na wyjściu układu kombinacyjnego), czas ustawiania (tS; to minimalny czas,

w którym sygnał wejściowy przerzutnika musi być stabilny przed nadejściem zbocza

wyzwalającego sygnału zegarowego), czas trzymania (tH; to minimalny czas, w którym

sygnał na wejściu przerzutnika musi być stabilny po wystąpieniu zbocza wyzwalającego

sygnału taktującego), opóźnienie sygnału taktującego do wyjścia (tCO; czas jaki upływa od

momentu zmiany sygnału taktującego podanego na zewnętrzny zacisk układu do chwili

ustalenia się stabilnego stanu na innym zacisku zewnętrznym układu), opóźnienie propagacji

sygnału taktującego przez matrycę logiczną do wyjścia (tCO2; ), opóźnienie zegara

systemowego do zegara systemowego (tSCS; minimalny czas sygnału taktującego, wymagany

do wykonania operacji logicznych w strukturze między rejestrami; naleŜy tu wliczyć czasy

ustawiania obydwu rejestrów). Maksymalna częstotliwość pracy jest określana wg zaleŜności:

f max = 1

t SCS

.

3. Układy CPLD

Układy CPLD są podobne do układów SPLD, ale mają większe zasoby logiczne

i moŜliwości funkcjonalne. Zawierają od kilkudziesięciu do kilkuset makrokomórek

łączonych w większe bloki logiczne po 4÷16 (struktura hierarchiczna). Układy CPLD

wytwarzane są zwykle w technologii MOS i wyposaŜane w pamięć EPROM, EEPROM

i Flash. Pierwsze układy CPLD oparte były na technologii PAL, przy znacznie zwiększonym

wymiarze programowalnej matrycy AND. Dzięki temu uzyskano znaczne zwiększenie ilości

sygnałów wejściowych, a takŜe większą liczbę rejestrów wyjściowych. To rozwiązanie było

jednak za wolne, co było wynikiem zwiększenia się pojemności pasoŜytniczych. Kolejna

architektura była takŜe oparta na strukturach PAL, ale połączono je szybką, programowaną

matrycą połączeniową. We współczesnych układach CPLD matryce połączeniowe

realizowane są w postaci programowalnych multiplekserów, które dostarczają sygnały z linii

wejściowych i sprzęŜenia zwrotnego do bloków logicznych. Czas propagacji nie przekracza

zwykle 3 ns. Czasy te są róŜne w zaleŜności od producenta i uŜytych technologii. Matryce

połączeniowe wykonywane są takŜe jako wielopoziomowe. W układach tych jest moŜliwe

poprowadzenie wszystkich połączeń, czyli dowolne wejście do połączenia programowalnego

moŜe być połączone z dowolnym blokiem logicznym, o ile nie wykorzystano juŜ wszystkich

wejść danego bloku. Rozmiar bloku logicznego określa jego moŜliwości czyli liczbę

elementów logicznych, które moŜna w nim zaimplementować. WaŜnym elementem jest takŜe

liczba wejść do bloku, liczba iloczynów oraz schemat rozprowadzenia tych iloczynów

wewnątrz struktury. Większość linii iloczynowych moŜe być uŜywana przez cztery sąsiednie

makrokomórki, bez ryzyka wystąpienia dodatkowych opóźnień. Sygnały wejściowe mogą być

kombinacyjne, zatrzaskowe lub zapisywane w rejestrze. Czasem sygnał asynchroniczny

względem zegara systemowego jest synchronizowany przez dwa przerzutniki, aby zwiększyć

niezawodność systemu. Parametry czasowe są takie same jak w przypadku układów SPLD:

czas propagacji, czas ustawiania, opóźnienie sygnału taktującego do wyjścia oraz czas

przejścia sygnału od rejestru do rejestru. W przypadku układów CPLD mamy do czynienia

z kilkoma własnościami, które odróŜniają je między sobą, a mianowicie: programowanie

układu w systemie (ISP – In System Programmability), przeprogramowanie układu

w systemie (ISR – In System Reprogrammability), napięcie pracy (5V lub 3,5 V), port dla

sygnałów testujących i moŜliwość testowania przez złącze obserwacyjno-testujące (JTAG –

Joint Test Action Group) oraz bufory wejściowe i wyjściowe, które są zgodne ze standardem

połączeń PCI (Peripherial Component Interconnect)

Rys. 3. Schemat logiczny układu o architekturze CPLD

4. Układy FPGA

Układy FPGA składają się z bloków logicznych rozmieszczonych matrycowo,

połączonych za pomocą tras i matryc kluczy połączeniowych, umieszczonych na przecięciu

tras poziomych i pionowych. Na brzegach znajdują się programowalne bloki we/wy.

Zawierają zwykle od 64 do dziesiątków tysięcy bloków logicznych. Bloki logiczne

w układach FPGA mogą być bardzo zróŜnicowane. ZłoŜone bloki zawierają dwie lub więcej

pamięci RAM i dwa lub więcej przerzutników. W prostszych blokach występują zwykle

dwuwejściowe układy generacji funkcji kombinacyjnych lub czterowejściowe multipleksery

i przerzutniki. Układy FPGA charakteryzują się duŜą liczbą sygnałów we/wy oraz duŜym

upakowaniem rejestrów. UmoŜliwiają zwiększenie, w dość znacznej mierze, stopnia scalenia.

MoŜna je programować i przeprogramowywać w systemie.

Architektura komórek logicznych jest róŜna, w zaleŜności od tego w jaki sposób są

wykonywane połączenia. W strukturach z izolowanymi połączeniami moŜna stosować

większą liczbę sygnałów we/wy dzięki duŜej ilości linii do przenoszenia sygnałów

i bezpieczników, dzięki którym moŜna wykonać prawie wszystkie dowolne połączenia.

W układach opartych na technologii SRAM komórki logiczne są większe o mniejszej liczbie

we/wy. Nadają się one do implementacji skomplikowanych funkcji logicznych bez większego

wpływu na opóźnienia.

Wadą układów FPGA jest to, Ŝe połączenia między blokami są zestawiane z części, co

moŜe prowadzić do występowania opóźnień. Pod tym względem układy CPLD są lepsze

poniewaŜ posiadają ciągłe połączenia dzięki czemu opóźnienia są mniejsze, stałe

i przewidywalne. Powszechnie stosowane są wejścia i obwody specjalnego przeznaczenia

charakteryzujące się niskim poziomem zniekształceń, którymi rozprowadzane są sygnały

zegarowe. Układy FPGA mogą pracować zasilane napięciami 5V i 3,5V, z niskim poborem

mocy. Mogą być takŜe testowane przez złącze obserwacyjno-testujące zgodne ze standardem

JTAG. Posiadają zgodność sygnałów we/wy ze standardem PCI.

Rys. 4. Architektura układu FPGA

LITERATURA

[1] Pasierbiński Jerzy, Zbysiński Piotr: „Układy programowalne”, WKŁ, Warszawa 2002.

[2] Skahill Kevin: „Język VHDL”, WNT, Warszawa 2001.

[3] Zwoliński Mark: „Projektowanie układów cyfrowych z wykorzystaniem języka VHDL”, WKŁ, Warszawa

2002.

[4] http://www.xilinx.com/

[5] http://www.altera.com/