MINISTERSTWO EDUKACJI

NARODOWEJ

Ryszard Zankowski

Uruchamianie układów i systemów mikroprocesorowych

312[02].Z1.01

Poradnik dla ucznia

Wydawca

Instytut Technologii Eksploatacji – Państwowy Instytut Badawczy

Radom 2007

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

Recenzenci:

mgr inż. Zbigniew Miszczak

mgr inż. Krzysztof Słomczyński

Opracowanie redakcyjne:

mgr inż. Ryszard Zankowski

Konsultacja:

mgr Małgorzata Sienna

Poradnik stanowi obudowę dydaktyczną programu jednostki modułowej 312[02].Z1.01.

„Uruchamianie układów i systemów mikroprocesorowych”, zawartego w programie

nauczania dla zawodu technik teleinformatyk.

Wydawca

Instytut Technologii Eksploatacji – Państwowy Instytut Badawczy, Radom 2007

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

1

SPIS TREŚCI

1.

2.

3.

4.

5.

6.

Wprowadzenie

Wymagania wstępne

Cele kształcenia

Materiał nauczania

4.1. Charakterystyka procesorów i rodzajów pamięci

4.1.1. Materiał nauczania

4.1.2. Pytania sprawdzające

4.1.3. Ćwiczenia

4.1.4. Sprawdzian postępów

4.2. Zasada działania procesora

4.2.1. Materiał nauczania

4.2.2. Pytania sprawdzające

4.2.3. Ćwiczenia

4.2.4. Sprawdzian postępów

4.3. System mikroprocesorowy

4.3.1. Materiał nauczania

4.3.2. Pytania sprawdzające

4.3.3. Ćwiczenia

4.3.4. Sprawdzian postępów

Sprawdzian osiągnięć

Literatura

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

2

3

5

6

7

7

7

17

17

19

20

20

34

34

36

37

37

45

45

47

48

52

1. WPROWADZENIE

Poradnik będzie Ci pomocny w przyswajaniu wiedzy o podstawowych zagadnieniach

dotyczących funkcjonowania i budowy systemów mikroprocesorowych.

W poradniku zamieszczono:

– wymagania wstępne – wykaz umiejętności, jakie powinieneś mieć już ukształtowane,

abyś bez problemów mógł korzystać z poradnika,

– cele kształcenia – wykaz umiejętności, jakie ukształtujesz podczas pracy z poradnikiem,

– materiał nauczania – wiadomości teoretyczne niezbędne do opanowania treści jednostki

modułowej,

– zestaw pytań, abyś mógł sprawdzić, czy już opanowałeś określone treści,

– ćwiczenia, które pomogą Ci zweryfikować wiadomości teoretyczne oraz ukształtować

umiejętności praktyczne,

– sprawdzian postępów,

– sprawdzian osiągnięć, przykładowy zestaw zadań. Zaliczenie testu potwierdzi

opanowanie materiału całej jednostki modułowej,

– literaturę uzupełniającą.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

3

312[02].Z1

Urządzenia komputerowe

312[02].Z1.01

Uruchamianie układów

i systemów

mikroprocesorowych

312[02].Z1.02

Identyfikowanie podzespołów

komputera i ich parametrów

312[02].Z1.03

Budowanie i uruchamianie

zestawów komputerowych

312[02].Z1.04

Eksploatowanie i zabezpieczanie

urządzeń komputerowych

Schemat układu jednostek modułowych

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

4

2. WYMAGANIA WSTĘPNE

–

–

–

–

–

–

–

−

−

−

−

−

−

−

−

–

–

–

Przystępując do realizacji programu jednostki modułowej powinieneś umieć:

stosować jednostki układu SI,

przeliczać jednostki,

posługiwać się podstawowymi pojęciami z zakresu elektrotechniki, elektroniki,

rozróżniać podstawowe wielkości elektryczne i ich jednostki,

odczytywać schematy prostych układów elektrycznych i elektronicznych,

łączyć układy elektryczne i elektroniczne zgodnie ze schematem,

wyjaśniać działanie prostych układów elektronicznych na podstawie ich schematów,

zapisywać liczby w różnych kodach,

wykonywać operacje logiczne i arytmetyczne na liczbach zapisanych w różnych kodach,

rozpoznawać bramki logiczne, przerzutniki, bloki funkcjonalne na podstawie symboli

graficznych, tabel prawdy, tabel stanów, tabel wzbudzeń lub grafów przejść,

klasyfikować układy logiczne,

analizować działanie elementów i bloków funkcjonalnych, wchodzących w skład

układów cyfrowych,

porównywać parametry cyfrowych układów scalonych wykonanych w różnych

technologiach,

obserwować stany logiczne oraz przebiegi na wejściach i wyjściach układów za pomocą

przyrządów specjalistycznych lub oscyloskopu,

obsłużyć wybrany program wspomagający projektowanie układów logicznych,

korzystać z różnych źródeł informacji,

obsługiwać komputer,

współpracować w grupie.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

5

3. CELE KSZTAŁCENIA

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

−

W wyniku realizacji programu jednostki modułowej powinieneś umieć:

wyjaśnić funkcje i zasady współpracy poszczególnych bloków systemu mikroprocesorowego,

wyjaśnić koncepcje pamięci podręcznej,

scharakteryzować magistrale i sygnały sterujące mikroprocesora,

wyjaśnić działanie układów wejścia/wyjścia,

scharakteryzować operacje wejścia/wyjścia,

wyjaśnić schemat blokowy mikroprocesora,

wyjaśnić działanie mikroprocesora i jego bloków,

wyjaśnić funkcje rejestrów procesora,

rozpoznać tryby pracy mikroprocesora,

opisać tryby pracy procesora,

zidentyfikować listę rozkazów procesora,

rozpoznać tryby adresowania,

zaprogramować system mikroprocesorowy,

rozpoznać typy obudów procesorów i gniazd,

porównać podstawowe parametry poszczególnych modeli procesorów,

porównać zasadę działania pamięci dynamicznej i statycznej RAM,

opisać pamięci ROM,

opisać organizacja pamięci.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

6

4. MATERIAŁ NAUCZANIA

4.1.

Charakterystyka procesorów i rodzajów pamięci

4.1.1. Materiał nauczania

Rodzaje pamięci w komputerach

Pamięci półprzewodnikowe są jednym z kluczowych elementów systemów cyfrowych.

Służą do przechowywania informacji w postaci cyfrowej. Liczba informacji, które mogą

przechowywać pojedyncze układy scalone pamięci, zawiera się w zakresie od kilobajtów do

gigabajtów.

Pamięciami półprzewodnikowymi nazywamy cyfrowe układy scalone przeznaczone do

przechowywania większych ilości informacji w postaci binarnej. Podstawowymi parametrami

pamięci są pojemność, czas dostępu i transfer danych.

Pojemnością pamięci nazywamy maksymalną liczbę informacji, jaką możemy

przechować w danej pamięci. Pojemność pamięci podajemy w bitach (b) lub bajtach (B).

Czasem dostępu do pamięci nazywamy czas, jaki musi upłynąć od momentu podania

poprawnego adresu słowa w pamięci do czasu ustalenia się poprawnej wartości tego słowa na

wyjściu pamięci w przypadku operacji odczytu lub w przypadku operacji zapisu – czas, jaki

upłynie do momentu zapisania wartości do tego słowa z wejścia pamięci.

W technice komputerowej używane są głównie pamięci półprzewodnikowe o dostępie

swobodnym (w odróżnieniu od dostępu sekwencyjnego). Pamięcią o dostępie swobodnym

nazywamy pamięć, dla której czas dostępu nie zależy od adresu słowa w pamięci, czyli od

miejsca, w którym jest dana informacja. Pamięci o dostępie swobodnym dzielimy na dwie

grupy tzn. pamięci RAM i ROM.

Pamięcią RAM nazywamy pamięć półprzewodnikową o dostępie swobodnym

przeznaczaną do zapisu i odczytu. RAM jest pamięcią ulotną, co oznacza, że po wyłączeniu

jej zasilania informacja w niej przechowywana jest tracona.

Pamięcią ROM nazywamy pamięć półprzewodnikową o dostępie swobodnym

przeznaczaną tylko do odczytu. ROM jest pamięcią nieulotną.

–

–

–

–

Rodzaje pamięci stałych tzn. takich, które nie tracą zawartości po wyłączeniu zasilania:

pamięci typu ROM (ang. Read Only Memory). Zawartość tego typu pamięci ustalana jest

w trakcie produkcji i nie może być później w żaden sposób modyfikowana.

pamięci typu PROM (ang. Programmable Read Only Memory). Jest to rodzaj pamięci

ROM, który może być zaprogramowana przez programistę. Zawartość pamięci PROM

można tylko raz modyfikowana.

pamięci typu EPROM (ang. Erasable Programmable Read Only Memory). Jest to ten

rodzaj pamięci typu ROM, który można zapisywać i kasować dowolną ilość razy. Przed

zapisem poprzednią zawartość pamięci należy skasować promieniami UV.

pamięci typu EEPROM lub E2PROM (ang. Electrically Erasable Programmable Read

Only Memory). Ten rodzaj pamięci ROM może być dowolnie modyfikowana. Do

kasowania nie potrzeba żadnego promieniowania. Odbywa się ono w sposób elektryczny.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

7

Pamięci typu RAM (ang. Random Access Memory), które tracą zawartość po wyłączeniu

zasilania:

– pamięci statyczne SRAM (ang. Static Random Access Memory), statyczna pamięć nie

wymagające odświeżania, charakteryzujące się krótszym czasem dostępu, ale też

mniejszą pojemnością i wyższą ceną;

– pamięci dynamiczne DRAM (ang. Dynamic Random Access Memory), pamięci

dynamiczne, które wymagają złożonych układów sterujących i mają dłuższy czas

dostępu, ale za to mają większą pojemność i są tańsze;

– pamięci pseudostatyczne PRAM (ang. Pseudostatic Random Access Memory), mające

wewnętrzną strukturę pamięci dynamicznej, ale na zewnątrz zachowujące się jak pamięć

statyczna.

Pomiędzy pamięciami statycznymi i dynamicznymi występują istotne różnice

w parametrach i własnościach użytkowych. Pamięci dynamiczne są wolniejsze od

statycznych, natomiast są znacznie tańsze (szczególnie gdy uwzględniamy koszt jednego

bitu). Ponadto pamięci dynamiczne znacznie łatwiej podlegają scaleniu, co oznacza, że dla

porównywalnej wielkości układu uzyskujemy znacznie większe pojemności. Wadą pamięci

dynamicznych jest również fakt, że dla ich funkcjonowania konieczny jest tak zwany proces

odświeżania. Polega on na cyklicznym, ponownym odnowieniu przechowywanej zawartości

w komórce pamięci.

Z porównania własności tych pamięci wynika miejsce ich zastosowania w technice

komputerowej. Pamięci dynamiczne stosowane są do budowy głównej pamięci operacyjnej

komputera, co wynika z ich niskiej ceny i dużych pojemności układów scalonych tej pamięci.

Wadą tych pamięci w porównaniu z pamięciami statycznymi jest przede wszystkim szybkość

ich działania. Jednak ze względów ekonomicznych (cena) i technologicznych (mniejszy

stopień scalenia) nie można zbudować pamięci operacyjnej z pamięci statycznych. Dlatego

w systemach komputerowych stosuje się tak zwaną pamięć podręczną (cache), o znacznie

mniejszej pojemności w porównaniu z pamięcią operacyjną. Pamięć cache buduje się

z pamięci statycznych.

Organizacja pamięci

Organizacją pamięci nazywamy sposób podziału obszaru pamięci na słowa.

W dalszej części tego rozdziału będziemy używać terminów „adres” i „słowo”. Mimo że

terminy te nie sprawiają kłopotu naszej intuicji, podamy ich definicje.

Adresem nazywamy niepowtarzalną liczbę (numer) przypisaną danemu miejscu (słowu)

w pamięci w celu jego identyfikacji.

Słowem w pamięci nazywamy zestaw pojedynczych komórek (pojedynczych bitów)

pamięci, do którego odwołujemy się pojedynczym adresem.

Rys. 1. Wyprowadzenia układu scalonego pamięci [8]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

8

Szyna wejścia/wyjścia danych (DB, zaciski te często są też oznaczane jako DQ) służy do

wprowadzania i wyprowadzania informacji do i z pamięci. Wejście adresowe służy do

dokonania wyboru, na którym z wielu słów w pamięci zostanie wykonana operacja (zapisu

bądź odczytu). Wejście sterujące R/W# informuje układ pamięci, jakiego rodzaju operacja

będzie wykonywana: odczyt czy zapis. Wejście CS# służy do uaktywnienia układu pamięci.

Wejście to jest używane przy budowie zespołów pamięci metodą łączenia dwóch lub więcej

układów scalonych pamięci.

Liczbę bitów w pojedynczym słowie pamięci będziemy nazywać długością słowa

pamięci. Zauważmy, że długość słowa pamięci musi być równa liczbie wyprowadzeń szyny

wejścia/wyjścia, gdyż słowa są wprowadzane i wyprowadzane z pamięci równolegle.

Z warunku unikalności adresu (czyli nie powtarzania się tego samego adresu) wynika z kolei

minimalna liczba linii szyny adresowej. Przy m-bitowej szynie adresowej mamy do

dyspozycji 2m różnych adresów. Jeżeli liczba słów przechowywanych w pamięci wynosi N,

musi być spełniony warunek:

N < 2m

lub inaczej, aby poprawnie zaadresować N słów, potrzebujemy

m = log2N

bitów adresu (lub linii adresowych).

Wartość pojemności pamięci, długości słowa oraz liczby linii adresowych wiąże prosty

i oczywisty wzór. Jeżeli liczbę bitów możliwych do zapamiętania oznaczymy przez M,

długość słowa przez n, a liczbę linii adresowych przez m, to spełniona jest zależność:

M = nx2m

Schemat blokowy układu scalonego pamięci DRAM oraz rodzaje jego wyprowadzeń

pokazane są na rysunkach.

Rys. 2. Wyprowadzenia pamięci DRAM [5]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

9

Rys. 3. Adresowanie słowa w pamięciach DRAM. [5]

Adres słowa, na którym chcemy wykonać operację, podawany jest w dwóch częściach

zwanych adresem wiersza i adresem kolumny. Zmniejsza to liczbę potrzebnych wyprowadzeń

szyny adresowej i upraszcza konstrukcję dekoderów adresu.

Z drugiej strony, układy logiczne kontrolera pamięci, sterujące pracą pamięci, muszą

dokonać konwersji adresu podawanego przez procesor czy innego zarządcę magistral na

postać wymaganą przez pamięć DRAM. Przykładowy układ dokonujący takiej konwersji

pokazany jest na rysunku 3. Sygnał podany na wejście multipleksera wybiera, czy starsza, czy

też młodsza część adresu jest podawana na jego wyjściu. Drobne różnice występują też

w wejściach sterujących pamięci. Zamiast wejścia R/W# mamy dwa wejścia: OE# –

zezwolenie na wyprowadzenie (odczyt) informacji (ang. Output Enable), i WE# – zezwolenie

na zapis (ang. Write Enable). Sygnał CE# (ang. Chip Enable) jest równoważny sygnałowi

CS#. Sygnały RAS# (ang. Row Ad-dress Strobe) odpowiedzialny jest za wybór określonego

wiersza w matrycy pamięci i CAS# (ang. Column Address Strobe) sygnał wyboru kolumny

pamięci.

Odświeżanie pamięci DRAM

Odświeżanie komórek pamięci DRAM polega na cyklicznym doładowywaniu

pojemności pamiętających przechowujących wartość 1. Częstotliwość odświeżania

zapewniająca poprawną pracę pamięci DRAM jest podawana przez producenta jako parametr

katalogowy, którego należy przestrzegać. Operacja odświeżania pamięci realizowana jest

przez układy logiczne odświeżania będące elementem systemu (płyty głównej).

−

−

−

−

Istnieją cztery podstawowe sposoby odświeżania pamięci dynamicznych RAM:

sygnałem RAS,

CAS przed RAS,

odświeżanie ukryte (ang. hidden refresh),

samoodświeżanie (ang. self-refresh).

Pierwszym sposobem, obecnie niemającym już znaczenia, jest odświeżanie sygnałem

RAS. Na sygnał z generatora odświeżania układy logiczne odświeżania przejmują kontrolę

nad magistralami (stają się zarządcą magistral). Następnie podają na magistralę adresową

zawartość tak zwanego licznika odświeżania. Licznik ten adresuje kolejne wiersze

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

10

przeznaczone do odświeżenia i po każdym odświeżeniu kolejnego wiersza jest zwiększany

o jeden. Po podaniu adresu generowany jest sygnał RAS powodujący odświeżenie

zaadresowanego wiersza. Wysoki stan sygnału CAS# powoduje, że wyjście danych pamięci

jest w stanie wysokiej impedancji.

Dwa następne sposoby wymagają obecności w układach pamięci wewnętrznego licznika

odświeżania. W sposobie CAS przed RAS sterownik DRAM wytwarza aktywny sygnał CAS,

a następnie sygnał RAS. W odpowiedzi na taką sekwencję układy pamięci DRAM odświeżają

wiersz wskazywany przez ich wewnętrzny licznik odświeżania. W pamięciach DDR

odpowiada to trybowi zwanemu autoodświeżaniem. Żądanie realizacji autoodświeżania jest

generowane przez kontroler pamięci (przykładowo dla pamięci 512 Mb DDR SDRAM jest

wymagany co około 7,5 μs).

Przy odświeżaniu ukrytym po wytworzeniu aktywnych poziomów sygnałów RAS i CAS

i odczycie komórki sygnał RAS zmienia kolejno stan na nieaktywny i aktywny przy stale

aktywnym sygnale CAS. Powoduje to pozostawienie zawartości odczytywanej komórki na

wyjściach danych przy jednoczesnym (równoległym) odświeżeniu wiersza zaadresowanego

przez wewnętrzny licznik odświeżania pamięci.

Przy odświeżaniu automatycznym układy logiczne odświeżania są zawarte wewnątrz układów

pamięci.

Pod względem rodzajów złącz pamięci można podzielić na:

–

DIP (ang.). Konstrukcja pamięci w formie zwykłego układu scalonego montowanego na

stałe na płycie układu mikroprocesorowego. Rozszerzenie rozmiaru takiej pamięci

wiązało się z koniecznością wylutowania kości pamięci z układu.

Rys. 4. Pamięć typu DIP [6]

–

SIPP (ang. Single Inline Pin Package). Druga generacja pamięci dynamicznych.

Wygodniejszy rodzaj pamięci niż DIP. W dowolnej chwili można było wymienić

dowolny moduł pamięci na inny.

Rys. 5. Pamięć typu SIPP [6]

–

SIMM (Single Inline Memory Module). Są to 30 pinowe moduły, które stosowano

w komputerach wyposażonych w procesor 0486. Najczęściej spotykanymi tego typu

układami są kości o pojemności 1, 4, 8 MB. Z uwagi na ich budowę mogły być

instalowane tylko parami po cztery sztuki. Obecnie częściej wykorzystuje się moduły

nowszego typu, 72 pinowe.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

11

Rys. 6. Pamięć typu SIMM [6]

–

PS/2 SIMM. Pod względem budowy wewnętrznej odpowiadają one 30 pinowym

modułom SIMM, są jednak przeznaczone do pracy z 32 bitową szyną danych. Z uwagi na

to, że architektura procesorów Pentium bazuje na magistrali 64bitowej, na płytach

pecetów z tym CPU niezbędne jest umieszczanie parami identycznych układów pamięci.

Zależnie od producenta płyty możliwe jest zainstalowanie od dwóch do ośmiu modułów,

czyli od jednej do czterech par.

Rys. 7. Pamięć typu PS/2 [6]

–

DIMM (ang. Dual In-Line Memory Module). Najpopularniejsze typy DIMM to:

72-pinowe, stosowane w SO DIMM (32 bitowe) i 144-pinowe, stosowane w SO DIMM

(64 bitowe) stosowany głównie w notebookach, komputerach małogabarytowych oraz

w niektórych drukarkach biurowych wysokiej klasy.

Rys. 8. Pamięć typu SO DIMM

168-pinowe, stosowane w SDR SDRAM. Pamięć SDR SDRAM jest taktowana

częstotliwościami 66, 100 i 133 MHz. Produkowane były kości 32, 64, 128, 256 i 512 MB.

184-pinowe, stosowane w DDR SDRAM. Stosowane są dwa rodzaje oznaczeń pamięci

DDR SDRAM. Mniejszy (np. PC-200) mówi o częstotliwości, z jaką działają kości.

Natomiast większy (np. PC1600) mówi o teoretycznej przepustowości jaką mogą osiągnąć.

240-pinowe, stosowane są w DDR2 SDRAM. Pamięć DDR2 charakteryzuje się wyższą

efektywną częstotliwością taktowania (533, 667, 800, 1066 MHz) oraz niższym poborem

prądu. Podobnie jak DDR, pamięć DDR2 wykorzystuje do przesyłania danych wznoszące

i opadające zbocze sygnału zegarowego, mogą pracować w temperaturze do 70°C. Moduły

pamięci DDR2 nie są kompatybilne z modułami DDR. Obecnie DDR2 obsługiwane są

zarówno przez procesory firmy Intel jak i AMD. Istnieją dwa sposoby oznaczania modułów

pamięci DDR2. Pierwszy z nich (np. PC2-533) mówi o prędkości modułu. Natomiast drugi

(np. PC2-6400) informuje o przepustowości.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

12

Rys. 9. Pamięć typu SDR 2 [6]

– DDR3 SDRAM (ang. Double Data Rate Synchronous Dynamic Random Access

Memory (ver. 3)). Jest to nowy standard pamięci RAM typu SDRAM, będący rozwinięciem

pamięci DDR i DDR2, stosowanych w komputerach jako pamięć operacyjna. Pamięć DDR3

wykonana jest w technologii 90 nm. Technologia ta umożliwia zastosowanie niższego

napięcia (1,5 V w porównaniu z 1,8 V dla DDR2 i 2,5 V dla DDR). Dzięki temu pamięć

DDR3 charakteryzuje się zmniejszonym poborem mocy o około 40% w stosunku do pamięci

DDR2 oraz większą przepustowością w porównaniu do DDR2 i DDR. Pamięci DDR3 nie

będą kompatybilne wstecz, tzn. nie będą współpracowały z chipsetami obsługującymi DDR

i DDR2. Posiadają także przesunięte wcięcie w prawą stronę w stosunku do DDR2 (w DDR2

wcięcie znajduje się prawie na środku obudowy). Obsługa pamięci DDR3 przez procesory

została wprowadzona w 2007 roku w procesorach firmy Intel oraz zostanie wprowadzona

w 2008 roku w procesorach firmy AMD.

Rys. 10. Pamięć typu DDR3 [6]

– RIMM (Rambus Inline Memory Module). Jest to jeden z rodzajów pamięci

komputerowej, na którym umieszczone są układy scalone z pamięcią Rambus DRAM

(RDRAM).

Rys. 11. Pamięć typu Rambus [6]

–

–

–

–

Najpopularniejsze pamięci typu RIMM:

160-pinowe, stosowane SO-RIMM,

184-pinowe, stosowane RIMM 16-bitowe,

232-pinowa, stosowane RIMM 32-bitowe,

326-pinowa, stosowane RIMM 64-bitowe.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

13

Rodzaje procesorów i gniazd.

Gniazdo procesora (ang. CPU socket lub CPU slot) jest to rodzaj złącza znajdującego się

na płycie głównej; pełni ono rolę interfejsu pomiędzy procesorem a pozostałymi elementami

systemu komputerowego umożliwiając jego współpracę z systemem za pośrednictwem

odpowiednich magistrali i układów znajdujących się na płycie głównej.

Na każdej płycie głównej musi być przynajmniej jedno takie gniazdo; determinuje ono

rodzaj procesora, jaki jest przez nią obsługiwany.

Producenci wyposażają swoje płyty w różne wersje gniazd umożliwiających

zastosowanie jednego z dostępnych procesorów, przy czym rodzaj procesora często zależy

również od zainstalowanego na płycie chipsetu. Dla procesorów Pentium i jego poprzedników

stosowano jednakowe podstawki, jednak począwszy od procesora Pentium II, zaczęto

projektować inne, zależnie od producenta.

Typ gniazda dla procesora musi być zgodny z określonym procesorem. Dla danego typu

gniazda charakterystyczny jest kształt, napięcie rdzenia, prędkość magistrali systemowej oraz

inne cechy. Na przykład Slot 1 – Celeron, Pentium II, Pentium III.

W pierwszych płytach głównych procesory były wlutowane, ale z powodu coraz większej

oferty procesorów i ich nieustannie zmieniającej się budowy pojawiły się gniazda, które

umożliwiły dopasowanie budowy płyty oraz jej możliwości do potrzeb danego użytkownika.

W efekcie użytkownik chcąc wymienić procesor na procesor innej firmy, musi wymieniać

całą płytę główną.

Najczęściej obecnie spotykanym gniazdem montowanym na płytach głównych jest

gniazdo typu ZIF. Gniazda te umożliwiają łatwą instalację procesora bez użycia siły,

wyposażone są bowiem w małą dźwigienkę, służącą do zaciskania lub poluzowania

znajdującego się w gnieździe procesora. Mikroprocesory posiadają piny, dzięki którym mogą

zostać zamontowywane w gnieździe. Należy bardzo uważać przy umieszczaniu

mikroprocesora w podstawce, gdyż zgięcie wyprowadzeń może trwale uszkodzić

mikroprocesor.

Podstawki firmy AMD i odpowiadające im typy procesorów:

– Socket 5 – AMD K5.

– Socket 7 – AMD K6.

– Super Socket 7 – AMD K6-2, AMD K6-III.

– Socket 462 (zwany także Socket A) – AMD Athlon, Duron, Athlon XP, Athlon XP-M,

Athlon MP, i Sempron.

Rys. 12. Podstawka typu Socket A [6]

–

–

–

Socket 463 (zwany także Socket NexGen) – NexGen Nx586.

Socket 563 – AMD Athlon XP–M (µ-PGA Socket).

Socket 754 – AMD Athlon 64, Sempron, Turion 64.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

14

Rys. 13. Podstawka typu Socket 754 [6]

–

–

–

–

–

–

–

Socket 939 – AMD Athlon 64, Athlon 64 FX, Athlon 64 X2, Sempron, Turion 64,

Opteron (seria 100). Obsługa podwójnego kanału pamięci DDR-SDRAM, tzw. dualchannel.

Socket 940 – AMD Opteron (seria 100, 200, 800), Athlon 64 FX. Obsługa podwójnego

kanału pamięci DDR-SDRAM, tzw. dual-channel.

Socket 1207 (zwane także Socket F) - Supports AMD Opteron (seria 200, 800). Zastąpił

Socket 940. Obsługa dual-channel DDR2-SDRAM.

Socket AM2 – AMD Athlon 64 FX, Athlon 64 X2, Sempron, Turion 64, Opteron (seria

100). Obsługa dual-channel DDR2-SDRAM. Posiada 940 pinów.

Socket AM2+ – AMD Athlon X2, Athlon X4, Phenom X2, Phenom X3, Phenom X4,

Sempron. Obsługa dual-channel DDR2-SDRAM, oraz Obsługa dual-channel DDR3SDRAM i HyperTransport 3 z mniejszym zapotrzebowaniem na energię. Posiada 940

pinów.

Socket AM3 – Przyszłe gniazgo pod procesor AMD, charakteryzujący się obsługą dualchannel DDR3-SDRAM, oraz HyperTransport 3. Planowany na II półrocze 2008.

Socket S1 - gniazdo na platformy mobilne, z obsługą dual-channel DDR2-SDRAM.

Podstawki Intel:

– 40 pin – Intel 8086, Intel 8088.

– 68 pin – Intel 80186, Intel 80286, Intel 80386.

– Socket 1 – 80486.

– Socket 2 – 80486.

– Socket 3 – 80486

Rys. 14. Podstawka typu Socket 3 [6]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

15

–

Socket 4 – Intel Pentium 60-66 MHz.

Rys. 15. Podstawka typu Socket 4 [6]

–

–

–

–

–

Socket 5 – Intel Pentium 75-133 MHz.

Socket 7 – Intel Pentium, Pentium MMX.

Socket 8 – Intel Pentium Pro.

Socket 370 – Intel Pentium III, Celeron; Cyrix III; VIA C3.

Socket 423 – Intel Pentium 4 z jądrem Willamette.

Rys. 16. Podstawka typu Socjet 423 [6]

–

Socket 478 – Intel Pentium 4, Celeron, Pentium 4 Extreme Edition, Pentium M.

Rys. 17. Podstawka typu Socket 478 [6]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

16

–

–

–

–

–

–

–

Socket 479 – Intel Pentium M i Celeron M.

Micro-FCBGA – Intel Mobile Celeron, Core 2 Duo (mobile), Core Duo, Core Solo,

Celeron M, Pentium III (mobile), Mobile Celeron.

Socket 486 – 80486.

Socket 603 – Intel Xeon.

Socket 604 – Intel Xeon.

LGA 771 (zwane także Socket 771 or Socket J) – Intel Xeon.

LGA 775 (zwane także Socket 775 or Socket T) – Intel Pentium 4, Pentium D, Celeron D,

Pentium Extreme Edition, Core 2 Duo, Core 2 Extreme, Celeron, Xeon seria 3000, Core 2

Quad.

Rys. 18. Podstawka typu Socket T [6]

–

–

PAC418 – Intel Itanium.

PAC611 – Intel Itanium 2.

4.1.2. Pytania sprawdzające

1.

2.

3.

4.

5.

6.

7.

8.

Odpowiadając na pytania, sprawdzisz, czy jesteś przygotowany do wykonania ćwiczeń.

Czy wiesz co to jest pamięć o dostępie swobodnym?

Jak działa pamięć statyczna?

Jakie są różnice pomiędzy pamięcią statyczną i dynamiczną?

Czy wiesz co to jest pamięć typu ROM?

Jakie są różnice między pamięciami ROM i RAM?

Jak jest zbudowany moduł pamięci typu SIMM?

Czy potrafisz scharakteryzować pamięć np. typu DDR3?

Co to jest gniazdo procesora?

4.1.3. Ćwiczenia

Ćwiczenie 1

Przedstaw rozwój procesorów i odpowiadających im podstawek.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) przeanalizować rozwój technologiczny patrząc na procesory pod kątem typu obudowy,

2) zwrócić uwagę jakie parametry procesorów zmieniały się z upływem czasu,

3) zapisać spostrzeżenia na arkuszu papieru.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

17

−

−

−

Wyposażenie stanowiska pracy:

plansze z rysunkami podstawek,

zdjęcia procesorów,

arkusz papieru, flamastry.

Ćwiczenie 2

Scharakteryzuj poznane pamięci typu DIMM.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) spośród dostępnych kości RAM wybrać te które mają obudowę typu DIMM,

2) posegregować wybrane przez Ciebie kości pamięci na odpowiednie grupy,

3) opisać te cechy, na podstawie których można podzielić pamięci w obudowach typu

DIMM.

−

−

−

Wyposażenie stanowiska pracy:

moduły pamięci różnych typów,

karty katalogowe elementów,

arkusz papieru, flamastry.

Ćwiczenie 3

W jaki sposób realizuje się odświeżania pamięci dynamicznych.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) zastanowić się i odpowiedzieć na pytanie w jakim celu stosuje się odświeżanie pamięci,

2) odpowiedzieć na pytanie, które bloki funkcjonalne odpowiedzialne są za procesy

odświeżania pamięci,

3) zastanowić się w jaki sposób działa mechanizm wybierania komórek pamięci do

odświeżenia.

−

−

Wyposażenie stanowiska pracy:

schemat blokowy pamięci dynamicznej,

literatura zgodna z punktem 6 poradnika.

Ćwiczenie 4

Określ podstawowe parametry charakteryzujące procesory i przedstaw ich zmiany

w czasie.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) określić jakie parametry charakteryzują procesory,

2) przedstawić spektrum zmian na przykładzie wybranych modeli procesorów.

−

−

Wyposażenie stanowiska pracy:

procesory różnych typów,

karty katalogowe elementów.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

18

Ćwiczenie 5

Scharakteryzuj poznane pamięci o dostępie swobodnym.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) odpowiedzieć na pytanie czym jest dostęp swobodny do pamięci,

2) określić jakimi rodzajami pamięci będziesz się zajmować.

−

−

Wyposażenie stanowiska pracy:

moduły pamięci różnych typów,

karty katalogowe elementów.

4.1.4. Sprawdzian postępów

Czy potrafisz:

1)

2)

3)

4)

5)

6)

7)

8)

wyjaśnić pojęcie pamięci o dostępie swobodnym?

wyjaśnić pojęcie pamięci statycznej?

wyjaśnić pojęcie pamięci dynamicznej?

określić podstawowe różnice między pamięcią RAM i ROM?

wyjaśnić do czego służy sygnał RAS?

wyjaśnić budowę modułu typu SIMM?

scharakteryzować pamięć typu DDR3?

wyjaśnić pojęcie gniazda procesora?

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

19

Tak

Nie

4.2.

Zasada działania procesora

4.2.1. Materiał nauczania

Procesor 8086

Jest to pierwszy 16-o bitowy procesor wyprodukowany dla komputerów osobistych firmy

IBM. Mimo znacznej rozbudowy obecnie produkowanych procesorów zawsze istnieje

możliwość pracy w trybie procesora 8086.

–

–

Centralny blok przetwarzający procesora składa się z dwóch części:

układu sprzęgającego magistrali (ang. BIU-Bus Interface Unit),

układu wykonawczego (ang. EU-Execution Unit).

Rys. 19. Schemat blokowy procesora 8086 [7]

–

–

–

Procesor 8086 posiada:

20 linii adresowych adresujących bezpośrednio 220=1 MB komórek pamięci,

16 linii adresowych dla rozkazów definiujące lokacje 216=64 KB portów WE/WY,

dwa niezależne układy operacyjne: dla realizacji kodu bieżącego (EU), dla równoległego

pobierania rozkazu następnego (BIU),

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

20

–

–

dwa tryby przetwarzania: w układzie maksymalnym, w układzie minimalnym,

możliwość współpracy z rodziną 8-o bitowych układów sprzęgających firmy Intel.

Układ wykonawczy (EU)

Układ wykonawczy procesora 8086 zawiera 16-bitową ALU współpracującą z rejestrami

wskaźnikowymi oraz rejestrami wewnętrznymi. Wszystkie rejestry i magistrale wewnętrzne

układu wykonawczego są 16-bitowe. Układ wykonawczy nie ma bezpośredniego kontaktu

z magistralą zewnętrzną. Rozkazy są do niej przekazywane z bloku rejestru FIFO (ang. FirstIn First-Out pierwszy wchodzi-pierwszy wychodzi) zwanego kolejką rozkazów. Kolejka

rozkazów jest zapełniana za pośrednictwem układu sprzęgającego BIU. Wszystkie adresy

generowane w obrębie układu wykonawczego są 16-bitowe, choć układ sprzęgający

magistrali steruje dwudziestoma liniami adresującymi 1 MB przestrzeni adresowej. Zadaniem

układu wykonawczego jest dekodowanie i wykonywanie rozkazów gromadzonych w kolejce.

W trakcie wykonywania rozkazów w układzie wykonawczym układ sprzęgający magistrali

zewnętrznej otrzymuje zezwolenie na pobranie następnego rozkazu z pamięci programu. Gdy

kolejnym bajtem w pamięci to dane, zostaną one pominięte w operacji przesłania do kolejki

rozkazów. Gdy zaś EU realizuje rozkaz skoku lub wywołania podprogramu, następuje

wówczas wyzerowanie kolejki i pobranie za pośrednictwem BIU rozkazów z przestrzeni

pamięci związanej z tym rozgałęzieniem.

Układ wykonawczy zawiera:

– 16-bitową jednostkę arytmetyczno-logiczną ALU,

– układ sterowania z rejestrem rozkazów,

– cztery 16-bitowe rejestry użytkownika: AX, BX, CX, DX LUB cztery pary 8-bitowych

rejestrów po 8 bitów: AL, AH, BL, BH, CL, CH, DL, DH (odpowiednio L – młodszy,

H – starszy bajt),

– cztery 16-bitowe rejestry adresowania:

SP (ang. Stack Pointer)

– wskaźnik stosu,

BP (ang. Base Pointer)

– wskaźnik bazy,

SI (ang. Source Pointer)

– indeksowy źródła danych,

DI (ang. Destination Pointer) – indeksowy przeznaczenia danych,

– 16-bitowy rejestr wskaźników – flagowy.

Rejestry

Rejestr jest częścią pamięci wewnętrznej procesora o niewielkiej (kilkubitowej)

pojemności. Pewne rejestry procesora związane są określonymi operacjami a z kolei

wykonywanie określonych operacji związane jest ściśle z określonymi rejestrami. Rejestry

są komórkami o czasie dostępu do pamięci krótszym niż w przypadku pamięci operacyjnej.

Ponieważ ilość rejestrów jest niewielka więc w ciele rozkazu wyraźnie wskazujemy,

na którym rozkaz wykonuje operację. Główne zadanie rejestrów to przechowywanie adresów

lub danych na potrzeby rozkazu. Mogą być używane do modyfikowania adresów,

zapamiętania adresu powrotu z podprogramów, jako liczniki rozkazów lub jako małe pamięci

podręczne.

Jednostka arytmetyczno-logiczna

Jest ona częścią procesora, która wykonuje operacje arytmetyczne typu dodawanie,

odejmowanie, a także elementarne operacje logiczne: sumowanie (OR), mnożenie (AND),

sumowanie modulo 2 (XOR).

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

21

Układ sprzęgający magistrali (BIU)

Układ sprzęgający – BIU (ang. Bus Interface Unit) procesora 8086 przesyła dane między

procesorem a pamięcią operacyjną lub układami WE/WY pod nadzorem układu

wykonawczego. W czasie gdy układ wykonawczy realizuje kolejny rozkaz, BIU pobiera

nowy rozkaz z pamięci operacyjnej i przekazuje go do kolejki. Wykorzystuje w ten sposób

stan wolnej magistrali zewnętrznej w trakcie operacji przetwarzania wewnętrznego w obrębie

układu wykonawczego procesora. W procesorach poprzedniej generacji pobranie

poprzedniego rozkazu uwarunkowane było zakończeniem przetwarzania poprzedniego

rozkazu. Zasada równoległego współdziałania obu układów wewnętrznych procesorów tzw.

trzeciej generacji została przedstawiona na rys. 20. jako schemat rozdziału faz pobierania –

FETCH i wykonania – EXECUTE.

Cykl pracy procesora 8086

Wykonanie kolejnych rozkazów procesora związane jest z sekwencją pewnych stałych

kroków zwanych fazami cyklu. W zależności od rodzaju rozkazu mogą wystąpić

maksymalnie cztery spośród pięciu faz cyklu:

− pobranie (ang. fetch) – kod rozkazu zostaje pobrany z pamięci do zestawu rejestrów

tworzących kolejkę rozkazów skąd trafi do rejestru rozkazów IR procesora;

− dekodowanie (ang. decode) – w tej fazie rozkaz jest dekodowany i ustalane są, jeśli

wymaga tego typ rozkazu, połączenia arytmometru z rejestrami, które mają dostarczyć

argumentów operacji;

− odczyt (ang. read) – jeżeli rozkaz wymaga argumentu z pamięci operacyjnej, to zostaje

obliczony jego adres, a następnie argument jest odczytywany i wprowadzany do

procesora;

− wykonanie (ang. execute) – w tej fazie operacja zdefiniowana rozkazem jest

wykonywana;

− zapis (ang. write) – jeżeli wynik operacji ma być umieszczony w pamięci operacyjnej, to

zostaje obliczony adres i wykonany zapis do pamięci.

Dzięki kolejce rozkazów jednostka wykonawcza oraz jednostka sprzężenia z magistralą

mogą pracować niezależnie i jest możliwe równoczesne wykonywanie dwóch faz należących

do cykli kolejnych rozkazów. Zwiększa to szybkość pracy całego systemu.

W mikroprocesorze 8086 pojemność kolejki wynosi 6 bajtów. Jeśli w kolejce zwolni się

miejsce na co najmniej dwa bajty, a jednostka wykonawcza nie żąda dostępu do magistrali, to

jednostka sprzężenia z magistralą wykonuje samodzielnie cykle pobrania, ustawiając

w kolejce rozkazów kolejne bajty kodu programu. Operacja ta może przebiegać równocześnie

z inną fazą cyklu, w której jednostka wykonawcza procesora nie odwołuje się do pamięci.

Jeżeli jednostka wykonawcza zażąda dostępu do magistrali w czasie, gdy jednostka

sprzężenia z magistralą dokonuje pobrania, to faza pobrania zostanie dokończona,

a potem uwzględnione żądanie układu wykonawczego.

Rys. 20. Realizacja 4 kolejnych rozkazów w procesorze 8086 [7]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

22

Powyżej przedstawiono przepływ rozkazów ilustrujący równoległą pracę jednostki

wykonawczej i jednostki sprzężenia z magistralą. Zacieniowano klatki ilustrujące fazy cyklu,

w których procesor odwołuje się do pamięci. Trzeci z kolei rozkaz ma podwójną długość, stąd

dwie fazy pobrania.

Rejestr flagowy

Procesor 8086 ma dziewięć 1-bitowych wskaźników (bitów flagowych), których wartości

są zapisywane w 16-bitowym rejestrze flagowym. Rozmieszczenie bitów pokazane jest na

rysunku.

Rys. 21. Rejestr wskaźnikowy [7]

Wskaźniki można podzielić na dwie grupy:

– Znaczniki stanu wewnętrznego,

– Znaczniki rozkazów sterujących.

Znaczniki wewnętrzne:

– C (ang. Carry) – przeniesienie; wartość 1 na tej pozycji oznacza przeniesienie zewnętrzne

dla operacji arytmetycznych całkowitoliczbowych,

– P (ang. Parity) – parzystość; wartość 1 na tej pozycji oznacza parzystą ilość jedynek

wyniku dowolnej operacji,

– A (ang. Auxiliary-Carry) – przeniesienie połówkowe; wartość 1 na tej pozycji oznacza po

czwartym bicie rezultatu operacji arytmetycznych BCD,

– Z (ang. Zero) – zero; wartość 1 na tej pozycji oznacza rezultat 0 operacji,

– S (ang. Sign) – znak; wartość 1 na tej pozycji oznacza ujemny wynik operacji

matematycznej całkowitoliczbowej,

– O (ang. Over-flow) – przepełnienie; wartość 1 na tej pozycji oznacza zbyt dużą liczbę dla

wyniku operacji arytmetycznej całkowitoliczbowej.

Znaczniki sterujące:

– T (ang. Trap) – jest znacznikiem pracy krokowej procesora; gdy T=1 wówczas procesor

przechodzi do pracy krokowej tzn. następuje zatrzymanie po każdym rozkazie, wywołane

jest przerwanie 1 a CPU przesyła zawartość rejestru flagowego na stos (jak dla obsługi

przerwań),

– I (ang. Interrupt enable) – znacznik wskazujący, czy wejście przerwania maskowanego

INTR jest odblokowane (I=1), czy zablokowane (I=0),

– D (ang. Direction) – znacznik sterowania kierunkiem zmian zawartości rejestrów SI i DI.

Dla D=0 zawartość zwiększa się o 1 przy operacjach 8-bitowych oraz o 2 dla

16-bitowych.

Dla D=1 zawartość zmniejsza się o 1 przy operacjach 8-bitowych oraz o 2 dla

16-bitowych.

Znaczniki stanu wewnętrznego ustawiane są w wyniku wykonywania określonych

operacji arytmetycznych lub logicznych procesora, natomiast znaczniki sterujące są ustawiane

przez programistę za pomocą odpowiednich rozkazów w celu wymuszenia określonego trybu

pracy.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

23

Rejestry ogólnego przeznaczenia

Procesory 16-bitowe zawierają blok ośmiu 16-bitowych rejestrów ogólnego

przeznaczenia. Można w nich wyróżnić trzy grupy rejestrów o zdefiniowanym przeznaczeniu:

– rejestry danych: cztery 16-bitowe, w których wyróżniono bajt starszy H (H – high) i bajt

młodszy L (ang. L – low),

– rejestry wskaźników adresowych: stosu i bazy,

– rejestry indeksów adresowych: źródła i miejsca przeznaczenia.

Niektóre grupy rozkazów odnoszą się do operandów 8-bitowych inne do 16-bitowych.

Rozkazy operujące słowem 16-bitowych oznaczono przez X np. AX, BX .

Rejestry segmentowe

Megabajt przestrzeni pamięciowej jest adresowany przez procesor za pomocą 20-bitowej

magistrali adresowej. Obszar podzielono na segmenty po 64 KB a procesor ma bezpośredni

dostęp do czterech segmentów. Lokacja początkowa tych segmentów (16 starszych bitów

słowa 20-bitowego) jest zapisywana w rejestrach segmentowych: CS, DS, SS, ES:

– segment kodów – CS, wskazuje część adresu (16 bitów), odnoszą się do obszaru pamięci,

w których zapisano kody rozkazów,

– segment stosu – SS, zawiera 16 bitów adresu, które lokalizują obszar pamięci traktowany

jako stos, przechowujący dane restartów przerwań,

– segment danych – DS, wskazuje 16 bitów adresu komórek pamięci, które zawierają dane,

głównie zmienne programu,

– segment dodatkowy – ES, wykorzystywany jako dodatkowy obszar pamięci do zapisu

danych programu.

Wskaźnik instrukcji – IP

Wskaźnik IP (ang. instruction pointer) zwany wskaźnikiem instrukcji lub wskaźnikiem

rozkazów jest to rejestr mikroprocesora zawierający adres komórki pamięci, w którym

przechowywany jest kod rozkazu przeznaczonego do wykonania jako następny. Zawartość

wskaźnika rozkazów modyfikuje układ sprzęgający magistrali (BIU). Przed zapisaniem IP na

stos następuje modyfikacja jego zawartości tak, aby po powrocie do tej lokalizacji został

wskazany następny rozkaz w programie. W czasie normalnej pracy procesora IP zawiera

offset adresu wskazujący kolejny rozkaz w segmencie programu.

Stosem nazywamy obszar pamięci określany wg. określonych reguł:

– pamięć typu stos działa jak stos książek położonych jedna na drugiej,

– informacje odczytujemy w kolejności odwrotnej do kolejności zapisu,

– informacja odczytywana jest z ostatnio zapełnionej komórki, natomiast zapisujemy do

pierwszej wolnej. Komórkę odczytaną traktujemy jako wolną.

Tryby pracy wybranych procesorów

Procesor 80286

W mikroprocesorze 80286 pojawiły się mechanizmy sprzętowe ułatwiające realizację

pracy wielozadaniowej oraz pamięci wirtualnej. Obydwa pojęcia wiążą się z projektowaniem

nowoczesnych systemów operacyjnych i tam też głównie znalazły zastosowanie. Z drugiej

strony zapewniono kompatybilność tego procesora z procesorem 8086/88.

Procesor 80286 może pracować w jednym z dwóch trybów:

Trybie rzeczywistym (ang. real modę) – w trybie tym zachowuje się jak szybki procesor

8086. Między innymi używa tylko 20 bitów adresu (co pozwala zaadresować jedynie 1 MB

pamięci). Jednocześnie może być uruchomiony tylko jeden program główny.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

24

Chronionym trybie wirtualnym (ang. protected virtual mode), zwanym dalej trybem

chronionym lub trybem wirtualnym. W trybie tym procesor wykorzystuje swoje pełne

możliwości. Używa 24 bitów adresu, co pozwala zaadresować 16 MB fizycznej pamięci.

Ponadto dostępne są sprzętowe mechanizmy wspomagające obsługę pamięci wirtualnej, pracy

wielozadaniowej i ochrony zasobów. Procesor 80286 po restarcie rozpoczyna pracę w trybie

rzeczywistym. Przełączenie procesora na tryb chroniony następuje po ustawieniu bitu PE

(ang. Protect enable) w rejestrze MSW (ang. machinę status word) znajdującym się w zespole

rejestrów sterujących w BIU.

Procesor 80386

Procesor 80386 jest pierwszym 32-bitowym mikroprocesorem rodziny Intel x86, od

którego rozpoczęło się tworzenie architektury IA 32. Architektura ta jest kompatybilna wstecz

z 16-bitowymi procesorami rodziny Intel x86. Sposób realizacji instrukcji ulegał natomiast

znacznym zmianom w trakcie rozwoju tej architektury. Zmiany te będziemy sukcesywnie,

choć krótko, opisywać. Miały na celu głównie przyspieszenie realizacji instrukcji, a zatem

zwiększenie mocy obliczeniowej procesora.

–

–

–

Procesor 80386 może pracować w trzech trybach pracy:

trybie rzeczywistym,

chronionym trybie wirtualnym,

trybie zadań wirtualnych 8086.

Tryb rzeczywisty procesora 80386 jest taki sam jak tryb rzeczywisty procesora 80286.

Chroniony tryb wirtualny oferuje podobne, aczkolwiek ulepszone i rozszerzone

możliwości jak procesor 80286. W trybie tym, w porównaniu do procesora 286, zwiększona

jest przestrzeń pamięci wirtualnej przydzielona jednemu zadaniu i wynosi 64 TB. Ponadto,

oprócz mechanizmu segmentacji w trybie tym dostępny jest także mechanizm stronicowania.

Tak jak poprzednio, mamy do dyspozycji mechanizmy wspomagające pracę wielozadaniową

i ochronę zasobów.

Tryb zadań wirtualnych 8086 jest trybem nowym, który pojawił się dopiero

w procesorze 80386. Tworzy środowisko do wykonywania zadań przygotowanych dla

procesora 8086 w wielozadaniowym środowisku trybu chronionego procesora 80386. Zadania

procesora 8086 mogą więc być wykonywane przez procesor 80386 w dwóch trybach:

rzeczywistym i wirtualnych zadań 8086. Różnica polega na tym, że w trybie rzeczywistym

wykonujemy jedno zadanie, podczas gdy tryb wirtualnych zadań 8086 można stosować do

określonych zadań wykonywanych w środowisku wielozadaniowym. Po przełączeniu się do

tego trybu w celu wykonania konkretnego zadania procesor ten zachowuje się jak 8086, lecz

po powrocie z niego pracuje dalej w trybie chronionym, umożliwiając pracę wielozadaniową.

Lista wybranych rozkazów procesora 8086

Mikroprocesory 8088 i 8086 mają dokładnie takie same listy rozkazów. Zawierają

również rozkazy typowe dla ich poprzedników 8-bitowych (jak 8080 i 8085) oraz szereg

dodatkowych jak: mnożenie i dzielenie binarne ze znakiem, bez znaku i w kodzie BCD,

operacja przesyłania i porównywania tablic (o wymiarze do 64 KB), badanie wartości

określonych bitów operandów, programowe generowanie przerwań, czy instrukcje

ułatwiające programowanie układów wieloprocesorowych.

W procesorach 8086 prawie każdy rozkaz dotyczy zarówno bajtów jak i słów

16 bitowych. Zmienne można dodawać, odejmować, przesuwać, porównywać, itp.

bezpośrednio w pamięci bez potrzeby wcześniejszego przenoszenia ich do rejestrów. Ta

właściwość w znacznym stopniu skraca program i przyspiesza jego realizację. Przetwarzanie

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

25

jest znacznie wydajniejsze w porównaniu z mikroprocesorami 8-bitowymi. Długość rozkazu

może wynosić od 1 do 6 bajtów. Rozkaz może być bezargumentowy, jedno lub dwu

argumentowy, ale tylko jeden z argumentów może być pobrany z pamięci operacyjnej.

Rozkazy można podzielić na kilka grup pod względem rodzaju i sposobów działania:

Rozkazy transmisji danych

Kierunek Rejestry – Pamięć:

MOV

– prześlij bajt lub słowo,

PUSH – prześlij słowo na szczyt stosu,

POP

– pobierz słowo ze szczytu stosu,

XCHG – zamień miejscami bajty lub słowa,

XLAT – pobierz bajt z tablicy.

Kierunek-układy WE/WY:

IN

– pobierz bajt lub słowo z (portu) rejestru wejściowego,

OUT

– prześlij port lub słowo do (portu) rejestru wyjściowego.

Ładowanie adresów

LEA

– załaduj adres efektywny,

LDS

– załaduj adres logiczny do wskazanego rejestru i DS,

LES

– załaduj adres logiczny do wskazanego rejestru i ES.

Rejestr znaczników:

LAHF – prześlij wskazany bajt słowa znaczników do rejestru AH,

SAHF – prześlij zawartość rejestru AH do rejestru znaczników,

PUSHF – prześlij zawartość rejestru wskaźników na stos,

POPF

– pobierz dane ze stosu i prześlij do rejestru wskaźników.

Rozkazy arytmetyczne i logiczne

Dodawanie

ADD

– dodawanie bajtów lub słów 16-bitowych,

ADC

– dodawanie bajtów lub słów 16-bitowych z uwzględnieniem przeniesienia,

INC

– dodaj 1 do baj tu lub słowa,

AAA

– poprawka dla dodawania w rozpakowanym kodzie BCD,

DAA

– poprawka dziesiętna dla dodawania w kodzie BCD.

Odejmowanie

SUB

– odejmowanie bajtów lub słów 16-bitowych,

SBB

– odejmowanie bajtów lub słów 16-bitowych z uwzględnieniem pożyczki,

DEC

– odejmij 1 od bajtu lub słowa,

NEG

– zaneguj lub dopełnij do 2 bajt lub słowo,

CMP

– porównaj bajt lub słowo z innym operandem,

AAS

– poprawka po odejmowaniu w rozpakowanym kodzie BCD,

DAS

– poprawka dziesiętna po odejmowaniu w kodzie BCD.

Mnożenie

MUL

– mnożenie bajtów lub słów 16-bitowych, bez uwzględnienia znaku,

IMUL – mnożenie bajtów lub słów 16-bitowych z uwzględnieniem znaku,

AAM

– poprawka po mnożeniu w rozpakowanym kodzie BCD.

Dzielenie

DIV

– dzielenie bajtów lub słów 16-bitowych bez znaku,

IDIV

– dzielenie bajtów lub słów z uwzględnieniem znaku,

AAD

– poprawka przed dzieleniem w rozpakowanym kodzie BCD,

CBW

– zamiana bajtu na słowo,

CWD

– zamiana słowa na podwójne słowo (32-bitowe),

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

26

Grupa logiczna

NOT

– negacja (dopełnienie) bajtu lub słowa,

AND

– iloczyn logiczny bajtów lub słów,

OR

– suma logiczna bajtów lub słów,

XOR

– operacja exclusiwe-or bajtów lub słów,

TEST

– porównanie logiczne (test) bajtów lub słów.

Przesunięcia

SHL

– przesunięcie logiczne w lewo bajtu lub słowa,

SAL

– przesunięcie arytmetyczne (w kierunku bitów starszych) bajtu lub słowa,

SHR

– przesunięcie logiczne w prawo bajtu lub słowa,

SAR

– przesunięcie arytmetyczne w prawo bajtu lub słowa,

ROL

– przesunięcie cykliczne w lewo bajtu lub słowa.

ROR

– przesunięcie cykliczne w prawo bajtu lub słowa,

RCL

– przesunięcie cykliczne w lewo z bitem przeniesienia bajtu lub słowa,

RCR

– przesunięcie cykliczne w prawo z bitem przeniesienia bajtu lub słowa.

Tryby adresowania procesora 8086

Program pracy komputera jest zapisywany ciągiem wektorów binarnych

zarejestrowanych w jego pamięci. Zawiera on zbiór rozkazów wykonujących operacje na

danych binarnych. Dane do operacji są zawarte w pamięci, w rejestrach otaczających procesor

lub buforach pamięci pośredniczących, usytuowanych między procesorem i urządzeniami

WE/WY. Lokacja danych jest definiowana za pomocą określonych kombinacji wartości

zmiennych adresowych. Długość słowa adresowego określa liczbę adresowanych komórek

pamięci. Najprostsza deklaracja bieżącego adresu polega na podaniu w programie wszystkich

bitów adresowych. Taka zasada adresacji jest jednak najkosztowniejsza, zajmuje bowiem

najwięcej pamięci operacyjnej, a czas realizacji takiego programu jest najdłuższy. W celu

uproszczenia procedur adresacji wprowadzono szereg dodatkowych sposobów określania

bieżącego (fizycznego) adresu operandu.

W odniesieniu do adresowania procesora 8086 i pochodnych wyróżniono trzy

podstawowe zapisy adresów:

– adres fizyczny,

– adres logiczny,

– adres efektywny.

Adres logiczny

Adres logiczny składa się z bazy (inaczej adresu początku segmentu) zawartej w jednym

z czterech rejestrów segmentowych – CS, DS, SS i ES oraz przemieszczenia liczone go od

bazy. Schemat ideowy metody wyznaczania adresu fizycznego pokazano na rys. 22. Blok

BIU przesuwa wektor adresowy bazy o cztery bity w kierunku pozycji starszych i dodaje do

niego 16-bitowy wektor przemieszczenia. Następne adresy wylicza się na podstawie adresów

poprzednich operandu i modyfikatorów adresów. Modyfikator jest zawarty w określonym

rejestrze procesora lub w komórce pamięci. Przez umiejętne korzystanie z dostępnych trybów

adresacji można uzyskać znaczny wzrost efektywności obliczeń komputera.

Adres fizyczny

Adres fizyczny określa stan 20-bitowego wektora zewnętrznego, lokalizującego 1 MB

komórek pamięci, od 00000 H do FFFFF H. Pisząc program w języku maszynowym,

programista używa pojęcia adresu logicznego, operując krótszym formatem adresu. Jeśli to jest

16-bitowy adres będziemy dodawać cztery bity na najstarszych pozycjach (od bitu 16 do 19.)

w przedziale wartości od OH do FH, będziemy adresować 16 segmentów po 64 KB każdy.

Tego typu organizacja adresów została przyjęta w procesorach 8086 firmy Intel.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

27

Rys. 22. Wyznaczanie 20-bitowego adresu fizycznego [7]

Adres efektywny

W literaturze często spotyka się również termin adres efektywny, który jest wartością

przemieszczenia (offset) wskazującego położenie komórki pamięci w bieżącym segmencie,

licząc od początku segmentu.

Tryby adresowania

Dlatego żeby zwiększyć wydajność sposobów programowania procesorów istnieje kilka

trybów programowania, które stosowane są w zależności od wymaganej efektywności. W tym

miejscu skupimy się tylko na tych podstawowych.

Adresowanie bezpośrednie

Adresowanie bezpośrednie (ang. direct addressinig) polega na podaniu pełnego adresu

operanda bezpośrednio w programie. Ten adres jest bezpośrednim identyfikatorem lokacji

komórki pamięci lub rejestru komputera.

Na rysunku 23 podano przykład przekazywania danych między wybranymi rejestrami

wewnętrznymi procesora; z pary BX do akumulatora 16-bitowego AX. Adresy operandów są

zapisane w kodzie rozkazu przesyłu danych. Rysunek a) przedstawia stan rejestrów przed

a rysunek b) po operacji.

Rys. 23. Przykład adresacji bezpośredniej, dla przekazywania danych z rejestru do rejestru [7]

Na następnym rysunku przedstawiono inny przykład adresacji bezpośredniej dla

przekazywania danych z komórki pamięci wskazywanej przez adres adr do podanego

w rozkazie rejestru akumulatorowego.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

28

Do rejestru AX wpisane zostają dwa kolejne bajty słowa 16-bitowego, zapisane

w pamięci według kolejności: młodszy a następnie starszy bajt słowa PAO (Pamięci

Operacyjnej).

Rys. 24. Przykład transferu danych z pamięci (PAO) komputera do wskazanego rejestru (AX) z adresacją

bezpośrednią (adr) [7]

Adresowanie pośrednie

Adresowanie pośrednie (ang. indirect addressing) polega na wskazywaniu lokalizacji

operandu za pomocą zawartości określonego rejestru procesora lub komórki pamięci

operacyjnej (PAO). Procesor dokonuje automatycznej zmiany zawartości tego

rejestru/komórki pamięci (ang. increment lub decrement) po wykonaniu operacji adresacji.

MOV AX,[BX] ; wartość BX jest 16-bitowym adresem: 42, 43.

Rys. 25. Przykład adresacji pośredniej zawartością [BX] wskazanego rejestru wewnętrznego mikroprocesora [7]

Do tej grupy zaliczyć można również adresowanie stosu pamięci; zawartością

specjalnego rejestru zwanego wskaźnikiem stosu (ang. SP – Stack Pointer).

Adresowanie względne

Adres względny (ang. relative address) obliczamy względem adresu początku strony (sekcji)

przez dodanie do niego zawartości określonego rejestru wewnętrznego procesora. Jest to tzw.

przemieszczenie adresowe (ang. DISP – Displacement lub Offset). Przemieszczenie dotyczy

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

29

adresu wewnątrz strony – od adresu bazy o określaną liczbę komórek pamięci. Na rys. 26 jest

podany przykład adresacji względnej zawartością rejestru BX z przemieszczeniem 2.

Rys. 26. Przykład adresacji względnej, zawartością rejestru bazowego BX z przemieszczeniem 2 [7]

Operacja: MOV AX,[BX] + 2 oznacza wpisanie do rejestru AX zawartości komórki

pamięci wskazywanej przez zawartość rejestru BX – bazy i przemieszczenia o 2 komórki

pamięci (Offset = 2) oraz kolejnego bajtu w pamięci. Dane są czytane z pamięci w kolejności

młodszy bajt a następnie starszy bajt i w takiej kolejności wpisywane w odpowiednie części

rejestru AX.

Adresowanie natychmiastowe

Zapis danych w komórce pamięci następującej po lokacji kodu operacji nazywa się

adresowaniem natychmiastowym (ang. immediate addressing). Co oznacza, że w polu

operandu występującym po kodzie operacji zapisane są dane dla tej operacji. Przykład

adresowania natychmiastowego przedstawiono na rys. 27.

Rys. 27. Przykład adresacji natychmiastowej (względnej z zawartością IP z przemieszczeniem 0) [7]

Przykład ten można również uznać za szczególny przypadek adresacji względnej

z adresem bazy zawartym we wskaźniku rozkazów (IP) z przemieszczeniem 0.

Adresowanie indeksowane

Adres indeksowany (ang. indexed address) obliczamy jako sumę podanego w rozkazie

adresu i zawartości rejestru indeksowego [SI], np: MOV AX, adr[SI] oznacza wpisanie do

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

30

rejestru AX zawartości komórki pamięci adresowanej sumą adresu adr i zawartości rejestru

indeksowego [SI]. Etykieta (adr=41H) + [SI] określa 16-bitowy adres: 44,45. Na rysunku

poniżej przedstawiono przykład adresacji indeksowanej z indeksem [SI]=3 dla przekazywania

danych z dwóch komórek pamięci o adresach 44H i 45H do 16-bitowego rejestru

wewnętrznego procesora, AX.

Rys. 28. Przykład adresacji indeksowanej dla transferu danych z pamięci do rejestru procesora [7]

Oprócz wymienionych poprzednio czterech podstawowych trybów adresacji spotykamy

różne kombinacje tych technik. Na przykład w mikroprocesorach firmy Intel można spotkać

kombinację adresacji pośredniej z indeksowaną. W tym celu procesor wyposażono

w specjalny rejestr bazowy BP (ang. Base Pointer) – wskaźnik bazy.

Operacja: MOV AX, [BP][SI] oznacza wpisanie do rejestru AX zawartości dwóch komórek

pamięci o adresach określanych sumą zawartości rejestru BP - adresu bazowego i rejestru SI –

indeksu przemieszczenia. Przykład na rys. 29 ilustruje zasady realizacji operacji

przemieszczenia danych, z pamięci operacyjnej do rejestru AX, z adresowaniem pośrednim

indeksowanym.

Rys. 29. Przykład adresacji pośredniej indeksowanej [7]

Aby zaprogramować układ procesorowy należy skorzystać z dwóch narzędzi

programistycznych. Jedno z nich to TAsm lub jego inny odpowiednik funkcjonalny. Jest to

rodzaj kompilatora, który ze zwykłego pliku tekstowego z rozszerzeniem *.asm generuje plik

z rozszerzeniem *.obj będącego produktem wejściowym dla konsolidatora TLink. Ten z kolei

generuje wynikowy z rozszerzeniem *.exe lub *.com w zależności od ustawienia sposobu

linkowania pliku.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

31

Powyższe darmowe narzędzia, lub ich odpowiedniki funkcjonalne, dostępne są w sieci

Internet. Niektóre komputery wymagają jeszcze obecności pliku rtm.exe w katalogu

z obrabianym plikiem. Ponieważ są to narzędzia działające w trybie tekstowym więc

najwygodniej jest umieścić te pliki w katalogu np. na dysku C: . przykładowa ścieżka dostępu

mogłaby wyglądać następująco C:\mój katalog\ . pierwsze próby z programowaniem

w asemblerze zalecam prowadzić mając zainstalowany system operacyjny Windows 98, gdzie

system DOS nie jest implementowany softwarowo (jak ma to miejsce w Windows XP).

Nowsze systemy operacyjne Microsoft wymagają dodatkowych bibliotek systemowych,

o które będzie dopominać się kompilator w swoich raportach o błędach.

Rys. 30. Ścieżka dostępu do plików

Zawartość katalogu roboczego musi zawierać pliki jak na poniższym slajdzie.

Na wszelki wypadek należy dołączyć plik rtm.exe.

Rys. 31. Zawartość katalogu

W pliku przyklad.txt piszemy kod programu w asemblerze. Następnie zapisujemy plik

z rozszerzeniem *.asm.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

32

Rys. 32. Przykładowy program w asemblerze

Następnym krokiem jest wywołanie wiersza poleceń i przeprowadzenie operacji

przekształcenia pliku poleceniem

tasm przyklad.asm

Rys. 33. Pierwsza faza kompilacji

Kompilator pokazuje informacje o ewentualnych błędach kompilacji i wielkości

zajętej pamięci operacyjnej.

Następnym narzędziem, którego należy użyć jest konsolidator generujący plik *.exe

lub *.com. Jego zadaniem jest przekształcenie plików wynikowych w pliki wykonywalne.

Rys. 34. Tworzenie pliku wykonywalnego

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

33

Wynikiem działania polecenia zostanie wygenerowany plik wykonywalny.

Jeszcze jednym narzędziem, który bardzo ułatwia pracę jest Turbo Debugger znany

pod nazwą TD.exe. Pozwala on na krokowe wykonywanie programu oraz analizę jego kodu

źródłowego, zawartości rejestrów i pamięci.

Rys. 35. Ekran debugera

4.2.2. Pytania sprawdzające

1.

2.

3.

4.

5.

6.

7.

Odpowiadając na pytania, sprawdzisz, czy jesteś przygotowany do wykonania ćwiczeń.

Jakie są zadania procesora w układzie?

Z jakich bloków funkcjonalnych składa się procesor?

Czy wiesz co oznacza pojęcie rejestru procesora?

Jakie są funkcje rejestrów?

Czy wiesz co to jest tryb pracy procesora?

Czy potrafisz scharakteryzować wybrany tryb pracy procesora?

Co to jest tryb adresowania procesora?

4.2.3. Ćwiczenia

Ćwiczenie 1

Omów sposób działania wybranego modelu procesora.

Sposób wykonania ćwiczenia

1)

2)

3)

4)

Aby wykonać ćwiczenie, powinieneś:

odszukać w materiałach schemat blokowy procesora,

określić funkcje poszczególnych bloków,

dokonać analizy ich działania pod kątem pracy całości

zapisać spostrzeżenia na arkuszu papieru.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

34

−

−

Wyposażenie stanowiska pracy:

schematy blokowe procesorów,

arkusz papieru, flamastry.

Ćwiczenie 2

Scharakteryzuj przeznaczenie poznanych typów rejestrów segmentowych.

Sposób wykonania ćwiczenia

1)

2)

3)

4)

Aby wykonać ćwiczenie, powinieneś:

odszukać w materiałach opis szukanych rejestrów,

określić funkcje jakie pełnią w procesorze,

scharakteryzować do jakich celów są wykorzystywane,

zapisać spostrzeżenia na arkuszu papieru.

−

−

Wyposażenie stanowiska pracy:

schematy blokowe procesorów,

arkusz papieru, flamastry.

Ćwiczenie 3

Opisz wybrany tryb pracy procesora.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) odszukać w materiałach opis trybów pracy procesorów,

2) przeanalizować jeden tryb pracy dla wybranego procesora,

3) zapisać spostrzeżenia na arkuszu papieru.

−

Wyposażenie stanowiska pracy:

arkusz papieru, flamastry.

Ćwiczenie 4

Scharakteryzuj podstawowe operacje matematyczne operujące na 8-u bitach.

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) odszukać w materiałach opis operacji matematycznych realizowanych przez procesory,

2) wybrać te z nich, które mogą operować na słowie ośmiobitowym,

3) zapisać spostrzeżenia na arkuszu papieru.

−

Wyposażenie stanowiska pracy:

arkusz papieru, flamastry.

Ćwiczenie 5

Scharakteryzuj dowolny tryb adresowania i zaprogramuj procesor.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

35

Sposób wykonania ćwiczenia

Aby wykonać ćwiczenie, powinieneś:

1) odszukać w materiałach opisy trybów adresowania procesorów,

2) wybrać jeden z nich i określić, czym różni się od pozostałych i jakiego rodzaju komórki

pamięci uczestniczą w przesyłaniu danych w takiej operacji,

3) napisać krótki program w notatniku,

4) korzystając z programów Tasm, Link oraz TD utworzyć program wynikowy.

−

−

Wyposażenie stanowiska pracy:

arkusz papieru, flamastry,

komputer z oprogramowaniem.

4.2.4. Sprawdzian postępów

Czy potrafisz:

1)

2)

3)

4)

5)

6)

7)

8)

wyjaśnić pojęcie procesora?

wyjaśnić sposób działania procesora?

opisać bloki z których składa się procesor?

określić pojęcie rejestru procesora?

wyjaśnić do czego służą rejestry?

wyjaśnić co to jest tryb pracy procesora?

scharakteryzować wybrany tryb pracy procesora?

wyjaśnić pojęcie trybu adresowania?

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

36

Tak

Nie

4.3.

System mikroprocesorowy

4.3.1. Materiał nauczania

CPU

ROM RAM

I/O

Adres

Dane

sterowanie

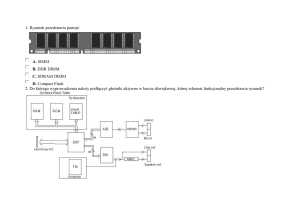

Rys. 36. Schemat blokowy systemu mikroprocesorowego [8]

−

−

−

−

−

Typowy system mikroprocesorowy składa się z następujących elementów:

mikroprocesora CPU,

pamięci stałej ROM,

pamięci operacyjnej RAM,

układów wejścia-wyjścia I/O,

układów sterujących przepływem informacji zwanymi szyną systemową, która obejmuje

m.in. magistralę danych, adresową i sterującą.

Ponieważ część tych elementów zostało omówionych poprzednio skupimy się tylko na

tych ostatnich.

Układy wejścia-wyjścia.

Urządzeniami peryferyjnymi komputera nazywamy urządzenia zapewniające jego

komunikację z otoczeniem bądź jego urządzenia wykonawcze. Nazwa urządzenia peryferyjne

może być nieco myląca, gdyż sugeruje umieszczenie tych urządzeń poza komputerem, co nie

zawsze jest prawdą (przykład: stacje dysków). Urządzenia peryferyjne nie komunikują się

z systemem bezpośrednio, lecz za pomocą specjalnych układów zwanych interfejsem bądź

kontrolerami tych urządzeń. Z punktu widzenia systemu układy te stanowią układy

wejścia/wyjścia.

Typowymi urządzeniami wejściowymi są: klawiatura, mysz,

Urządzenia wyjściowe to np.: drukarka, monitor, ploter.

Urządzenia, w przypadku których transmisja danych przebiega w obu kierunkach to

wszelkiego rodzaju nośniki pamięci np. dysk twardy, stacja dysków elastycznych.

Przyczyny, dla których układy wejścia/wyjścia muszą istnieć, są następujące:

format informacji dostarczanej przez system jest różny od formatu informacji urządzenia

peryferyjnego,

− parametry elektryczne sygnałów w systemie i urządzeniu peryferyjnym są różne,

− występuje różnica w szybkości transmisji informacji.

Wiadomą rzeczą jest fakt, iż wszystkie procesy zachodzące w komputerze są wynikiem

wykonywania pewnego programu. Innymi słowy, do poprawnej pracy komputera potrzebny

−

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

37

jest zarówno sprzęt (ang. hardware), jak i oprogramowanie (ang. software). Dotyczy to

oczywiście także obsługi urządzeń peryferyjnych. Sprzętem są tu układy wejścia/wyjścia lub

inaczej interfejs danego urządzenia. Oprogramowaniem są tak zwane sterowniki programowe

(ang. driver) czyli oprogramowanie niezbędne do poprawnej pracy danego urządzenia

peryferyjnego. Każde urządzenie peryferyjne musi korzystać z określonego układu

wejścia/wyjścia. Nie oznacza to jednak, że układ taki zawsze znajduje się na karcie

montowanej w gnieździe rozszerzającym. Rozwiązanie takie zapewnia większą elastyczność

budowy komputera, lecz nie jest konieczne. Interfejsy najbardziej popularne umieszcza się

bezpośrednio na płycie głównej. Przykładami mogą być: sterownik klawiatury, porty

szeregowe (RS 232C), równoległe czy też interfejsy dysków elastycznych lub dysków

twardych (na przykład EIDE, SATA).

W celu zapewnienia współpracy układów wejścia/wyjścia z systemem wymagane są

pewne zasoby systemu. Należą do nich: adresy w przestrzeni adresowej pamięci, adresy

w przestrzeni adresowej układów wejścia/wyjścia, sygnały zgłoszeń przerwań.

Część urządzeń peryferyjnych komunikuje się z systemem wykorzystując tzw.

mechanizm przerwań. Działanie to polega na tym, że mikroprocesor przerywa wykonywanie

swojego bieżącego programu i zaczyna wykonywać podprogram obsługi przerwania

np. wypisuje na ekranie monitora ciąg znaków, po czym wraca do przerwanej pracy.

Magistrala standardowa

W czasie pracy komputera wykorzystywane są urządzenia peryferyjne do wprowadzania

i wyprowadzania informacji. Mimo dużej różnorodności tych urządzeń, techniki realizacji

podłączeń peryferii z jednostką centralną zostały znormalizowane i zapisane jako standard

międzynarodowy.

Na rysunku przedstawiony został schemat blokowy komputera wyróżniający podstawowe

układy, magistrale i złącza biorące udział w procesach wymiany informacji między jednostką

centralną pamięcią operacyjną i urządzeniami zewnętrznymi (peryferyjnymi). Złącza

standardowe są montowane zwykle na karcie głównej komputera. Takie gniazda nazywa się

popularnie slotem. Umożliwiają one rozbudowę komputera o dodatkowe układy korzystające

z sygnałów standardowych, pozwalających na bezpośrednią komunikację z procesorem. Są to

linie adresowe, linie danych oraz linie sygnałów sterujących.

Urządzenia zewnętrzne wykonują zadania określone przez użytkownika systemu, jak:

prezentacja informacji na monitorze ekranowym, czy zapis/odczyt informacji na/z dysku. Na

drodze sygnału zewnętrznego (bezpośredniego kontaktu z użytkownikiem) do procesora,

mają miejsce operacje przetwarzania formatu informacji przyjmowanej z urządzenia

wejściowego na standard wewnętrzny komputera lub odwrotnie - ze standardu wewnętrznego

komputera na lokalny format, właściwy dla urządzenia zewnętrznego. Układy odpowiedzialne

za realizację opisanych wyżej operacji zawarto w dwóch blokach: bloku konwersji sygnałów

standardowych karty głównej komputera na standard lokalny urządzenia peryferyjnego oraz

bloku konwersji standardu lokalnego na format zapisu lub prezentacji formacji

charakterystyczne dla urządzenia WE/WY.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

38

Rys. 37. Zasady podłączeń urządzeń peryferyjnych do jednostki centralnej komputera [8]

Oba te układy zostają połączone ze sobą za pomocą złącza lokalnego we/wy. Pośrednie

złącze lokalne zastosowano z myślą o daleko idącej specjalizacji firm produkujących same

urządzenia peryferyjne bądź same układy elektroniczne. Firmy najczęściej realizują je na

podstawie własnych rozwiązań technicznych, zgodnych jedynie z lokalnymi standardami

urządzenia peryferyjnego komputera, na poziomie styku układów. Wyróżnione wyżej układy

mogą być połączone w jeden blok sprzęgający wejściowo/wyjściowy.

Magistrala adresowa i magistrala danych procesora

W procesorze 8086 zastosowano tylko jedną zewnętrzną szynę WE/WY na której,

w określonym czasie (time shared bus), wystawiany jest adres i przesyłane są dane do

i z procesora. W celu określenia miejsca przechowywania informacji procesor musi być

wyposażony w dodatkowe układy zewnętrzne. W układach zewnętrznych procesora

zapamiętane zostają wartości wektorów adresowych i wektory danych. Na rysunku pokazano

schemat połączeń procesora z elementami jego najbliższego otoczenia.

Sygnałem zatrzasku adresów ALE (ang. Address Latch Enable) zostaje zapisany wektor

adresowy w bloku rejestrów 8282 (ang. Latch) taktowany sygnałem STB. Natomiast blok

8286 spełnia funkcję dwukierunkowego, trójstanowego wzmacniacza, zwiększającego

obciążalność linii danych.

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

39

Rys. 38. Schemat organizacji połączeń zewnętrznych dla magistral procesora 8086/8088 [5]

W urządzeniach komputerowych stosuje się bloki pamięci, operujące standardowo bajtem

danych. Czytanie danych 16-bitową magistralą jest realizowane przez równoległe połączenie

dwóch modułów (banków) pamięci. Sygnał selekcji CS (ang. Chip select) modułów pamięci

otwiera drogę transmisji dla danych transmitowanych w kierunku określonym za pomocą

sygnałów RD i WR, odpowiednio: do lub z procesora. Jeśli sygnał CS jest aktywny jednocześnie

na obu modułach RAM, na magistrali danych pojawi się 16-bitowy wektor informacji.

W układzie pokazanym powyżej jednoczesną selekcję dwóch banków pamięci zrealizowano za

pomocą linii adresowej A0 (bajt młodszy) i sygnału sterującego BHE (dostęp do bajtu starszego).

W trakcie realizacji rozkazów komunikacji z pamięcią sygnał BHE = L (niski poziom

logiczny). Niska wartość na linii adresowej A0 oznacza podłączenie obu banków RAM

Operacje magistrali i sygnały sterujące

Rys. 39. Podstawowy cykl czasowy dla magistrali zewnętrznej [5]

„Projekt współfinansowany ze środków Europejskiego Funduszu Społecznego”

40

W cyklu zegarowym T1 układ sprzęgający magistrali (BIU) ustawia wartości adresów na

liniach magistrali zewnętrznej procesora - od ADO do AD 15 i od Al6 do A19 (dla procesora

8086). W T2 układ sprzęgający przełącza magistralę na bufory (BUFOR) transmisji danych

dla operacji czytania (RD) lub na linie odczytu danych dla operacji pisania (WR). W cyklach

T3 i T4 jest realizowana operacja przesyłu danych z procesora lub do procesora.

Stan oczekiwania na dane Tw jest wprowadzany między T3 i T4, gdy sygnał Ready jest

niski. Cykl obsługi magistrali zewnętrznej jest powtarzany przez układ sprzęgający magistrali

(BIU) w dwóch przypadkach:

− na żądanie układu wykonawczego EU, gdy komunikacja z otoczeniem jest częścią

rozkazu,

− gdy kolejka rozkazów nie jest do końca zapełniona.

Oprócz linii adresowych i linii danych procesor przyjmuje i wysyła sygnały sterujące

iinformacyjne. Linie: od A16/S3 do A19/S6 w cyklu Tj określają cztery najbardziej znaczące

bity adresowe, ale w cyklach T2, T3, Tw i T4 są to cztery starsze bity (S3 do S6) słowa

statusowego mikroprocesora.

S3 i S4 – określają stan aktywności rejestrów segmentowych aktualnie wykorzystywanych do

adresowania:

00 – gdy aktywny jest rejestr ES.

01 – gdy aktywny jest rejestr CS lub nie został użyty żaden z rejestrów (dla cykli

WE/WY i potwierdzenia przerwania),

10 – gdy aktywny jest rejestr SS,

11 – gdy aktywny jest rejestr DS.

S5=IF Przyjmuje wartość bitu flagowego przerwań.

S6= 0 Wartość stała zero.

BHE/S7 – jest sygnałem selekcji starszego bajtu danych (rys. 38) z banku pamięci w takcie

Ti, dla operacji zapisu, odczytu i potwierdzenia przerwania. W taktach T2, T3 i T4 wartość tej

zmiennej reprezentuje bit S7 statusu procesora. S7 wraz z dwoma innymi sygnałami koduje

osiem cykli maszynowych, pokazanych na rys. 39.

RD i WR – to wyjściowe sygnały trójstanowe, które taktują operacje czytania i pisania

danych niską wartością logiczną w taktach zegarowych T2–T4.

READY – jest sygnałem gotowości (wartość wysoka) pamięci lub układu WE/WY do

transferu danych. Wartość niska oznacza przejście procesora w stan oczekiwania

INTR – jest wejściowym sygnałem żądania przerwania maskowanego, z aktywnym

poziomem wysokim.

NMI – jest sygnałem żądania przerwania niemaskowalnego aktywizowany narastającym

zboczem tego sygnału.

TEST –jest sygnałem wejściowym, który umożliwia zatrzymanie pracy procesora. Poziom

wysoki (nieaktywny) na tym przewodzie oznacza zatrzymanie procesora. Poziom niski (co

najmniej przez sześć taktów zegarowych) oznacza kontynuowanie programu. TEST jest

synchronizowany narastającym zboczem impulsu CLK.

RESET – jest sygnałem wejściowym zerowania procesora.

M/IO – jest sygnałem wyróżniającym cykl współpracy z pamięcią (poziom wysoki) od cyklu

współpracy z portami WE/WY (poziom niski).