Krystyna Maria Noga

LABORATORIUM PODSTAW

TECHNIKI CYFROWEJ

Gdynia 2005

RECENZENT: dr inż. Jerzy KRUPA

REDAKCJA: Marta GRZYBOWSKA

KOREKTA: Bożena SOBOLEWSKA

Wydawca:

Akademia Morska w Gdyni

Wydział Elektryczny – studia zaoczne

ISBN 83-87875-42-2 dla wydania trzeciego

ISBN

dla wydania czwartego

Wersja elektroniczna

Wydawca zastrzega sobie wszelkie prawa autorskie i wydawnicze

Akademia Morska, Dział Wydawnictw

ul. Morska 81-87, 81-225 Gdynia, tel. 690-12-78

Wydanie czwarte, poprawione

maj 2005

2

SPIS TREŚCI

Strona

Wstęp ................................................................................................

4

1. Modułowy zestaw elementów logicznych UNILOG ...................

6

2. Bramki TTL i synteza układów kombinacyjnych .......................

16

3. Bloki komutacyjne .......................................................................

51

4. Bloki arytmetyczne .....................................................................

66

5. Przerzutniki bistabilne ..................................................................

82

6. Synteza układów sekwencyjnych ...............................................

100

7. Liczniki i rejestry scalone ............................................................ 116

8. Układy uzależnień czasowych ..................................................... 135

9. Podstawowe bramki, generatory astabilne

i monostabilne C-MOS ............................................................... 149

10. Klucze dwukierunkowe, multipleksery,

demultipleksery CMOS ................................................................ 166

11. Cyfrowy układ sterowania pracą windy ładunkowej ................... 182

Załączniki ........................................................................................... 208

3

WSTĘP

Skrypt niniejszy obejmuje tematy ćwiczeń laboratoryjnych z podstaw techniki cyfrowej. Dotyczą one badania podstawowych układów

kombinacyjnych, sekwencyjnych i uzależnień czasowych. Zakres i

tematyka ćwiczeń zostały dostosowane do programu studiów specjalności elektroautomatyka okrętowa i komputerowe systemy sterowania

na Wydziale Elektrycznym Akademii Morskiej w Gdyni na studiach

dziennych i zaocznych. Skrypt można również traktować jako pomoc

dydaktyczną w czasie wykładu i ćwiczeń tablicowych z przedmiotu

podstawy techniki cyfrowej.

Układ poszczególnych ćwiczeń jest podobny - po części teoretycznej, mającej na celu wyjaśnienie pojęć niezbędnych do zrozumienia ćwiczenia, znajduje się opis jego przebiegu i instrukcja wskazująca, jakie badanie należy wykonać w laboratorium i jaka powinna być

zawartość sprawozdania. Podano także zagadnienia do samodzielnego opracowania przez studentów. Po każdym ćwiczeniu zamieszczono spis najpopularniejszych pozycji literatury związanych z daną

tematyką.

Część ćwiczeń realizowana jest za pomocą modułowych zestawów elementów logicznych UNILOG-2, w które wyposażone jest laboratorium. Dlatego w początkowej części skryptu zawarto skrócony

opis zestawu UNILOG-2 oraz podano charakterystykę wykorzystywanego w ćwiczeniach analizatora sygnałów TTL. Ponadto część ćwiczeń może być realizowana w środowisku Electronics Workbench

oraz Multisim 2001. Na stronie internetowej -www.am.gdynia.pl\~jagat

dostępnych jest sporo gotowych projektów, które powinny ułatwić zrozumienie zasad projektowania układów cyfrowych w środowisku wirtualnym.

Wyrażam podziękowanie mojemu dyplomantowi, G. Przytarskiemu, za przygotowanie programu omówionego w rozdziale 2.3.

Czytelników tego skryptu proszę o zgłaszanie ewentualnych

uwag.

Autorka

4

Uwaga – dotyczy wszystkich ćwiczeń laboratoryjnych

przed wykonaniem niektórych ćwiczeń laboratoryjnych należy przygotować w domu własne projekty (w Internecie, na stronie www.

am.gdynia.pl\~jagat, przedstawiłam przykładowe projekty oraz szablony do niektórych ćwiczeń laboratoryjnych). Można skorzystać z

przedstawionych w niniejszym skrypcie propozycji tematów, można

też zrealizować inny, związany tematycznie, projekt.

W sprawozdaniu należy umieścić własny projekt, wzorcowych,

przedstawionych w Internecie, proszę nie umieszczać.

Wykaz zadań, które należy zrealizować w czasie zajęć laboratoryjnych należy ustalić z prowadzącym zajęcia (w niniejszym

skrypcie podano przykładowe propozycje).

Na potrzeby zajęć audytoryjnych, tablicowych oraz laboratoryjnych z Techniki Cyfrowej zapraszam na strony Internetowe

http://www. am.gdynia.pl\~jagat,

http://rafa.am.gdynia.pl\~czarny,

http://rafa.am.gdynia.pl\~anacz

5

1.

MODUŁOWY ZESTAW ELEMENTÓW LOGICZNYCH

UNILOG

1.1. OGÓLNA CHARAKTERYSTYKA ZESTAWU

Zestaw elementów logicznych UNILOG-2 jest urządzeniem przenośnym. Obudowa wykonana w formie walizki zawiera pole operacyjne mieszczące 12 wymiennych modułów logicznych oraz 3 niewymienne panele techniczne: zasilacz, panel przełączników i wskaźników diodowych oraz panel generatora. Płytę czołową zestawu

przedstawiono na rysunku 1.1.

CLOCK

WYMIENNE

MODUŁY

PULSE

PROBE

5V DC

MAINS

DISPLAY

OSCILLOSCOPE

DISPLAY

REGISTER

SWICH

REGISTER

Rys.1.1. Płyta czołowa zestawu UNILOG-2

Każdy moduł logiczny zawiera jeden układ scalony TTL lub

C-MOS. Wyprowadzenia układu logicznego są połączone z końcówkami umieszczonymi na płycie czołowej modułu i wkomponowanymi

w topografię wyprowadzeń układu naniesioną na tę płytę.

W środku pola operacyjnego znajduje się listwa zasilająca, na

której umieszczono końcówki ze stałymi poziomami logicznymi,

oznaczone literą H, oraz końcówki zasilania, oznaczone symbolami

+5 V i 0 V. Moduł logiczny jest zasilany poprzez połączenie końcó-

6

wek na jego płycie, oznaczonych symbolami +5 V lub U cc i 0 V lub

GND, z odpowiednimi końcówkami na listwie zasilającej.

Wartościom logicznym 0 i 1 są w zestawie UNILOGU-2 przyporządkowane poziomy logiczne L i H. Niski poziom logiczny L, któremu odpowiada w technice TTL napięcie wejściowe od 0 do +0,8 V

oraz napięcie wyjściowe od 0 do +0,4 V, jest przyporządkowany wartości logicznej 0. Wysoki poziom logiczny H, któremu odpowiada w

technice TTL napięcie wejściowe od +2,0 do +5,0 V oraz napięcie

wyjściowe od +2,4 do 5,0 V, jest przyporządkowany wartości logicznej 1. Założenia te są słuszne dla tzw. logiki dodatniej.

Do budowy połączeń pomiędzy modułami logicznymi oraz między modułami i panelami technicznymi służą specjalne przewody

połączeniowe o różnej długości wchodzące w skład zestawu. Wykonując połączenia, należy zwracać uwagę, aby wyjścia bramek, przerzutników i innych układów logicznych były łączone tylko z wejściami układów logicznych. Połączenie wyjścia z wyjściem lub wyjścia z

zasilaniem +5 V jest niedozwolone i może doprowadzić do zniszczenia układu scalonego.

Każde wejście układu logicznego stanowi pewne obciążenie dla

wyjścia, które nim steruje. Wielkością określającą obciążenie wnoszone przez wejście układu jest współczynnik obciążalności wejścia.

Na przykład każde wejście prostej bramki logicznej ma współczynnik

obciążalności równy 1, wejścia ustawiające S (oznaczane również

jako Pr) i zerujące R (Clear) przerzutników mają współczynnik obciążalności równy 2, wejście zegarowe T (CP, CL, C) przerzutników ma

współczynnik równy 2. Każde wyjście układu logicznego charakteryzuje się zdolnością wysterowania pewnej maksymalnej liczby układów wejściowych. Liczbę tę określa współczynnik obciążalności wyjścia. Wartości tych współczynników dostępne są w katalogach układów logicznych, a także w dokumentacji technicznej zestawu

UNILOG-2. Dokonując połączeń pomiędzy modułami logicznymi,

należy przestrzegać zasady, że suma współczynników obciążalności

wejść sterowanych z jednego wyjścia nie może być większa niż

współczynnik jego obciążalności.

7

1.2. PANEL ZASILACZA

Panel zasilacza umieszczony jest po lewej stronie pulpitu technicznego. Na płycie czołowej panelu znajduje się wyłącznik sieciowy

MAINS. Zestaw zasilany jest napięciem przemiennym 220 V, 50 Hz.

Podłączenie zestawu do sieci sygnalizuje wskaźnik diodowy umieszczony nad przełącznikiem. Ponadto na panelu zasilacza umieszczone

jest gniazdo PROBE 5 V DC, przeznaczone do podłączenia analizatora

sygnałów TTL typu PSL-1, stanowiącego wyposażenie dodatkowe

zestawu.

1.3. PANEL PRZEŁĄCZNIKÓW I WSKAŹNIKÓW

Panel przełączników i wskaźników umieszczony jest w środkowej części zestawu UNILOG-2. Składa się on z dwóch części opisanych SWITCH REGISTER i DISPLAY REGISTER. W części oznaczonej SWITCH REGISTER znajduje się 8 przełączników dwustabilnych,

przeznaczonych do ręcznego ustawiania poziomów logicznych, wykorzystywanych do sterowania badanych układów. Nad każdym przełącznikiem umieszczone są dwie związane z nim końcówki wyjściowe. Na końcówce górnej, oznaczonej symbolem , występuje poziom

L, jeżeli przełącznik jest zwolniony, oraz poziom H, jeżeli przełącznik

jest wciśnięty. Na końcówce dolnej, oznaczonej symbolem , występuje poziom H, jeśli przełącznik jest zwolniony, oraz poziom L, jeśli

przełącznik jest wciśnięty. Współczynnik obciążalności każdego wyjścia wynosi 30.

W części oznaczonej DISPLAY REGISTER znajduje się 16 niezależnych wskaźników diodowych, służących do monitorowania stanów

logicznych w różnych punktach badanych układów. Dioda emituje

światło, jeżeli na odpowiadające jej wejście podany jest poziom logiczny H, nie emituje zaś światła, jeżeli na jej wejście został podany

poziom logiczny L lub wejście jest nie podłączone. Współczynnik

obciążalności każdego wejścia wynosi 1.

8

1.4. PANEL GENERATORA

Panel generatora składa się z czterech części. W części opisanej

jako CLOCK umieszczono układ generatora ciągu impulsów, tzw.

zegar. Ma on dwa wyjścia, każde o współczynniku obciążalności 30.

generowany jest ciąg impulsów H, na

Na wyjściu oznaczonym

- ciąg impulsów L. Częstotliwość impulsów

wyjściu oznaczonym

zegara wybiera się poprzez wciśnięcie jednego z trzech przełączników

stabilnych, opisanych 1 Hz, 1 kHz i 1 MHz. Szerokość impulsów zegara równa jest połowie okresu drgań, wynikającego z wybranej częstotliwości. Znajdujące się nad przełącznikami pokrętło służy do płynnej

regulacji częstotliwości impulsów zegarowych. Umożliwia ono regulację częstotliwości od połowy wartości ustawionej za pomocą przełącznika do wartości pięciokrotnej.

W części oznaczonej PULSE umieszczone są trzy przełączniki

niestabilne, umożliwiające generację pojedynczych impulsów H na

, lub impulsów L na wyjściu dolwyjściu górnym, oznaczonym

nym, oznaczonym

. Wciśnięcie i zwolnienie przełącznika powoduje wygenerowanie dokładnie jednego impulsu. Współczynnik obciążalności każdego wyjścia wynosi 30.

W części opisanej DISPLAY znajduje się cyfrowy wskaźnik

7-segmentowy i wyprowadzone są dwa rodzaje wejść tego wskaźnika.

Wejścia oznaczone a, b, c, d, e, f, g, DP pozwalają na bezpośrednie

sterowanie segmentami. Podanie poziomu L na jedno z wejść wskaźnika powoduje emitowanie światła przez odpowiedni segment wskaźnika. Natomiast wejścia oznaczone jako 20 , 21 , 22 , 23 są wejściami

scalonego translatora kodu BCD na kod wskaźnika 7-segmentowego,

wbudowanego w panel i połączonego ze wskaźnikami.

W części opisanej OSCILLOSCOPE umieszczone są dwie pary

gniazd A i B. Ułatwiają one prowadzenie obserwacji oscyloskopowych przebiegów logicznych w badanych układach. Dwa gniazda

koncentryczne, służące do podłączenia przewodów koncentrycznych,

połączone są z dwiema końcówkami, umożliwiającymi połączenie z

oscyloskopem dwukanałowym wybranych punktów badanego układu.

9

1.5. ANALIZATOR SYGNAŁÓW TTL

Analizator sygnałów TTL typu PSL-1 wykonany jest w postaci

zwartej konstrukcji z wyprowadzonym przewodem zasilającym, zakończonym wtykiem słuchawkowym. Ponadto wyposażono go w

wymienne końcówki pomiarowe, zakończone ostrzem lub giętkim

przewodem. Ogólny widok analizatora pokazano na rysunku 1.2.

AA

przycisk

kasujący funkcji

przełącznik

funkcji

L1 L2 L3 L4

L5 L6 L7 L8 L9

A

B→

C→

←D

Rys. 1.2. Analizator sygnałów TTL typu PSL-1

Analizator zasilany jest napięciem +5 V. Napięcie zasilające należy podać na górny wtyk słuchawkowy lub na czerwoną żyłę przewodu zasilającego. Podczas badania układów zrealizowanych za pomocą zestawu UNILOG-2 najwygodniej jest wykorzystać do zasilania

analizatora znajdujące się w panelu zasilacza tego zestawu gniazdo

``PROBE 5V DC``. W wypadku niezależnego zasilania analizatora

na-leży uważać, aby nie pomylić biegunowości zasilania, gdyż ewentualna zmiana w tym zakresie prowadzi do trwałego uszkodzenia analizatora.

W przedniej części obudowy analizatora znajdują się gniazda

wejściowe A i B, na które za pośrednictwem końcówek pomiarowych

podawane są badane sygnały, oraz gniazdo C, umożliwiające podłączenie dodatkowego przewodu masy badanego układu. Z boku obudowy znajduje się przycisk kasowania R, służący do zerowania wewnętrznych rejestrów analizatora.

Na płycie czołowej analizatora umieszczono diody świecące,

sygnalizujące stan badanego układu, oraz przełącznik funkcji, sterują-

10

cy sposobem pracy wewnętrznego licznika impulsów. Poszczególne

elementy mają za zadanie sygnalizować:

• dioda świecąca L1 - wysoki poziom sygnału na wejściu A,

• dioda świecąca L2 - zarejestrowanie co najmniej jednego zbocza

opadającego na wejściu A,

• dioda świecąca L3 - niski poziom sygnału na wejściu A,

• dioda świecąca L4 - zarejestrowanie faktu, że sygnał na wejściu B

miał wysoki poziom podczas narastającego zbocza sygnału na wejściu A ( dotyczy to pierwszego po wyzerowaniu analizatora narastającego zbocza sygnału na wejściu A, a służy do rozpoznawania

wzajemnej lokalizacji czasowej impulsów w sygnałach podawanych na wejścia A i B ),

• diody świecące L5-L8 - stan licznika binarnego, który w zależności

od położenia przełącznika funkcji zlicza ilość narastających zboczy

w sygnale podawanym na wejście A lub ilość narastających zboczy

w sygnale na wejściu B w czasie trwania ramki czasowej, wyznaczonej przez dwa pierwsze (po wyzerowaniu przyciskiem R) opadające zbocza w sygnale na wejściu A,

• dioda świecąca L9 - przepełnienie licznika binarnego.

W tylnej części obudowy analizatora, obok przewodu zasilającego, umieszczone jest gniazdo wyjściowe D sygnału TTL z czwartego

bitu licznika binarnego. Daje ono możliwość podłączenia dodatkowego zewnętrznego licznika impulsów.

Zestaw UNILOGU-2 może również współpracować z analizatorem sygnałów TTL typu PSL-1A (rys. 1.3). Analizator ten umożliwia

wykrycie stanu logicznego L (zielona dioda) oraz stanu logicznego H

(dioda czerwona). Na czerwoną żyłę przewodu zasilającego należy

podać napięcie +5 V.

Rys. 1.3. Analizator sygnałów TTL typu PSL-1A

11

1.6. WYKAZ UKŁADÓW SCALONYCH I DODATKOWYCH

ELEMENTÓW DOSTĘPNYCH W LABORATORIUM

1.6.1. Moduły logiczne TTL serii UCY 74 zestawu

UNILOG

(Druga liczba, występująca po liczbie identyfikującej układ scalony,

określa liczbę modułów)

7400 - 14, 7402 - 5, 7404 - 5, 7410 - 9 7420 - 14, 7442 - 5, 7450 - 5,

7460 - 5, 7472 - 3, 7474 - 9, 7476 - 10, 7483 - 5, 7485 - 5, 7486 - 4,

7489 - 2, 7490 - 3, 7493 - 5, 7495 - 5, 74123 - 7, 74150 - 2, 74151 -7,

74154 - 2, 74155 - 7, 74181 - 5, 74192 - 5, 74193 - 5,

elementy RC - 7, podstawka 16 pin - 17, podstawka 24 pin - 10.

1.6.2. Moduły logiczne C - MOS serii 4000 zestawu

UNILOG

(Druga liczba, występująca po liczbie identyfikującej układ scalony,

określa liczbę modułów)

4000 - 2, 4007 - 2, 4008 - 1, 4011 - 2, 4012 - 2, 4013 - 2, 4019 - 1,

4024 - 1, 4027 - 2, 4028 - 1, 4029 - 2, 4035 - 2, 4040 - 1, 4042 - 1,

4047 - 2, 4044 - 3, 4050 - 2, 4051 - 2, 4059 - 2, 4066 - 2, 4511 - 4,

4724 - 1.

UWAGA: odpowiednikiem krajowym jest seria MCY 74.

1.6.3. Układy scalone TTL serii UCY 74 i C-MOS serii

MCY 74

Układy C - MOS

74000, 74001, 74002, 74011, 74012, 74013, 74016, 74022, 74023,

74028, 74028, 74047, 74049, 74051, 74052, 74053, 74066, 74069,

74071, 74072, 74077, 74081, 74093.

Układy TTL

7400, 7401, 7402, 7403, 7404, 7405, 7406, 7407, 7408, 7409, 7410,

7414, 7416, 7417, 7420, 7430, 7437, 7438, 7440, 7442, 7447, 7450,

12

7451, 7453, 7454, 7460, 7472, 7473, 7474, 7475, 7476, 7483, 7485,

7486, 7490, 7492, 7493, 7495, 74107, 74121, 74123, 74132, 74141,

74145, 74150, 74151, 74153, 74154, 74157, 74164, 74165, 74174,

74175, 74180, 74181, 74192, 74193, 74549, 74A60, 74H00, 74H10,

74HCT14, 74LS00, 74LS02, 74LS04, 74LS05, 74LS08, 74LS09,

74LS10, 74LS11, 74LS14, 74LS15, 74LS20, 74LS21, 74LS22,

74LS26, 74LS32, 74LS74, 74LS90, 74LS109, 74LS123, 74LS132,

74LS138, 74LS139, 74LS174, 74LS373, 74S00, 74S405, 74S412.

1.6.4. Elementy dodatkowe

Płytki z zestawami elementów

820 Ω, 390 Ω, 200 Ω, 110 Ω, 1µF,

4 x 200 Ω, 4 x 1 kΩ,

1 µF, 2,2 µF, 4,7 µF, 22 µF, 33 µF, 47 µF, 100 µF, 220µF, 470 µF ,

2 x BC109, 2 x BC179,

4 x BAY55, 2 x BAVP21, 2 x GD507, 2 x 1N40.

Elementy na przewodach

rezystory: 110 Ω – 1; 820 Ω – 2; 11 kΩ – 1; 15 kΩ – 3; 27 kΩ – 1;

30 kΩ – 2; 39 kΩ – 5; 51 kΩ – 2; 820 kΩ – 1;

dioda: 1N4005 – 2;

kondensatory: 100 µF – 1; 220 µF – 5; 470 µF – 2; 1000 µF – 1.

1.7. PŁYTKA LOGICZNA Z TRANSLATOREM KODU BCD

NA KOD WSKAŹNIKA 7-SEGMENTOWEGO

Wskaźnik 7-segmentowy, wchodzący w skład zestawu UNILOG2, znajdujący się w polu DISPLAY, nie zawiera następujących wejść

funkcyjnych:

• wejścia wygaszania, spełniającego również funkcję sygnalizacji

wygaszania zera BI/RBO (ang. Blanking Input/Ripple Blanking

Output),

• wejścia wygaszania zera RBI (ang. Ripple Blanking Input),

• wejścia testowego LT (ang. Lamp Test).

13

Wyświetlacz A

Vcc

+

1

2

3

4

5

6

7

R1

20

A

21

B

22

C

23

D

BI/RBO

E

RBI

F

LT

a

R2

f

R3

b

g

R4

R5

R6

e

c

R7

G

d

R8

UCY 7447

12345678

BEZPOŚREDNIE ZASILANIE

WYŚWIETLACZA A

Wyświetlacz B

1

2

3

4

5

6

7

20

A

21

B

22

C

23

D

BI/RBO

E

RBI

F

LT

R9

a

R10

R11

f

R12

b

g

R13

R14

R15

G

e

c

d

R16

UCY 7447

12345678

BEZPOŚREDNIE ZASILANIE

WYŚWIETLACZA B

Rys. 1.4. Układ sterujący wskaźnikami 7-segmentowymi o wspólnej anodzie

14

Układ sterujący wskaźnikami 7-segmentowymi o wspólnej anodzie zawierający wejścia funkcyjne przedstawiony jest na rysunku

1.4; został on wykonany w postaci dodatkowej płytki współpracującej

z zestawem UNILOG-2.

Poszczególne katody segmentów są dołączone do wyjścia układu

UCY 7447 (translator kodu BCD na kod wskaźnika 7-segmentowego

o wyjściach zanegowanych) poprzez rezystory ograniczające prąd do

wartości dopuszczalnej, jaka może płynąć przez segment.

15

2. BRAMKI TTL I SYNTEZA UKŁADÓW

KOMBINACYJNYCH

2.1. CEL ĆWICZENIA

Celem ćwiczenia jest praktyczne poznanie podstawowych układów cyfrowych, realizujących funkcje logiczne, oraz ich parametrów i

charakterystyk. Ćwiczenie umożliwia zbudowanie i przebadanie

wcześniej zaprojektowanego układu kombinacyjnego. Wykorzystuje

się tu modułowy zestaw elementów logicznych UNILOG-2 lub program dydaktyczny do badania podstawowych charakterystyk wybranych elementów półprzewodnikowych [ 8 ].

2.2. PODSTAWOWE WIADOMOŚCI TEORETYCZNE

2.2.1. Układy cyfrowe TTL

Spośród monolitycznych układów cyfrowych dużą popularność,

obok obecnie powszechnie stosowanych układów cyfrowych wykonanych w technice MOS, osiągnęły wykonane w technice bipolarnej

układy tranzystorowo-tranzystorowe TTL (ang. Transistor-Transistor

Logic).

Układy TTL są elementami dwustanowymi, których aktualny

stan można opisać wykorzystując dwuelementową algebrę Boole’a.

Wysoki poziom napięcia (logiczna 1) oznacza się literą H (ang. High),

natomiast poziom niski (logiczne 0) literą L (ang. Low ).

Stosuje się trzy podstawowe kryteria podziału cyfrowych układów

scalonych TTL:

a/ ze względu na zakres temperatur pracy oraz napięć zasilania układy

TTL dzielą się na trzy podstawowe serie, które zostały przedstawione

w tabeli 2.1,

b/ ze względu na czas propagacji i pobór mocy układy TTL dzielą się

na pięć wersji (tab. 2.2):

• układy standardowe,

16

•

•

•

•

c/

•

•

•

•

układy małej mocy strat (L), lecz o większym czasie propagacji,

układy szybkie (H), lecz o zwiększonej mocy strat,

układy superszybkie (S),

układy superszybkie (LS) małej mocy strat,

ze względu na liczbę elementów w jednej obudowie układy TTL

dzielą się na:

układy małej skali integracji (ang. SSI - Small Scale Integration)

zawierające nie więcej niż 12 bramek w jednej strukturze,

układy średniej skali integracji (ang. MSI - Medium Skale Integration) zawierające 13÷99 bramek,

układy dużej skali integracji (ang. LSI - Large Sale Integration) zawierające 100÷10 000 bramek,

układy bardzo dużej skali integracji (ang. VLSI - Very Large Scale

Integration) zawierające powyżej 10 000 bramek.

Tabela 2.1

Zakres temperatur pracy i napięć układów TTL

Napięcie

zasilania [V]

o

Seria

Zakres temperatur pracy [ C]

54

74

64

od -55 do +125

od 0 do +70

od -25 do +85

5 ±10%

5 ± 5%

5 ± 5%

Tabela 2.2

Podstawowe parametry techniczne bramek TTL serii 74

standardowa

H

Wersja

L

Czas propagacji tp [ns]

10

6

33

3

10

Częstotliwość maks. fmax [MHz]

35

50

3

125

45

Moc strat Ps [mW]

10

22

1

19

2

Obciążalność N

10

10

10

10

20

Parametry

S

LS

2.2.2. Podstawowa bramka z serii 74

Podstawowym elementem układów cyfrowych TTL jest bramka

NAND z serii 74. Jej schemat bramki przedstawiono na rysunku 2.1.

Bramka realizuje funkcję negacji iloczynu logicznego, tzn. F = AB .

17

Rys. 2.1. Schemat ideowy bramki podstawowej NAND

Sygnały wejściowe podawane są na emitery tranzystora wieloemiterowego T1, realizującego iloczyn logiczny. Tranzystor T2 pracuje w układzie wzmacniacza pośredniczącego, natomiast tranzystory

T3 i T4 stanowią przeciwsobny stopień wyjściowy (Totem - Pole).

Zapewnia on małą rezystancję wyjściową w obu stanach logicznych.

Jeżeli przynajmniej na jedno wejście bramki podany jest sygnał 0

(napięcie o poziomie L), to tranzystor T1 przewodzi prąd będąc w

stanie nasyconym, zatykając tym samym tranzystor T2. Zatkanie T2

pociąga za sobą zatkanie T4, natomiast T3 działa wtedy jako wtórnik

emiterowy, w którym rolę opornika emiterowego spełnia obciążenie

bramki. Napięcie wyjściowe odpowiada poziomowi logicznemu 1.

Jeżeli na oba wejścia bramki podane zostaną sygnały o wartości

logicznej H, wówczas złącze emiterowe tranzystora T1 jest spolaryzowane w kierunku zaporowym (obszar pracy inwersyjnej, gdzie kolektor i emiter zamieniają wzajemnie role). Tranzystor T2 zostaje wysterowany do stanu nasycenia. Spadek napięcia na kolektorze T2 powoduje zatkanie T3, natomiast T4 wchodzi w stan głębokiego nasycenia, a tym samym napięcie na jego kolektorze spada do około 0,2 V

(stan L). Przykładem układu scalonego zawierającego cztery dwuwejściowe bramki NAND jest układ UCY 7400 (SN7400).

Właściwości statyczne układów logicznych TTL można przedstawić w postaci odpowiednich charakterystyk. Podstawową charakte18

rystyką statyczną jest charakterystyka przejściowa (przełączania)

U0 = f(UI), określająca zależność napięcia wyjściowego od napięcia

wejściowego bramki. Na rysunku 2.2 pokazano charakterystykę przejściową standardowej bramki NAND.

Zależności prądowo-napięciowe układu ilustruje się za pomocą

charakterystyki wejściowej II = f(UI). Przykładową charakterystykę

wejściową standardowej bramki NAND przedstawiono na rysunku 2.3.

U0

UOH MIN

UOL MAX

[V]

4,8

4,4

4,0

3,6

3,2

2,8

2,4

2,0

1,6

1,2

0,8

0,4

0,4 0,8 1,2 1,6 2,0 2,4 2,8

UIL MAX

UIH MIN

UI

[V]

Rys. 2.2. Charakterystyka przejściowa bramki NAND

II [mA]

0,5

1

3

2

4

-1

Rys. 2.3. Charakterystyka wejściowa bramki NAND

19

UI [V]

Charakterystykę poboru prądu zasilania Icc = f(UI) bramki NAND,

określającą zależność prądu zasilania od napięcia wejściowego, przedstawiono na rysunku 2.4.

~20 mA

Icc [mA]

~13 mA

~10 mA

UI [V]

~1,5 V

Rys. 2.4. Charakterystyka poboru prądu zasilania

W celu zobrazowania możliwości obciążenia bramki podaje się

dwie charakterystyki wyjściowe U0 = f(I0) – osobno dla stanu wysokiego i niskiego na wyjściu bramki (rys. 2.5).

UOH

[V]

UOL

[V]

a)

5

0,5

4

0,4

3

0,3

2

0,2

1

0,1

5

10

15

20

25

30

IOH

[mA]

b)

10

20

30

40

50

IOL

[mA]

Rys. 2.5. Charakterystyki wyjściowe bramki NAND: a) dla stanu H na wyjściu,

b) dla stanu L na wyjściu

Oporność wyjściowa bramki w stanie 1, przy małym obciążeniu nie

po-wodującym nasycenia tranzystora T3, wynosi około 100 Ω, nato-

20

miast w stanie 0 - około 10 Ω (wyjście zachowuje się jak kolektor

nasyconego tranzystora z emiterem na masie).

W serii UCY 74 gwarantowane są następujące wartości napięć:

•

U IL max = 0,8 V, maksymalna wartość napięcia wejściowego w

stanie 0,

• U IH min = 2,0 V, minimalna wartość napięcia wejściowego w stanie 1,

• U OL max = 0,4 V, maksymalna wartość napięcia wyjściowego w

stanie 0 dla prądu wyjściowego nie przekraczającego 16 mA,

• U OH min = 2,4 V, minimalna wartość napięcia wyjściowego w stanie 1 dla prądu pobieranego mniejszego niż 400 µA.

Podane powyżej prądy obciążenia dotyczą wyłącznie wersji standardowej. Gwarantowane wartości prądów wejściowych wynoszą dla

wersji standardowej:

dla U I = 0,4 V

I ILmax = 1,6 mA

I IHmax = 1,6 µA

dla U I = 2,4 V

2.2.3. Bramka z otwartym obwodem kolektora

Bramka z wyjściem typu „Open Collector” (OC) różni się od typowych bramek tym, że w jej stopniu wyjściowym znajduje się zwykły

inwerter (rys. 2.6), a nie

układ przeciwsobny Totem

Pole, co pozwala na realizację iloczynu logicznego poprzez podłączenie kolektorów tranzystorów wyjściowych wielu bramek do

wspólnego opornika, łączącego je z napięciem zasilającym. Zrealizowany w taki

sposób iloczyn logiczny

nazywa się iloczynem monRys. 2.6. Bramka z otwartym obwodem

tażowym.

kolektora UCY 7401

21

Dwie bramki OC dołączone do wspólnego rezystora obciążającego RO (rys. 2.7) realizują funkcję: F = A B + C D = A B ⋅ C D .

UCC

R0

A

B

F = AB + CD

C

D

Rys. 2.7. Dołączenie dwu bramek z otwartym kolektorem do wspólnego rezystora

obciążającego

Projektowanie iloczynu montażowego polega na wyznaczeniu

górnej i dolnej granicznej oporności wspólnego obciążenia R0. Odbywa się to na drodze analizy rozpływu prądów bramek OC przy obu

stanach logicznych (rys. 2.8).

a)

b)

UCC

UCC

RO MIN

RO MAX

ID

ID

UIL

IOH

IIH

UIH

UIL

IOH

IIH

UIL

IIL

UIL

IOH

IIH

UIL

IIL

UIL

IOH

n

IOL

IIL

UIL

N

n

N

Rys.2.8. Rozpływ prądów w układzie iloczynu montażowego: a) w stanie H,

b) w stanie L

Maksymalna wartość rezystancji R 0 dla stanu H wynosi:

22

R 0 max =

Ucc − UOH min

n I OH max + N I IH max

gdzie:

n - liczba bramek dołączonych do wspólnego rezystora R0 ,

N - liczba wejść bramek obciążających.

W stanie L wartość R 0 można wyznaczyć na podstawie wzoru:

R 0 min =

Ucc − U OL max

I OL max − N I IL max

W związku z różnicami w budowie poszczególnych bramek z otwartym kolektorem, gwarantowane wartości parametrów stopnia końcowego precyzuje się dla każdego typu bramki oddzielnie. Na przykład

dla bramki UCY 7401 wartości te wynoszą:

dla

U OH = 5,25 V

I OH max = 250 µA

(I OH max jest odmiennie zdefiniowana niż dla układu UCY7400)

dla

I OL max = 16 mA.

U OL max = 0,4 V

Bramki z otwartym obwodem kolektora służą również do współpracy układów TTL z innymi układami pracującymi przy wyższych

napięciach zasilania, np. z wysokoprogowymi tranzystorami MOS.

Realizacja tej funkcji wymaga zastosowania w stopniu wyjściowym

tranzystora o podwyższonym napięciu przebicia (15 V lub 30 V) i

odpowiednio dużym prądzie IOL. Przykładem bramki buforowej z

otwartym obwodem kolektora jest inwerter UCY 7406.

2.2.4. Zasady stosowania układów TTL

Sygnały podawane na wejścia elementów TTL powinny charakteryzować się następującymi parametrami:

• czasy narastania i opadania impulsów zegarowych powinny być

mniejsze niż 150 ns,

• czasy narastania i opadania zboczy impulsów wejściowych powinny maleć ze wzrostem rezystancji wyjściowej układów sterujących,

23

jeżeli impedancja Z O ≥ 100 Ω, czasy te nie powinny być dłuższe

niż 1 µs,

• wejściowe poziomy napięć dodatnich nie powinny przekraczać

+5,5 V, a ujemnych -0,5 V.

Podczas stosowania układów TTL może zaistnieć sytuacja, że nie

do wszystkich wejść bramki doprowadzono sygnały sterujące. Wejście nie wykorzystane oddziałuje wtedy na wartość logiczną sygnału

wyjściowego w taki sposób, jak gdyby do tych wejść zostały doprowadzone sygnały odpowiadające jedynce logicznej. Pozostawienie nie

wykorzystanych (otwartych) wejść zmniejsza szybkość przełączania

bramki ze stanu wysokiego do niskiego, a także odporność bramki na

zakłócenia. Jeśli więc w systemach lub urządzeniach cyfrowych istnieją elementy logiczne, w których nie wszystkie wejścia są wykorzystane, to należy stosować następujące zasady ich połączenia:

• nie używane wejścia bramek AND, NAND i przerzutników należy

dołączyć do szyny napięcia zasilania U cc poprzez rezystancję

1÷5 kΩ; przez pojedynczą rezystancję 1 kΩ można dołączyć maksymalnie 25 wolnych wejść; jeżeli napięcie zasilania nie przekracza 5,5 V, to nie używane wejścia można dołączyć wprost do napięcia zasilania,

• nie używane wejścia bramek AND, NAND, OR oraz NOR można

dołączyć do wejść używanych tych samych bramek pod warunkiem, że dopuszczalna obciążalność układu sterującego w stanie

wysokim nie zostanie przekroczona,

• wolne wejścia bramek AND, NAND oraz przerzutników można

dołączyć do wyjścia nie używanej bramki, na wejście której należy

przyłożyć napięcie odpowiadające zeru logicznemu,

• wolne wejścia bramek AND, NAND oraz przerzutników można

dołączyć do niezależnego źródła napięcia zasilania o napięciu wynoszącym +2,4 ÷ +3,5 V,

• wolne wejście bramek OR oraz NOR należy dołączyć do masy;

wejście bramki można łączyć z masą układu poprzez opornik nie

większy niż 400 Ω.

24

2.2.5. Synteza układów kombinacyjnych

W celu dokonania syntezy układu kombinacyjnego należy:

• określić funkcję logiczną rozpatrywanego problemu, np. za pomocą tablicy prawdy,

• dokonać minimalizacji funkcji logicznej wykorzystując tablice

Karnaugha lub metody algebraiczne,

• sporządzić schemat układu logicznego, realizującego zminimalizowaną funkcję logiczną.

Minimalizacja funkcji logicznych polega na wielokrotnym stosowaniu tzw. reguł sklejania:

Ax + A x = A

(A + x ) (A + x) = A

Wyrażenia podlegające sklejaniu noszą nazwę sąsiednich. Są one

iloczynami lub sumami tych samych zmiennych różniących się tylko

negacją jednej zmiennej. Na przykład sąsiednie są wyrażenia

x1 x 2 x 3 i x1 x 2 x 3 oraz x 1 + x 2 + x 3 + x 4 i x1+ x2 + x 3 + x 4 ; ich

suma i iloczyn po zastosowaniu reguł sklejania wynoszą odpowiednio:

x1 x2 oraz x1 + x2 + x3 . Funkcje logiczne można minimalizować

poprzez przekształcenia algebraiczne zgodnie z prawami oraz tożsamościami algebry Boole’a. Jest to jednak sposób pracochłonny i niewygodny.

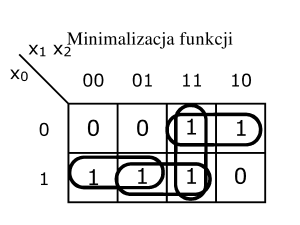

Podstawowy algorytmiczny sposób minimalizacji funkcji logicznych to metoda tablic Karnaugha. Przykładowo podano jej zastosowanie do minimalizacji względem zer i względem jedynek następującej funkcji logicznej czterech zmiennych:

f (D, C, B, A) = Σ ( 0, 1, 2, 8, 9, 11, 12, 13, 15 ) =

= DCBA + DCBA + DCBA + DCBA + DCBA + DCBA + DCBA +

+ DCBA + DCBA

W celu zminimalizowania powyższej funkcji należy przedstawić ją w

tablicy Karnaugha (rys. 2.9).

25

a)

BA 00

DC

00

1

01

0

11

1

10

1

01

11

10

1

0

1

1

0

0

1

1

1

0

0

0

b)

BA 00

DC

00

1

01

0

11

1

10

1

01

11

10

1

0

1

1

0

0

1

1

1

0

0

0

Rys.2.9. Tablice Karnaugha funkcji f ( D, C, B, A ):

a) minimalizacja względem zer, b) minimalizacja względem jedynek

Z tablicy otrzymuje się następujące minimalne postaci funkcji:

a) minimalizując względem zer:

f ( D, C, B, A ) =

(D+C)(D+B+ A )(A+B+ D)

b) minimalizując względem jedynek:

f ( D, C, B, A ) = DCA +CB+ DB+DA

Zasady sporządzania schematu logicznego zostaną omówione na podstawie kolejnego przykładu.

Przykład

Zminimalizować funkcję Y(a, b, c, d, e)= Π [0, 5, 7, 8, 10, 12, 13, 14,

16, 20, 23, 31 (3, 4, 6, 15, 18, 24, 29)] .

Zaprojektować układ kombinacyjny złożony z bramek:

a) tylko NOR 3-wejściowych,

b) tylko NAND 3-wejściowych.

Rozwiązanie

Minimalizacji dokonano wykorzystując tablice Karnaugha.

c, d, e

a, b

00

01

11

10

000

0

0

x

0

001

1

1

1

1

011

x

1

1

1

26

010

1

0

1

x

110

x

0

1

1

111

0

x

0

0

101

0

0

x

1

100

x

0

1

0

Y(a, b, c, d, e) = c e + e d a + a b e + b d e

a

c

b

d

e

Y

Rys. 2.10. Układ kombinacyjny na bramkach NOR 3-wejściowych

a

b

c

d

e

Y

Rys. 2.11. Układ kombinacyjny na bramkach NAND 3-wejściowych

27

2.3. OPIS OPROGRAMOWANIA DO BADANIA

PODSTAWOWYCH CHARAKTERYSTYK WYBRANYCH ELEMENTÓW PÓŁPRZEWODNIKOWYCH

2.3.1. Struktura programu

Uruchomienie programu do badania charakterystyk wybranych

elementów półprzewodnikowych następuje po wejściu do katalogu, w

którym znajdują się wszystkie pliki niezbędne do jego działania (sterowniki karty graficznej - pliki z rozszerzeniem BGI, zbiory krojów

pisma - pliki z rozszerzeniem CHR, pliki graficzne z rozszerzeniami

DCS i BMP znajdujące się w podkatalogu SCHEMATY, zbiory tekstowe z rozszerzeniem TXT oraz program wykonawczy MAIN.EXE)

i po uruchomieniu zbioru o nazwie MAIN.EXE.

Przygotowane w ramach pracy dyplomowej [8] oprogramowanie składa się z trzech zasadniczych części:

• MENU GŁÓWNEGO,

• WPROWADZENIA DO ĆWICZENIA,

• CZĘŚCI POMIAROWEJ.

2.3.1.1. Menu główne

Po uruchomieniu programu wyświetlana jest czołówka, z której

po naciśnięciu dowolnego klawisza przechodzimy do menu głównego.

Menu główne daje nam do wyboru następujące opcje:

• USTAWIENIA,

• DIODY,

• TRANZYSTORY,

• BRAMKI,

• POMOC.

Każda z tych opcji może być uaktywniana poprzez naciśnięcie klawisza odpowiadającego wyróżnionej literze w nazwie opcji lub poprzez

naprowadzenie podświetlonej belki za pomocą klawiszy ← , → na

odpowiednią nazwę opcji i potwierdzenie jej klawiszem Enter. Po

28

wyborze opcji następuje wyświetlenie na ekranie monitora dostępnych

podopcji.

Sposób wyboru podopcji jest taki sam, jak przy wyborze opcji, tzn.

przez naciśnięcie odpowiedniego klawisza z wyróżnioną literą lub

poprzez naprowadzenie podświetlonej belki na wybraną podopcję.

Ponadto program umożliwia szybkie poruszanie się między okienkami, np. za pomocą klawisza kierunkowego → można przejść od podopcji USUŃ SORTOWANIE w opcji USTAWIENIA do podopcji

PROSTOWNICZA w opcji DIODY. Metodę tę można także stosować dla bardziej „zagłębionych” opcji poprzez kilkakrotne naciskanie

kursora kierunkowego. Struktura MENU GŁÓWNEGO została

przedstawiona na rysunku 2.12.

Opcja USTAWIENIA

Po wyborze opcji USTAWIENIA na ekranie pojawi się okno

zawierające następujące podopcje:

• WSTAW WPROWADZENIE,

• USUŃ WPROWADZENIE,

• WSTAW SORTOWANIE,

• USUŃ SORTOWANIE.

Za pomocą podopcji WSTAW WPROWADZENIE i USUŃ

WPROWADZENIE możemy włączyć lub wyłączyć funkcję wyświetlania na ekranie monitora wprowadzenia do ćwiczenia (standardowo

wprowadzenie ustawione jest na aktywne). Stan tej podopcji sygnalizowany jest na belce narzędziowej u dołu ekranu.

Opcja DIODY i opcja TRANZYSTORY

Opcje DIODY i TRANZYSTORY przeznaczone są do wykorzystania w laboratorium podstaw elektroniki, dlatego też opis ich nie

zostanie przedstawiony.

Opcja BRAMKI

Opcja BRAMKI przygotowana została z myślą o wykorzystaniu

w laboratorium techniki cyfrowej. Umożliwia ona badanie charakterystyk następujących bramek wykonanych w technice TTL:

• NAND,

29

•

OPEN COLLECTOR.

Jeżeli uaktywnimy podopcję NAND, to rozwinie się podmenu CHARAKTERYSTYKI, w którym należy dokonać wyboru rodzaju badanej charakterystyki. W nowo otwartym oknie dostępne są następujące

charakterystyki:

•

•

•

•

POBORU PRĄDU,

PRZEŁĄCZANIA,

WEJŚCIOWA,

WYJŚCIE ESC.

UWAGA: Aby określić charakterystykę PRZEŁĄCZANIA bramki UCY 7401, powinno wybrać się ją z

podmenu CHARAKTERYSTYKI mieszczącym się w menu podopcji OPEN COLLECTOR.

Uaktywnienie wybranej funkcji podmenu CHARAKTERYSTYKI spowoduje przejście do wyświetlania na ekranie komputera wprowadzenia, czyli pomocy teoretycznej (przy standardowym ustawieniu).

Opcja POMOC

Opcja POMOC powoduje wyświetlenie na ekranie monitora

podstawowych informacji o sposobie korzystania z programu do rejestracji charakterystyk wybranych elementów półprzewodnikowych.

Zawiera ona następujące elementy składowe:

• opis ogólny programu,

• podstawowe zasady dokonywania pomiarów za pomocą programu,

• podstawowe błędy przy obsłudze programu,

• nowości,

• info.

Do przeglądania pomocy służą klawisze:

- przesuw o jeden wiersz w górę,

↑

- przesuw o jeden wiersz w dół,

↓

Pg Up - przesuw o jeden ekran w górę,

Pg Dn - przesuw o jeden ekran w dół.

30

Ustawienia

Diody

Tranzystory

Wstaw wprowadzenie

Usuń wprowadzenie

Wstaw sortowanie

Usuń sortowanie

Wyjście

Esc

Prostownicza

Zenera

Wyjście

Esc

Bipolarne

Polowe

Wyjście

Przewodzenia

Zaporowa

Wyjście

Esc

Przejściowa

Wyjściowa

Wyjście

Esc

Esc

Bramki

Nand

Open Collector

Wyjście

Esc

Wejściowa

Poboru prądu

Przełączania

Wyjście

Esc

Przełączania

Wyjście

Esc

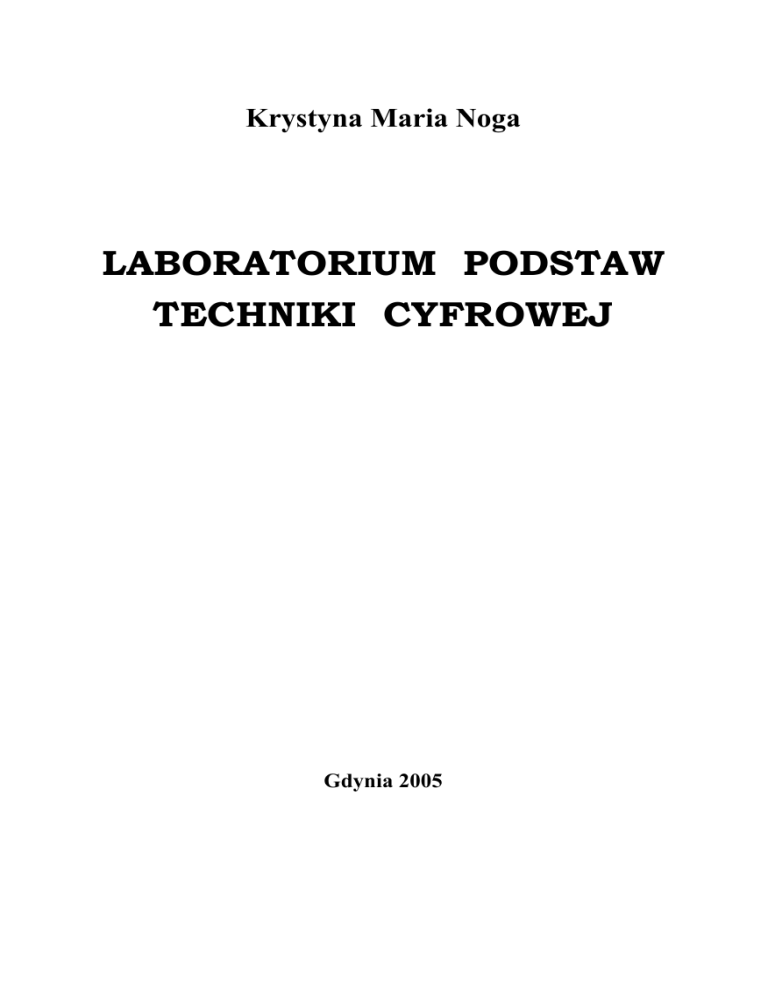

Rys.2.12. Struktura menu głównego

31

Pomoc

2.3.1.2. Wprowadzenie do ćwiczenia

WPROWADZENIE DO ĆWICZENIA uruchamia się automatycznie (gdy funkcja WPROWADZENIE jest aktywna) po określeniu elementu i wybraniu charakterystyki pomiarowej. W tej części

programu użytkownik ma możliwość zapoznania się z krótkim opisem

zjawisk, które będzie badał w czasie zajęć laboratoryjnych. Podstawowe wiadomości teoretyczne poparte są licznymi rysunkami i tabelami. Wyświetlony jest także schemat układu, jaki należy połączyć,

aby zarejestrować badaną charakterystykę. Po wyświetlanym na ekranie monitora wprowadzeniu teoretycznym można poruszać się kursorami kierunkowymi:

↑ - góra,

↓ - dół.

Naciśnięcie klawisza ENTER spowoduje przejście do CZĘŚCI

POMIAROWEJ przygotowanego oprogramowania (wprowadzenie

powinno być jednak przejrzane do końca, gdyż w przeciwnym wypadku naciśnięcie klawisza ENTER nie da spodziewanego rezultatu).

2.3.1.3. Część pomiarowa

Część pomiarowa, dostępna w przygotowanym oprogramowaniu,

jest rozbudowanym narzędziem do rejestrowania i obróbki określonych charakterystyk wybranych elementów półprzewodnikowych. W

układzie ekranu tej części programu można wyróżnić kilka podstawowych elementów:

• belka menu części pomiarowej,

• układ współrzędnych z naniesioną siatką i skalą,

• wartości wielkości czytanych przez mierniki,

• kwadrat z numerem i kolorem rejestrowanego wykresu,

• nazwa elementu i rodzaj badanej charakterystyki.

Belka menu CZĘŚCI POMIAROWEJ

Część pomiarowa udostępnia użytkownikowi oprogramowania

szereg funkcji, które ułatwiają rejestrację i obróbkę wykresu. Menu

części pomiarowej (rys.2.13) zawiera 7 następujących opcji:

•

•

•

•

•

•

•

PLIK,

EDYCJA,

NASTĘPNY,

SKASUJ,

SKALA,

POMOC,

KONIEC.

Uaktywnienie menu uzyskuje się poprzez przyciśnięcie klawisza F10;

spowoduje to pojawienie się zielonej belki na ostatnio wybranej opcji.

Do przemieszczania się między opcjami i funkcjami służą klawisze

kursorów, natomiast aby uruchomić wybraną opcję (lub funkcję),

należy nacisnąć klawisz ENTER.

Opcja PLIK

Wybór opcji PLIK powoduje wyświetlenie na ekranie monitora

podmenu zawierającego następujące funkcje:

• ZAPISZ,

• ODCZYTAJ,

• DRUKUJ,

• WYJŚCIE.

33

PLIK

Zapisz

Odczytaj

Drukuj

Wyjście

EDYCJA

NASTĘPNY

Wyświetlaj wszystkie wykresy

Wyświetlaj bieżący wykres

Wstaw / usuń opisy

Utwórz opis

Zamień mierniki

Pozycja

Linijka

Wyjście

SKASUJ

SKALA

Skasuj cały wykres

Skasuj ostatni punkt pomiarowy

Wyjście

Wykresy

Schemat

Wyjście

Rys. 2.13. Struktura menu CZĘŚCI POMIAROWEJ

35

POMOC

Edycja

Skasuj

Następny

Plik

Skala

Koniec

Klawiatura

Schemat

Info

KONIEC

Funkcja ZAPISZ

Funkcja ZAPISZ służy do zapisywania zarejestrowanych charakterystyk na dysku twardym lub na dyskietkach. Aby „zapisać” przebieg,

należy nadać mu nazwę (nie dłuższą niż 8 liter) oraz określić ścieżkę

dostępu (katalog) dla nowo utworzonego pliku. Gdy w określonym

przez użytkownika miejscu istnieje już plik o takiej nazwie, to zostanie on uaktualniony (poprzednie dane ulegną zniszczeniu). Wszystkie

pliki zostają automatycznie zapisane z rozszerzeniem ppm.

W funkcji Zapisz są aktywne następujące klawisze: Tab – przechodzenie między Nazwą a Katalogiem, Enter - potwierdzenie wyboru. Standardowo są także dostępne takie klawisze, jak: ↓, ↑, →, ←,

Backspace, Del, Home, End, Esc.

W wypadku podania błędnej lub nie istniejącej ścieżki, określenia nie

istniejącej stacji dysków czy też próby zapisu na zabezpieczoną dyskietkę program wyświetli na ekranie monitora odpowiedni komunikat.

Funkcja ODCZYTAJ

Funkcja ODCZYTAJ służy do odczytu plików z dowolnego napędu. Aby odczytać zbiór, należy określić jego nazwę oraz katalog, w

którym plik się znajduje. Niezbędnym warunkiem do odczytania pliku jest jego istnienie w danym miejscu. Powinien on również posiadać

odpowiedni format (pliki są nagrywane z rozszerzeniem ppm).

Obsługa klawiatury została zorganizowana podobnie jak w funkcji

ZAPISZ, dodatkowo po wciśnięciu klawisza F1 uaktywnia się nowe

okno zawierające informacje na temat otwieranego pliku.

W nowo otwartym okienku wyświetlana jest:

• dokładna ścieżka dostępu do wybranego pliku,

• data założenia,

• rozmiar zbioru,

• liczba wykresów,

• komentarz do poszczególnych wykresów,

• liczba punktów pomiarowych w kolejnych charakterystykach.

Wczytanie zbioru z dysku spowoduje zastąpienie bieżąco edytowanych wykresów nowymi, jednak zastąpione zostaną tylko te charakterystyki, które mają takie same numery, jak przebiegi odczytane z

dysku. Po zakończeniu funkcji ODCZYTAJ na monitorze będą

przedstawiane wszystkie charakterystyki (nowo otwarte i poprzednio

edytowane) aż do momentu odświeżenia ekranu. Umożliwia to porównanie kilku wcześniej zapisanych charakterystyk. Odświeżenie

ekranu spowoduje usunięcie zastąpionych wykresów (czyli wykresów o

tych samych numerach) z ekranu komputera. Odświeżenie ekranu następuje m.in. po wywołaniu takich opcji, jak SKALA czy SKASUJ.

Funkcja DRUKUJ

Za pomocą funkcji DRUKUJ możemy dokonać wydruku schematu pomiarowego lub aktualnie wyświetlanych na ekranie przebiegów. Do wydruku dołączone zostaną opisy poszczególnych wykresów.

Opcja EDYCJA

Szereg funkcji umożliwiających porównywanie wykresów, edytowanie opisów oraz obsługę mierników zostało zawartych w opcji

EDYCJA. Dokładny opis wszystkich możliwości przedstawiono w

kolejnych rozdziałach.

Opcja EDYCJA zawiera następujące funkcje:

• wyświetlaj wszystkie wykresy,

• wyświetlaj bieżący wykres,

• wstaw/usuń opisy,

• utwórz opis,

• zamień mierniki,

• pozycja,

• linijka.

Funkcja WYŚWIETLAJ WSZYSTKIE WYKRESY

Funkcja WYŚWIETLAJ WSZYSTKIE WYKRESY spowoduje, że oprócz bieżącego wykresu na ekranie komputera wyświetlane

będą pozostałe charakterystyki. Każda z charakterystyk ma swój numer i rysowana jest w innym kolorze.

Funkcja WYŚWIETLAJ BIEŻĄCY WYKRES

36

Funkcję WYŚWIETLAJ BIEŻĄCY WYKRES wywołujemy

wówczas, gdy chcemy, aby na ekranie monitora wyświetlany był tylko aktualnie edytowany wykres. Informacje o kolorze i numerze edytowanego wykresu są umieszczone w prawym dolnym rogu układu

współrzędnych (kwadrat w kolorze bieżącego wykresu z jego numerem w środku).

Funkcja WSTAW/USUŃ OPISY

Podczas rejestrowania charakterystyk użytkownik powinien

orientować się ile punktów pomiarowych zostało już określonych. W

tym właśnie celu została stworzona funkcja WSTAW/USUŃ OPISY.

Wywołanie jej spowoduje otwarcie na ekranie monitora okienka zawierającego podstawowe dane na temat sporządzanych przebiegów.

Ponowne wywołanie funkcji WSTAW/USUŃ OPISY spowoduje

usunięcie okna z ekranu monitora.

Funkcja UTWÓRZ OPIS

Dzięki funkcji UTWÓRZ OPIS można tworzyć komentarze do

poszczególnych wykresów; będą one dołączane do wydruków oraz

zapisywane na dysku wraz z charakterystykami. Tekst komentarza nie

powinien zawierać więcej niż 30 znaków.

Funkcja ZAMIEŃ MIERNIKI

Standardowo program przyporządkowuje osi X miernik podłączony pod COM1, a osi Y - miernik podłączony pod COM2. Jednak

ze względu na to, że użytkownik łącząc układ nie musi znać powyższych informacji, została wprowadzona funkcja ZAMIEŃ

MIERNIKI. Działanie jej sprowadza się do zamiany pierwotnych

ustawień. Wywołanie funkcji ZAMIEŃ MIERNIKI powoduje zmianę przyporządkowania mierników, tzn. miernik podłączony pod

COM1 zostanie przyporządkowany osi Y, a miernik podłączony pod

COM2 osi X.

Funkcja POZYCJA

Podczas analizowania zarejestrowanego na ekranie przebiegu niezbędna jest możliwość odczytu współrzędnych wybranych punktów

wykresu. Współrzędne można odczytywać bezpośrednio z naniesionej

37

w układzie skali (lecz jest to niewygodne i mało dokładne) lub za

pomocą funkcji POZYCJA.

Uaktywnienie funkcji POZYCJA spowoduje wyświetlenie na

ekranie komputera dwóch równolegle przecinających się prostych.

Wzajemne położenie linii można zmieniać za pomocą kursorów: ↑, ↓,

→, ←. Regulować można także skok (dokładność), z jakim następuje

przesuw linii (klawisz Pg Up - zwiększa dokładność, Pg Dn - zmniejsza dokładność), przy czym standardowo skok ustawiony jest na 10

punktów ekranowych. Współrzędne punktu przecięcia się prostych są

wyświetlane w prawym górnym rogu ekranu, natomiast informacja o

aktualnej dokładności przedstawiona jest w oknie u dołu ekranu.

Funkcja LINIJKA

Podczas analizy niektórych przebiegów zachodzi konieczność

znalezienia kąta nachylenia charakterystyki, sprawdzenia liniowości

wykresu, czy też poprowadzenia stycznej w określonym punkcie

przebiegu. W tym celu została wprowadzona funkcja LINIJKA. Zainicjowanie tej funkcji spowoduje wyświetlenie w układzie współrzędnych prostej o regulowanych punktach zaczepienia oraz zmiennym kącie nachylenia. Położeniem prostej steruje się za pomocą następujących klawiszy:

- ustawienie górnego końca linijki jako ruchomego (czerwony

↑

kwadrat u góry linijki),

- ustawienie dolnego końca linijki jako ruchomego (czerwony

↓

kwadrat u dołu linijki),

← , → - przesuwanie ruchomego końca linijki,

Pg Up - zwiększenie skoku (dokładności) linijki,

Pg Dn - zmniejszenie skoku (dokładności) linijki.

Okna informacyjne funkcji LINIJKA rozmieszczone są podobnie jak

w funkcji POZYCJA. W oknie w prawym górnym rogu ekranu wyświetlane są następujące dane:

• współrzędna X górnego punktu,

• współrzędna Y górnego punktu,

• współrzędna X dolnego punktu,

• współrzędna Y dolnego punktu,

• kąt nachylenia prostej względem osi X,

38

• tangens kąta nachylenia.

W dolnej części ekranu wyświetlane są informacje na temat ustawienia dokładności przesuwu linijki.

Opcja NASTĘPNY

W programie do badania podstawowych charakterystyk wybranych elementów półprzewodnikowych przewidziano możliwość wykreślania i zapisywania na jednym ekranie maksymalnie pięciu charakterystyk. Do przechodzenia między kolejnymi charakterystykami

służy opcja NASTĘPNY. Wywołanie jej spowoduje pojawienie się

okna dialogowego w którym należy wpisać numer sporządzanego

przebiegu (1 - 5). Jeśli wykres o danym numerze już istnieje, program

automatycznie powiadomi o tym użytkownika. Opcji NASTĘPNY

można także używać do przeglądania poszczególnych wykresów,

oczywiście wówczas, gdy aktywna jest funkcja WYŚWIETLAJ

BIEŻĄCY WYKRES.

Opcja SKASUJ

Opcja SKASUJ umieszczana jest standardowo w większości profesjonalnych programów jako funkcja opcji edycja. Jednak ze względu na to, że podczas rejestrowania charakterystyk często zachodzi

konieczność jej użycia, została ona umieszczona jako opcja w menu

części pomiarowej. Wywołanie jej spowoduje na ekranie otworzenie

podmenu zawierającego następujące dwie funkcje:

• SKASUJ CAŁY WYKRES,

• SKASUJ OSTATNI PUNKT POMIAROWY,

• WYJŚCIE.

Funkcja SKASUJ CAŁY WYKRES

Funkcji SKASUJ CAŁY WYKRES używamy wówczas, gdy

zachodzi konieczność skasowania całej charakterystyki. Po jej wywołaniu program zapyta o numer przebiegu do skasowania. Po wprowadzeniu numeru i po naciśnięciu klawisza ENTER wyszczególniony

wykres zostanie usunięty z pamięci oraz z ekranu monitora. Z wykonania polecenia możemy zrezygnować przyciskając klawisz Esc.

Funkcja SKASUJ OSTATNI PUNKT POMIAROWY Ze względu na

inercję mierników oraz na przypadkowe błędy często podczas reje39

strowania charakterystyki zachodzi konieczność cofnięcia (skasowania) ostatniego punktu pomiarowego. Funkcja SKASUJ OSTATNI

PUNKT POMIAROWY usuwa z pamięci komputera oraz ekranu

ostatnio zarejestrowany punkt bez względu na to, czy był on wstawiony na końcu charakterystyki, czy w jej środku. Ponowne wywołanie

tej funkcji (bez wczytania kolejnego punktu) nie przyniesie żadnego

rezultatu.

Opcja SKALA

Podczas uruchamiania części pomiarowej skala dla osi X i Y jest

dobrana optymalnie do rodzaju badanej charakterystyki. Wybierając

opcję SKALA użytkownik może sam określić zakresy dla poszczególnych osi. Uaktywnienie tej opcji spowoduje wyświetlenie na ekranie

monitora okna, w którym przedstawione są aktualnie ustawione zakresy. Do modyfikacji nastaw przeznaczone są następujące klawisze:

• Tab - przemieszczanie belki pomiędzy kolejnymi parametrami,

• ←, →, Home, End, Delete, Backspace - edycja wartości,

• Esc - rezygnacja i przywrócenie poprzednich nastaw.

Wpisując nowe wartości, należy zwrócić uwagę, aby zachowane

były następujące zależności:

Xmin < Xmax

Ymin < Ymax

W razie błędnie wprowadzonych danych komputer wygeneruje

ostrzeżenie o błędzie. Należy pamiętać, że właściwy dobór skali jest

bardzo ważnym czynnikiem w procesie pomiarowym.

40

Opcja POMOC

W opcji POMOC zawarte zostały podstawowe wskazówki na

temat możliwości, oferowanych w menu części pomiarowej. Uaktywnienie tej opcji spowoduje rozwinięcie okna zawierającego następujące polecenia:

•

•

•

•

•

•

•

•

•

EDYCJA,

SKASUJ,

NASTĘPNY,

PLIK,

SKALA,

KONIEC,

KLAWIATURA,

SCHEMAT,

INFO.

Po wybraniu dowolnego z pierwszych siedmiu poleceń zostanie wyświetlona pomoc zawierająca krótki opis danego zagadnienia. Użytkownik może również z tego podmenu przywołać schemat pomiarowy

do sporządzania aktualnej charakterystyki lub czołówkę programu

odpowiednio uaktywniając polecenia SCHEMAT oraz INFO.

Opcja KONIEC

Opcja KONIEC umożliwia opuszczenie części pomiarowej i

przejście do menu głównego.

2.3.2. Podstawowe zasady dokonywania pomiarów

za pomocą programu

Aby podczas ćwiczeń laboratoryjnych poprawnie obsługiwać

program, należy stosować się do następujących wytycznych:

1. Funkcje WPROWADZENIE oraz SORTOWANIE powinny

być ustawione jako aktywne (standardowo są tak ustawione).

41

2. Po wybraniu elementu i jego charakterystyki należy dokładnie

przeczytać WPROWADZENIE DO ĆWICZENIA.

3. Na podstawie przedstawionego we wprowadzeniu schematu należy połączyć układ pomiarowy, w miejsce mierników oznaczonych

na schemacie jako METEX należy użyć mierników METEX

M-4650CR, które powinny być uprzednio podłączone do komputera przez prowadzącego.

4. Sposób połączenia układu pomiarowego należy skonsultować z

prowadzącym ćwiczenie.

5. Zakresy na miernikach powinny być ustalone zgodnie z oczekiwanymi wielkościami i wartościami,

6. Przed opuszczeniem opcji WPROWADZENIE należy włączyć

jeden z mierników cyfrowych.

7. Przejście do CZĘŚCI POMIAROWEJ następuje po przeczytaniu całego wprowadzenia i naciśnięciu klawisza ENTER.

8. W części pomiarowej należy sprawdzić, czy uaktywniony miernik

przyporządkowany jest właściwej osi. W razie konieczności zmiany przyporządkowania należy użyć polecenia ZAMIEŃ

MIERNIKI z menu EDYCJA.

9. W wypadku wystąpienia błędu pomiaru po załączeniu drugiego

miernika należy go wyłączyć i włączyć ponownie.

10. Po przeprowadzeniu czynności 1÷9 można przystąpić do wykonywania pomiarów. Wielkości czytane przez mierniki będą wyświetlane u dołu ekranu oraz w układzie współrzędnych w postaci

okrągłego kursora. Punkty pomiarowe zatwierdza się klawiszem

SPACJA. Należy jednak zawsze poczekać, aż kursor ustabilizuje

się. Za pomocą polecenia SKASUJ OSTATNI PUNKT

POMIAROWY, znajdującego się w menu SKASUJ, można skasować ostatni punkt pomiarowy. Przed wydrukowaniem charakterystyk zaleca się zarejestrować sporządzone wykresy w pamięci

komputera (polecenie ZAPISZ w menu PLIK). Drukować można

zarówno charakterystyki, jak i schemat pomiarowy. Wykresy zostaną wydrukowane w aktualnie przyjętych zakresach.

11. Po wyjściu z programu do badania podstawowych charakterystyk

wybranych elementów półprzewodnikowych można, za pomocą

programu KONWERT.EXE, dokonać konwersji zapisanych podczas ćwiczenia plików z rozszerzeniem PPM na pliki DAT. Zbiór

42

zapisany z tym rozszerzeniem może być następnie importowany

przez inne, profesjonalne programy do obróbki danych (np. Excel).

2.4. PRZEBIEG ĆWICZENIA

2.4.1. Badanie bramki NAND (UCY 7400)

Po połączeniu układu pomiarowego zgodnie z rysunkiem 2.14

należy zdjąć charakterystykę przełączania UO = f ( UI ) bramki UCY

7400, ilustrującą zależność napięcia wyjściowego od napięcia wejściowego bramki.

Pomiary należy wykonać dla dwóch przypadków:

- wyjście nie obciążone,

- wyjście obciążone 10 wejściami bramek typu NAND.

Rys. 2.14. Schemat układu do pomiaru charakterystyki przełączania bramki

NAND UCY 7400 (wyjście nie obciążone)

Zależności prądowo-napięciowe na wejściu układu przedstawia

się za pomocą charakterystyki wejściowej II=f(UI). Schemat do pomiaru charakterystyki pokazano na rysunku 2.15. Charakterystykę

wejściową należy zarejestrować dla nie obciążonego wyjścia.

43

Rys. 2.15. Schemat układu do pomiaru charakterystyki wejściowej

bramki NAND UCY 7400

Charakterystykę poboru prądu, będącą graficznym przedstawieniem

zależności ICC=f(UI), należy zarejestrować dla nie obciążonego wyjścia bramki (schemat pomiarowy rys.2.16).

Rys. 2.16. Schemat układu do pomiaru charakterystyki poboru prądu bramki

NAND UCY 7400

44

2.4.2. Pomiar charakterystyki przełączania bramki

Open Colector UCY 7401

W układzie przedstawionym na rysunku 2.17 należy zdjąć charakterystykę UO=f(UI), przy czym pomiary należy przeprowadzić dla

trzech wartości obciążenia RO:

a) RO < RO min (nieznacznie mniejsze),

b) RO min < RO < Ro max,

c) RO > RO max.

UWAGA - wartości RO min , Ro max należy określić przed przystąpieniem do wykonywania ćwiczeń

laboratoryjnych.

Ucc − UOLmax

I OL max − N I IL max

Ucc − UOH min

=

n I OH max + N I IH max

Ro min =

Ro max

n - liczba bramek dołączonych do wspólnego rezystora Ro

N- liczba wejść bramek obciążających

Rys. 2. 17. Schemat układu pomiarowego do wyznaczenia

charakterystyk przełączania bramki UCY 7401

Podczas pomiarów należy pamiętać, aby nie przekraczać dopuszczalnych wartości prądów oraz napięć.

2.4.3. Pomiar charakterystyk wyjściowych bramki UCY 7400

Pomiaru charakterystyk wyjściowych bramki NAND należy dokonać w układzie jak na rysunku 2.18:

a) wejście A połączyć z masą układu, a miliamperomierz z rezystancją R1; zmieniając wartość R1 zdjąć charakterystykę UOL = f (IOL);

prąd IOL nie powinien przekroczyć 16 mA,

45

b) połączyć wejście A z plusem napięcia zasilania oraz miliamperomierz z rezystancją R2; zmieniając wartość R2 zdjąć charakterystykę UOH = f (IOH).

+5V

R1

1

/2 7400

14

mA

A

7

V

R2

Rys.2.18. Układ do pomiaru charakterystyk wyjściowych UO = f (IO)

podstawowej bramki NAND

2.4.4. Pomiar średniego czasu propagacji bramki

Łącząc ze sobą nieparzystą liczbę bramek NAND (rys.2.19),

uzyskuje się układ astabilny o okresie drgań T = 2 ⋅ n ⋅ tp,

gdzie:

n = 2k + 1 to liczba bramek, przy czym k = 0,1,2,…,

tp - średni czas propagacji bramki.

Należy dokonać pomiaru średniego czasu propagacji bramki poprzez

pomiar częstotliwości przebiegu generowanego przez układ z rysunku

2.19.

1

2

2k+1

Rys. 2.19. Układ astabilny o okresie drgań T = 2 (2k + 1)⋅ tp

46

2.4.5. Realizacja funkcji logicznej

Należy sprawdzić praktycznie poprawność działania zaprojektowanego w domu układu kombinacyjnego, składającego się wyłącznie

z bramek NAND typu UCY 7400, realizującego funkcję logiczną

wskazaną przez prowadzącego lub funkcję własną.

2.4.6. Opracowanie sprawozdania

•

•

•

Na otrzymanych charakterystykach należy zaznaczyć poziomy

logiczne odpowiadające stanom H i L.

Wyjaśnić różnicę pomiędzy charakterystykami dla wejść nie obciążonych i obciążonych.

Podać schemat ideowy ekspandera UCY 7460. Wyjaśnić zasadę

działania i podać przykład zastosowania.

2.5. ZAGADNIENIA KONTROLNE

1. Omówić sposoby zabezpieczania układów TTL przed zakłóceniami w obwodach zasilania.

2. Wyjaśnić pojęcia:

• wzmocnienie logiczne,

• amplituda logiczna,

• współczynnik jakości,

• margines szumów,

• statyczny margines szumów,

• moc strat,

• czas narastania i opadania impulsu zegarowego.

3. Przedstawić i opisać charakterystyki dynamiczne bramek TTL.

4. Wyjaśnić działanie bramki:

• AND-OR-INWERT,

• ekspandywnej i ekspandera,

• trójstanowej,

47

• Schmitta

• mocy.

5. Zminimalizować następujące funkcje boole’owskie:

F1 ( A , B, C, D) = A[( BC + D) A ]

F2 (A , B, C, D) = A B C + AB C + A B C + AB C + A B C + A C

F3 (A , B, C, D) = A C + A B C + B C + A B C

6. Wyjaśnić rolę diod D1, D2, D3 znajdujących się na schemacie

ideowym podstawowej bramki NAND.

7. Zaprojektować układ komparatora 2 liczb 2-bitowych A i B, który

będzie miał 3 wyjścia A=B, A>B, A<B, przy czym poziom H na

każdym z nich ma oznaczać spełnienie funkcji realizowanej przez

dane wyjście.

8. Zminimalizować metodą tablic Karnaugha następującą funkcję

(względem zer i jedynek):

f ( X1 , X 2 , X 3 , X 4 , X5 ) =

(0,1,2,4,5,6,11,13,16,17,20,21,29)

∑

9. Zaprojektować, wykorzystując tablice Karnaugha, układ realizujący funkcję: f ( X1 , X 2 , X 3, X 4 ) =

[1,3,7,8,9,1115

, , (5,6,10,14)]

∑

10. Zaprojektować, wykorzystując tablice Karnaugha, układ realizujący funkcję: f ( X1 , X 2 , X 3 , X 4 ) =

(1,4,5,6,7)

∏

11. Wyznaczyć minimalną postać funkcji realizowanej przez układy

przedstawione na rysunkach a, b; podać wykorzystywane prawa.

48

a)

X

Y

f(X,Y,Z)

Z

b)

"1"

A

"0"

B

f(A,B,C)

C

"1"

"0"

LITERATURA

1. KALISZ J., Podstawy elektroniki cyfrowej, WKiŁ, Warszawa 1991

2. Laboratorium podstaw techniki cyfrowej, praca zbiorowa pod red.

L. Wasilewskiego, WSM, Gdynia 1991

3. ŁAKOMY M., ZABRODZKI J., Cyfrowe układy scalone, PWN, Warszawa

1986

4. MAJEWSKI W., Układy logiczne, WN, Warszawa 1993

5. MISIUREWICZ P., Podstawy techniki cyfrowej, WNT, Warszawa 1985

6. PIECHA J., Elementy i układy cyfrowe, Wyd. Nauk. PWN, Warszawa 1990

7. PIEŃKOS J., TURCZYŃSKI J., Układy scalone TTL w systemach cyfrowych, WKiŁ, Warszawa 1986

8. PRZYTARSKI G., Program do badania podstawowych charakterystyk

wybranych elementów półprzewodnikowych, praca inżynierska, WSM, Katedra Automatyki Okrętowej, Gdynia 1996

49

9. SASAL W., Układy scalone serii UCA 64/UCY 74. Parametry i zastosowania, WKŁ, Warszawa 1985

10. TRACZYK W., Układy cyfrowe. Podstawy teoretyczne i metody syntezy,

WNT, Warszawa 1986

11. TURCZYŃSKI J., MAKSYMOWICZ R., MALEC B., PONIKIEWSKI J.,

Wybrane układy z techniki cyfrowej, WKiŁ, Warszawa 1983

50