Programowanie

Niskopoziomowe

Wykład 3: Architektura

procesorów x86

Dr inż. Marek Mika

Państwowa Wyższa Szkoła Zawodowa

im. Jana Amosa Komeńskiego

W Lesznie

Plan

•

•

•

•

•

Pojęcia ogólne

Budowa mikrokomputera

Cykl wykonania instrukcji

Cykl odczytu pamięci

Ładowanie i wykonywanie

programów

• Wielozadaniowość

Członkowie rodziny x86

• Procesory 32-bitowe Intel, AMD, Cyrix, VIA itp.

• Wszystkie procesory Intel IA-32:

– Intel 80386 (1985), Intel486, Pentium, Pentium MMX,

Pentium Pro, Pentium II, Pentium III, Pentium M, Intel

Core, Pentium 4

• Procesory AMD:

– Am386, Am486, Am5x86, K5, K6, K6-2, K6-3, Athlon,

Athlon XP

• Procesory Cyrix:

– Cyrix III - Samuel, 5x86, 6x86, Cyrix III – Joshua

• Procesory VIA:

– C3, C7

• Inne (m.in. NexGen, IDT, Centaur, Rise Technology)

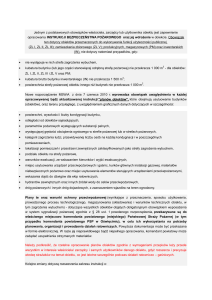

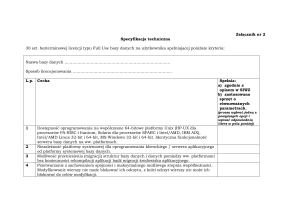

Blokowy schemat mikrokomputera

szyna danych, szyna we/wy

rejestry

Pamięć

CPU

ALU

CU

clk

szyna sterująca

szyna adresowa

Urz.

we/wy

nr 1

Urz.

we/wy

nr 2

CPU

• CPU (Central Processor Unit):

– rejestry – pełniące rolę komórek pamięci

– clk – zegar (o wysokiej częstotliwości)

synchronizujący wewnętrzne operacje procesora z

innymi komponentami systemu

– ALU (Arythmetic Logic Unit) – jednostka

arytmetyczno-logiczna wykonująca operacje

matematyczne (dodawanie, odejmowanie itd.) i

logiczne (iloczyn, alternatywa, negacja itd.)

– CU (Control Unit) – jednostka sterująca

koordynująca sekwencję kroków wykonywanych

podczas przetwarzania instrukcji maszynowej

CPU i inne komponenty systemu

• Po łączenie CPU z płytą główną

–

–

–

–

szyna danych

szyna we/wy

szyna adresowa

szyna kontrolująca

• Pamięć

– przechowuje dane i instrukcje programu

– przetwarzanie danych następuje w procesorze

– instrukcje programu są przesyłane do procesora

(pojedynczo lub grupami)

Szyny

• Fizycznie – wiązka przewodów (ścieżek)

• Szyna danych – do transferu danych i

instrukcji między pamięcią i CPU

• Szyna we/wy – do transferu danych między

CPU a urządzeniami we/wy

• Szyna sterująca – używa sygnałów binarnych

do synchronizacji działań wszystkich urządzeń

(układów) systemu

• Szyna adresowa – zawiera adres danej

(instrukcji) w pamięci komputera.

Zegar

•

•

•

•

•

•

•

Wszystkie operacje, w które zaangażowany jest procesor i

szyna systemowa są synchronizowane przez wewnętrzny

zegar o stałej częstotliwości

Podstawową jednostką czasu w systemie komputerowym jest

cykl zegarowy (maszynowy)

Długość cyklu zegarowego – to czas potrzebny na jedną

pełną zmianę stanu sygnału zegarowego (np. mierzony

pomiędzy dwoma kolejnymi zboczami narastającymi)

Prędkość zegara wyrażana jest w MHz (GHz) – w przypadku

zegara działającego z częstotliwością 1 GHz dł. cyklu

zegarowego wynosi 1ns

Instrukcje maszynowe mogą trwać od 1 cyklu zegarowego do

ponad 50 (np. mnożenie w procesorze 8088)

Instrukcje wymagające dostępu do pamięci często wymagają

pustych cykli zegarowych (stanów oczekiwania)

spowodowanych różnicami częstotliwości pracy CPU, szyny i

układów pamięci

Cykl wykonania instrukcji

• Program przed wykonaniem jest ładowany do pamięci

• Licznik rozkazów wskazuje na następną instrukcję

programu

• Kolejka instrukcji zawiera grupę kolejnych instrukcji

przewidzianych do wykonania

• Wykonanie instrukcji maszynowej wymaga trzech

podstawowych kroków:

– pobrania (fetch)

– zdekodowania (decode)

– wykonania (execute)

• Instrukcje wymagające dostępu do pamięci wymagają

dwóch dodatkowych kroków:

– pobrania argumentu z pamięci

– zapisania wyniku do pamięci

Kroki cyklu wykonania

•

•

•

•

•

Pobranie – CU pobiera następną instrukcję z kolejki i

odpowiednio zwiększa wartość licznika rozkazów (IP)

Dekodowanie – CU dekoduje instrukcję w celu określenia jej

działania, argumenty są wysyłane do ALU razem z sygnałami

sterującymi określającymi typ wykonywanej operacji

Pobranie argumentów z pamięci – krok wykonywany, gdy

argument instrukcji znajduje się w pamięci, CU korzysta z

operacji odczytu i zapisuje dane w wewnętrznych rejestrach

(niedostępnych w modelu programowym)

Wykonanie – ALU wykonuje instrukcję przy użyciu rejestrów

dostępnych w modelu programowym oraz rejestrów

wewnętrznych i wysyła wynik do odpowiedniego rejestru i/lub

pamięci, ALU ustawia również odpowiednio znaczniki

informujące o stanie procesora

Zapisanie wyniku do pamięci – krok wykonywany wtedy,

gdy instrukcja wymaga zapisu wyniku do pamięci, CU stosuje

w tym przypadku instrukcję zapisu

Sekwencja kroków

w pseudokodzie

loop

fetch next instruction

advance the instruction pointer (IP)

decode the instruction

if memory operand needed, read value

from memory

execute the instruction

if result is memory operand, write

result to memory

continue loop

Kod

Dane

Szyna adresowa

Pamięć

Szyna danych

Uproszczony schemat blokowy procesora

Cache kodu

IP

Dekoder instrukcji

CU

Rejestry

ALU

Cache danych

FPU

Schemat działania CPU

• Adres instrukcji kodu wystawiany jest na szynę

adresową

• Sterownik pamięci wystawia na szynę danych instrukcję

spod tego adresu

• Instrukcja trafia do pamięci podręcznej kodu

• IP określa, która instrukcja będzie wykonana jako

następna

• Dekoder instrukcji analizuje pobraną instrukcję i wysyła

odpowiednie (zależące od instrukcji) sygnały do CU

• CU koordynuje dalsze działanie ALU i FPU

• Synchronizacja transferu danych pomiędzy

odpowiednimi układami odbywa się przy użyciu sygnału

zegarowego przesyłanego szyną sterującą

(niewidoczną na schemacie)

Cykl odczytu pamięci

Cykl odczytu pamięci – opis

• Cykl 1:

– adres komórki pamięci, która ma być odczytana

wystawiany jest na szynę adresową (ADDR)

• Cykl 2:

– linia odczytu (RD) ustawiana w stan niski (0), co

sygnalizuje pamięci, że będą z niej odczytywane dane

• Cykl 3:

– cykl oczekiwania procesora

– w tym czasie sterownik pamięci wystawia na szynę

danych (DATA) dane odczytane z wybranej komórki

pamięci

• Cykl 4:

– linia odczytu przechodzi w stan wysoki (1) sygnalizując

procesorowi, że na szynie danych są dane gotowe do

odczytu

Pamięć podręczna

• Najtańsza pamięć operacyjna realizowana jako pamięć

DRAM jest zbyt wolna w porównaniu z CPU

• Potrzebna jest szybsza pamięć realizowana jako SRAM

w postaci pamięci podręcznej

• Odczyt instrukcji oraz danych z pamięci podręcznej

znacząco przyspiesza czas wykonania instrukcji

• Jeśli pobierana instrukcja (dana) znajduje się w pamięci

podręcznej, to mamy do czynienia z trafieniem pamięci

podręcznej (cache hit)

• W przeciwnym przypadku mówimy o chybieniu pamięci

podręcznej (cache miss), które wymaga pobrania

instrukcji (danej) z pamięci operacyjnej

Ładowanie i wykonywanie

programów

•

•

•

•

•

•

•

Użytkownik wywołuje program z linii poleceń

System operacyjny (OS) szuka nazwy programu w bieżącym katalogu,

jeśli jej nie znajdzie to szuka w zdefiniowanych katalogach (ścieżki), jeśli i

tam nie znajdzie tej nazwy, to sygnalizowany jest błąd

Jeśli program zostanie odnaleziony, to OS pobiera podstawowe informacje

o pliku programu (m.in. rozmiar pliku i jego fizyczne położenie na dysku)

OS określa następny dostępny obszar pamięci i tam ładuje program,

przydziela programowi blok pamięci, a informacje o rozmiarze i położeniu

plików umieszcza w tablicy deskryptorów, dodatkowo OS może zmienić

wartości wskaźników w programie, tak by zawierały adresy danych

programu

OS rozpoczyna wykonywanie pierwszej instrukcji programu (od tego

momentu mówimy już o procesie) i nadaje procesowi numer

identyfikacyjny (PID), który posłuży do śledzenia tego procesu w czasie

jego wykonywania

Proces działa samodzielnie, system operacyjny musi śledzić wykonywane

procesy i odpowiadać na żądania dostępu do zasobów (pamięć, pliki

dyskowe, urządzenia we\wy)

Po zakończeniu proces jest usuwany z pamięci

Wielozadaniowość

•

•

•

•

•

•

•

Wielozadaniowy system operacyjny potrafi wykonywać wiele

zadań jednocześnie

Zadanie definiowane jest jako proces lub jako wątek

Wątek współdzieli pamięć z innymi wątkami tego samego

procesu wykonywanymi „równocześnie”

W komputerach z jednym procesorem wielozadaniowość i

wielowątkowość realizowane są na zasadzie podziału czasu

procesora

Proces zwany schedulerem przydziela każdemu aktywnemu

procesowi wycinek czasu procesora, w którym wykonywany

jest blok instrukcji danego procesu, a po upływie tego czasu

sterowanie jest przekazywane do następnego procesu

Aby stworzyć iluzję wielozadaniowości przełączanie pomiędzy

procesami musi być stosunkowo szybkie.

Jednym z popularnych algorytmów jest Round-Robin

Round-Robin

• Algorytm stosowany w systemach wielozadaniowych

• Każde zadanie obsługiwane jest przez określony czas

po czym jest przerywane i trafia na koniec kolejki,

procesor przełączany jest na pierwsze zadanie w

kolejce itd.

• Przykład: 9 zadań, scheduler każdemu przydziela

procesor na 100 ms, przełączanie między zadaniami

trwa ok 8 ms, zatem jeden pełen cykl zajmuje 972 ms

• Procesor przed przejściem do nowego zadania musi

zapamiętać stan aktualnego zadania

• Często w wielozadaniowych OS istnieje możliwość

nadawania priorytetów zadaniom (im wyższy priorytet,

tym dłuższy wycinek czasu procesora)

• Wywłaszczalność zadań częstą cechą w

wielozadaniowych OS

DZIĘKUJĘ ZA UWAGĘ