Architektura

systemów

komputerowych

dr Artur Bartoszewski

Procesor – część II

Rejestry procesora dostępne programowo

A

B

D

H

F

C

E

L

PC

SP

SP - wskaźnik stosu

PC - licznik rozkazów

A – Akumulator

Zawiera jeden z operandów

działania i do niego przekazywany

jest wynik

B,C,D,E,H,L – rejestry robocze

(uniwersalne)

F - rejestr znaczników

Rejestry procesora dostępne programowo

Licznikiem rozkazów (PC) nazywamy rejestr mikroprocesora

zawierający adres komórki pamięci, w której przechowywany jest

rozkaz przeznaczony do wykonywania jako następny

Stosem nazywany wyróżniony obszar pamięci używany według

następujących reguł:

1. informacja zapisywana jest do kolejnych komórek, żadnego

adresu nie wolno pominąć,

2. odczyt informacji następuje w kolejności odwrotnej do zapisu,

3. informuje odczytujemy z ostatnio zapisanej komórki, natomiast

zapisujemy do pierwszej wolnej.

Stos

Stosem nazywany wyróżniony obszar pamięci używany według

następujących reguł:

1. Informacja zapisywana jest do kolejnych komórek, żadnego

adresu nie wolno pominąć,

2. Odczyt informacji następuje w kolejności odwrotnej do zapisu,

3. Informuje odczytujemy z ostatnio zapisanej komórki, natomiast

zapisujemy do pierwszej wolnej.

1; 2; 3; 4; 5

5

4

3

2

1

5; 4; 3; 2; 1

5

Stos

Stos jest rodzajem pamięci (buforem) typu LIFO (ang. Last In First Out).

Stos ma stały wymiar i położenie w pamięci. Konieczna jest więc tylko znajomość

adresu pierwszej wolnej komórki stosu (wierzchołka stosu). Do tego służy rejestr SP

- wskaźnik stosu.

Wskaźnik

stosu

5

4

3

2

1

Wskaźnikiem stosu nazywamy rejestr zawierający

adres ostatnio zapisanej komórki (wierzchołka) stosu

Rejestry procesora dostępne programowo

Stos jest rodzajem pamięci (buforem) typu LIFO (ang. Last In

First Out).

Stos ma stały wymiar i położenie w pamięci. Konieczna jest więc

tylko znajomość adresu pierwszej wolnej komórki stosu

(wierzchołka stosu). Do tego służy rejestr SP - wskaźnik stosu.

Wskaźnikiem stosu nazywamy rejestr zawierający adres

ostatnio zapisanej komórki (wierzchołka) stosu

Stos wykorzystywany jest najczęściej do zapamiętania adresu

bazowego programu przy wywołaniu podprogramu.

Wykorzystanie stosu do wywołania podprogramów

Zasada przetwarzania potokowego

Przypomnienie:

cykl rozkazowy składa się z wielu faz –

w najprostszej wersji z fazy pobrania i wykonania

rozkazu

Zasada przetwarzania potokowego

Jeżeli w procesorze wydzielić dwa „stanowiska obsługi" - jedno dla

pobierania rozkazów, a drugie dla ich wykonywania (rys), wówczas

można równocześnie realizować obie fazy cyklu rozkazowego:

pobieranie następnego rozkazu odbywa się w czasie, gdy jest

wykonywany rozkaz poprzedni . Takie działanie, analogiczne do

obróbki na taśmie produkcyjnej, nazywa się potokowym (pipeline).

Dwustopniowy potok rozkazów

Zakładając, że czas trwania każdej fazy cyklu jest taki sam,

uzyskuje się dwukrotne skrócenie czasu kończenia kolejnych

rozkazów (uzyskiwania wyników), mimo że sumaryczny czas

cyklu pozostaje niezmieniony.

Powody przestojów w przetwarzaniu

potokowym

Wystąpienie w programie rozgałęzień zależnych od efektów

poprzedzającej operacji (skoków warunkowych) - w takim

przypadku kolejny pobrany rozkaz może okazać się nieprzydatny i

trzeba pobierać inny, wskazany przez wykonywany rozkaz skoku.

Następuje wówczas opróżnienie potoku (flush) powodujące

chwilowy przestój jednostki wykonawczej,

Z kolei przestoje jednostki pobierającej rozkazy pojawiają się

wtedy, gdy samo wykonanie rozkazu wymaga kontaktu z pamięcią

dla odczytania lub zapisania argumentów.

Potoki wielostopniowe

Współczesne procesory stosują wielostopniowe przetwarzanie

potokowe (liczba stopni wynosi od kilku do kilkunastu), a dla

zredukowania strat wydajności wprowadza się rozwiązania

sprzętowo-programowe, takie jak równoczesny dostęp do pamięci

rozkazów i pamięci danych czy dynamiczne przewidywanie skoków.

Potok pięciostopniowy

Blok IF pobiera rozkazy, odczytując pamięć I-cache według licznika rozkazów.

Słowo rozkazowe jest następnie przekazywane do bloku dekodowania ID i

powoduje odczytanie argumentów operacji z właściwych rejestrów i

przekazanie ich do bloku wykonawczego EX/AC. Blok ten zawiera jednostkę

arytmetyczno-logiczną i wykonuje odpowiednie działanie na argumentach.

Stopień MA obsługuje pamięć danych i jest aktywny tylko w rozkazach load i

store, na jego wyjściu pojawia się słowo odczytane z D-cache lub wynik

przekazany ze stopnia EX. W ostatniej fazie cyklu, WB następuje wpisanie

wyniku do rejestru docelowego.

Potok pięciostopniowy

Każdym cyklu jest przetwarzanych

jednocześnie 5 rozkazów znajdujących się na

różnych etapach realizacji (a kolejne rozkazy

są kończone w każdym takcie zegara.

Konflikty w przetwarzaniu potokowym

Konflikt zasobów (structural hazard) powstaje wówczas, gdy w

tym samym czasie rozkazy będące w różnych fazach swojego

cyklu korzystają z tych samych zasobów komputera

Konflikty w przetwarzaniu potokowym

Konflikt danych (data hazard) polega na tym, że zmiany danych w

rejestrach lub w pamięci następują w innym czasie, niż wynika to z

logicznego następstwa rozkazów w programie.

Można uniknąć przestoju

potoku, gdyż wprawdzie

zawartość rejestru nie została

zaktualizowana, ale w takcie 3.

jest już dostępna na wyjściu

bloku EX i można ją przekazać

jako argument kolejnego

rozkazu - wymaga to

utworzenia w strukturze potoku

„drogi na skróty" i układu

wykrywającego tę sytuację

Konflikty w przetwarzaniu potokowym

Najbardziej kłopotliwe, trudne do usunięcia i obniżające efektywność

przetwarzania potokowego są konflikty sterowania (control hazard).

Powstają one przy wykonywaniu rozkazów rozgałęzienia programu,

które z natury rzeczy zakłócają sekwencję rozkazów, a jeżeli są

późno zidentyfikowane, to powodują konieczność zapełniania potoku

od nowa, co skutkuje stratą kilku cykli (tzw. „kara za skok").

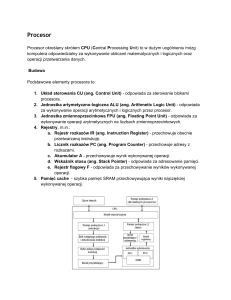

Procesory logiczne – technologia HT

Rejestry

Rejestry

Aparat wykonawczy (ALU)

Pamięć podręczna (CACHE)

Magistrala

systemowa

Pamięć operacyjna (RAM)

Hyper-Treading (HT) –

procesor posiada dwa

zestawy rejestrów dzięki

czemu emuluje obecność

dwóch układów

nazywanych procesorami

logicznymi

Pamiętajmy: program

„widzi” procesor jako

zestaw rejestrów.

Procesory fizyczne - rdzenie

Rejestry

Rejestry

Rejestry

Rejestry

Aparat

wykonawczy

Aparat

wykonawczy

Aparat

wykonawczy

Aparat

wykonawczy

CACHE

CACHE

Pamięć podręczna (CACHE)

Magistrala

systemowa

Pamięć operacyjna (RAM)

Magistrala

systemowa

Pamięć operacyjna (RAM)

Procesory fizyczne - rdzenie

W praktyce spotykam też hybrydę dwu powyższych schematów.

W procesorze Intel Core i7 każdy z rdzeni posiada własną

pamięć podręczną poziomów L1 i L2, natomiast pamięć poziomu

L3 jest wspólna.

L2

L2

Źródło: http://nvision.pl/img/art/procesory/intel_core_i7/intel_core_i7-2.jpg

L2

L2

Procesory fizyczne – rdzenie + HT

Rejestry

Rejestry

Rejestry

Rejestry

Aparat

wykonawczy

Aparat

wykonawczy

CACHE L2

CACHE L2

CACHE L3

Magistrala

systemowa

Pamięć operacyjna (RAM)

W najnowszych

procesorach (Core i7) dla

każdego z fizycznych

rdzeni zastosowano

technologię HyperTreading.

Oznacza to, że każdy

rdzeń widziany jest jako

dwa procesory logiczne i

może robić dwie rzeczy

naraz, np. czterordzeniowy

procesor Core i7 może

wykonywać 8 wątków

jednocześnie.

Pamięć CACHE

CACHE

zewnętrzny

CACHE

wbudowany

23

Zasoby pamięciowe komputera

Zasoby pamięciowe komputera

System zarządzania pamięcią zapewnia dostęp procesora do

tych różnorodnych zasobów w sposób niewidoczny dla

programu użytkowego.

Zadanie to jest realizowane sprzętowo na poziomie pamięci

cache i programowo - przez system operacyjny - na poziomie

pamięci wirtualnej.

W obu przypadkach obowiązuje ta sama koncepcja: niewielki

fragment pamięci wyższego poziomu jest w miarę potrzeby

kopiowany do pamięci niższego poziomu, bliższego

procesora.

poziomy pamięci cache

Pamięci wielodrożne są często stosowane w różnych

konfiguracjach i na różnych poziomach hierarchii - obecnie w

procesorach spotyka się pamięci cache wielopoziomowe:

poziom pierwszy (L1), zintegrowany z procesorem, stanowią

osobne pamięci rozkazów (l-cache) i danych (D-cache),

poziom drugi (L2) zajmuje większa i wolniejsza wspólna

pamięć również umieszczona w module procesora,

trzeci poziom cache (L3) można dołączyć w osobnym

module.

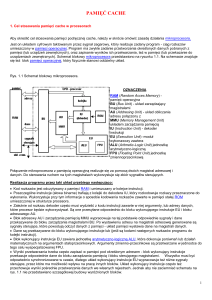

Organizacja pamięci CHAHE

CPU

CACHE

L1

CACHE

L2

Granice kości

krzemowej procesora

CACHE

L3

RAM

Architektura Look-aside („patrz w bok”)

W układzie konwencjonalnym

(często określany nazwą LookAside) którym mamy do czynienia

w procesorach x86 i Pentium,

pamięć podręczna dołączona jest

równolegle do magistrali

pamięciowej.

procesor odwołuje do pamięci

cache wykorzystując magistralę

pamięciową.

częstotliwości pracy cache jest

więc taka sama jak pamięci

głównej, jedynie czas dostępu

może ulec skróceniu.

Pamięć buforowa cache

Działanie pamięci buforowej cache, (zwanej pamięcią podręczną):

prawie zawsze, kiedy procesor poszukuje jakiegoś miejsca w

pamięci, jego kopia jest w cache - przypadek taki nazywa się

trafieniem (hit);

jeżeli odczytywany adres nie jest odwzorowany w cache, czyli

próba odczytu jest chybiona (miss);

wówczas następuje odczyt z pamięci głównej, ale

równocześnie do cache jest przepisywany blok (zwany linią)

kilku lub kilkunastu sąsiednich bajtów wraz z ich adresem. W

ten sposób chybienia powodują uzupełnianie pamięci buforowej

aż do momentu, kiedy nie będzie w niej miejsca i wtedy usuwa

się jedną linię - np. tę, która była najdawniej używana.

Pamięć buforowa cache

Efektywność pamięci buforowej określa tzw. współczynnik

trafień, czyli procent trafionych prób odczytu pamięci.

W rzeczywistych systemach współczynnik trafień wynosi

zależnie od programu 97% - 99%.

Architektura Look-throught („patrz w

bezpośrednio”)

Drugi sposób podłączenia pamięci

CACHE określany jest mianem LookThrough lub Inline Cache.

Procesor, zanim sięgnie do pamięci

głównej, napotyka układ pamięci

podręcznej.

Ta z kolei, sprzężona jest z pamięcią

główną poprzez właściwą magistralę

pamięciową.

Cache może więc być taktowany z

prędkością większą niż sama

magistrala pamięciowa, na przykład

dwa razy szybciej - takie

rozwiązanie zastosowano w

procesorze Pentium II.

Pamięć buforowa cache

W e współczesnej architekturze procesorów nie jest

już możliwe odwołanie się procesora do pamięci

RAM bez pośrednictwa pamięci CAHE

Pamięć buforowa cache

Ponieważ w pamięci buforowej znajdują się fragmenty pochodzące z

różnych, niespójnych, obszarów przestrzeni adresowej, muszą w niej być

skopiowane nie tylko dane, ale i ich adresy.

W katalogu adresów mogą być zapisane również inne informacje

dotyczące np. aktywności poszczególnych linii, które są używane przez

algorytmy usuwania niepotrzebnych bloków.

Zasoby pamięciowe komputera

Pamięć wirtualna

Pamięć wirtualna, ma stwarzać wrażenie, iż każde zadanie

dysponuje pamięcią o wielkości wynikającej z dostępnego

formatu adresu.

W rzeczywistości fizyczna pojemność pamięci głównej (RAM)

jest mniejsza i zamierzony efekt może być osiągnięty, jeżeli do

pamięci głównej będą w porę przenoszone potrzebne

fragmenty wirtualnej przestrzeni adresowej fizycznie

umieszczone w odpowiednio dużej pamięci zewnętrznej

(dyskowej).

Zadanie to jest realizowane metodą tzw. stronicowania (paging)

z użyciem środków sprzętowych wbudowanych w strukturę

systemu zarządzania pamięcią procesora oraz środków

programowych, którymi dysponuje system operacyjny.

Pamięć wirtualna

Informacja o aktualnym położeniu wszystkich stron

wirtualnych jest przechowywana przez system

operacyjny w katalogu zwanym tablicą stron.

Pamięć wirtualna

Ponieważ translacja adresu wirtualnego następuje przy każdym

kontakcie z pamięcią (pobranie rozkazu, odczytanie i zapisanie

danych), musi odbywać się na tyle szybko, żeby nie spowalniać

cyklu rozkazowego. Z tego względu część tablicy stron jest

realizowana w postaci pamięci cache zwanej TLB (translation

lookaside buffer) zawierającej ostatnio używane pozycje katalogu

stron.

Pamięć wirtualna

mechanizm stronicowania pozwala traktować pamięć

masową jako przedłużenie pamięci operacyjnej;

część kodu programu znajduję się w pamięci operacyjnej,

pozostała w pamięci masowej, jeżeli w trakcie realizacji

programu następuje odwołanie do pamięci masowej, blok

danych z tej pamięci ładowany jest do pamięci RAM, a inny

blok danych z pamięci RAM do pamięci masowej (dla

zwolnienia miejsca);

długie adresy (wirtualne) zawarte w programie tłumaczone

są na krótsze (fizyczne) adresy pamięci operacyjnej;

w trakcie translacji sprawdzana jest także dostępność

danych do których odwołuje sie program;

Tryby pracy procesora

Tryb rzeczywisty:

procesor przełącza sie w stan odwzorowujący

zachowanie procesora 16-to bitowego – pracuje

jako bardzo szybki procesor 8086.

Tryb chroniony:

tryb wprowadzony w celu ochrony poszczególnych

zadań pracujących pod kontrolą wielozadaniowego

systemu operacyjnego;

układy sprzętowe wbudowane w procesor kontrolują

odwołania do pamięci i wydają zezwolenie na

dostęp.

Tryby pracy procesora

tryb wirtualny:

stanowi kombinacje duch wcześniej omawianych

trybów;

każdy z programów (procesów) widzi swój własny

procesor 8086 pracujący w trybie rzeczywistym;

system jako całość dysponuje jednak

zaczerpniętymi z trybu chronionego

mechanizmami uniemożliwiającymi kolizje

pomiędzy współuczestniczącymi zadaniami

Rozwój procesora

Rozwój procesora

Najważniejsze spośród rozszerzeń dodanych

do architektury procesorów

MMX (MultiMedia eXtenntion) – miała na celu lepszy przydział mocy

obliczeniowej i zasobów procesora dla operacji związanych z

przetwarzaniem multimediów.

Zmiany w architekturze:

Zgrupowanie rozkazów w większe bloki (SIMD)

Nowe zespoły rejestrów (rejestry MMX)

Nowe rozkazy

Zwiększona pamięć podręczna, bufor rozkazów oraz długość

potoków przetwarzania instrukcji

Najważniejsze spośród rozszerzeń dodanych

do architektury procesorów

3DNow! - rozszerzenie architektury procesorów x86

stworzone przez firmę AMD, znacznie zwiększające

wydajność obliczeń zmiennoprzecinkowych, potrzebne

do odtwarzania grafiki trójwymiarowej i multimediów.

Był to pierwszy przypadek wprowadzenia takich istotnych

zmian przez firmę inną niż Intel.

Technologia 3DNow! uzupełnia i rozszerza możliwości

akceleratorów graficznych, przyspieszając obliczenia

zmiennoprzecinkowe występujące w początkowych etapach

przetwarzania grafiki.

Technologia ta pozwala uzyskać do 4 wyników

zmiennoprzecinkowych w ciągu jednego cyklu pracy

procesora.

Najważniejsze spośród rozszerzeń dodanych

do architektury procesorów

SSE – ok. 70 nowych poleceń.

SSE 2 – poszerza środowisko działania procesora o

nowe typy danych i nowe instrukcje

SSE 3 – 13 nowych poleceń oraz przyspieszenie

wykonywania dotychczasowych

SSE 4 - wprowadza 54 nowe instrukcje rozszerzenie istniejących instrukcji wektorowych

operujących na liczbach całkowitych oraz

zmiennoprzecinkowych

SSE 5 – (planowane) dodaje 82 nowe rozkazy: 30

działających na liczbach zmiennoprzecinkowych

oraz 52 na liczbach całkowitych

Najważniejsze spośród rozszerzeń dodanych

do architektury procesorów

AVX (Advanced Vector Extensions) - kolejne rozszerzenie zestawu

instrukcji SSE opublikowane w marcu 2008 przez firmę Intel.

Pierwsze implementacje sprzętowe są zapowiadane na 2010 rok.

Najważniejsze zmiany:

1.

W AVX wprowadzono 256-bitowe rejestry - 2 razy większe niż

wykorzystywane dotychczas w SSE. Nowych rejestrów jest 16 i w

asemblerze noszą nazwy YMM0...YMM15. W dalszych wersjach AVX

mogą pojawić się jeszcze większe rejestry, 512-, a nawet 1024bitowe.

2.

Dodano kilka rozkazów działających wyłącznie na rejestrach YMM (19

instrukcji).

3.

Dodane 4-argumentowe rozkazy akumulujące wyniki mnożenia

wektorów liczb zmiennoprzecinkowych

4.

Dodane specjalizowane instrukcje wspomagające szyfrowanie AES

(6 instrukcji).

Dziękuję za uwagę