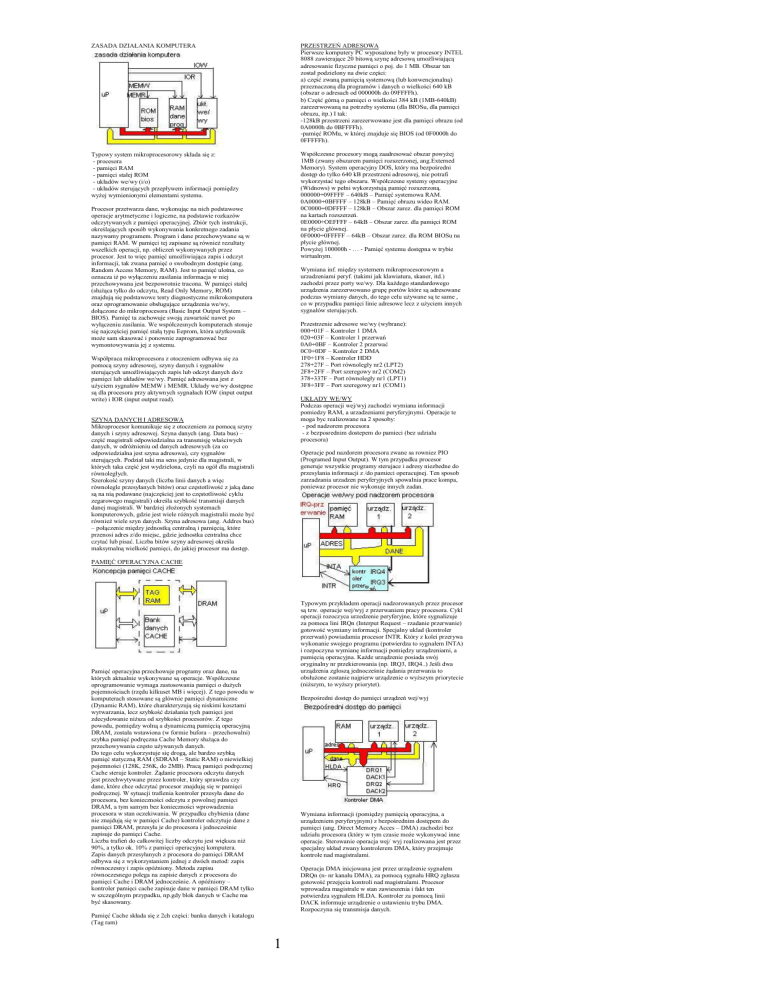

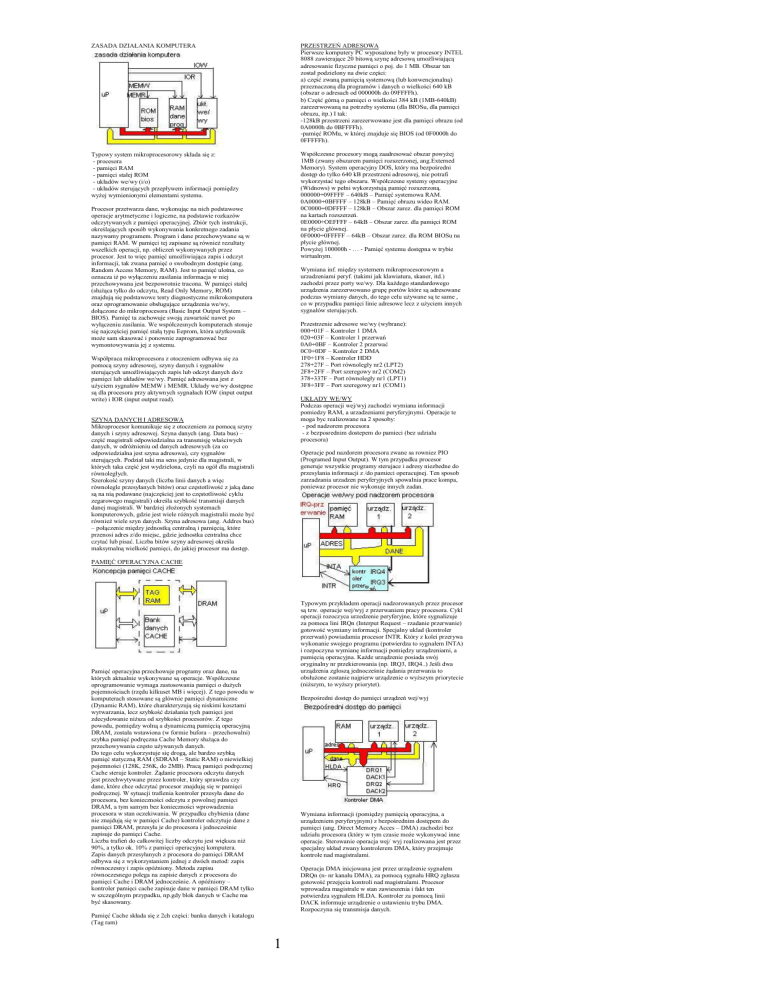

ZASADA DZIAŁANIA KOMPUTERA

PRZESTRZEŃ ADRESOWA

Pierwsze komputery PC wyposażone były w procesory INTEL

8088 zawierające 20 bitową szynę adresową umożliwiającą

adresowanie fizyczne pamięci o poj. do 1 MB. Obszar ten

został podzielony na dwie części:

a) część zwaną pamięcią systemową (lub konwencjonalną)

przeznaczoną dla programów i danych o wielkości 640 kB

(obszar o adresach od 000000h do 09FFFFh).

b) Część górną o pamięci o wielkości 384 kB (1MB-640kB)

zarezerwowaną na potrzeby systemu (dla BIOSu, dla pamięci

obrazu, itp.) I tak:

-128kB przestrzeni zarezerwowane jest dla pamięci obrazu (od

0A0000h do 0BFFFFh).

-pamięć ROMu, w której znajduje się BIOS (od 0F0000h do

0FFFFFh).

Typowy system mikroprocesorowy składa się z:

- procesora

- pamięci RAM

- pamięci stałej ROM

- układów we/wy (i/o)

- układów sterujących przepływem informacji pomiędzy

wyżej wymienionymi elementami systemu.

Współczesne procesory mogą zaadresować obszar powyżej

1MB (zwany obszarem pamięci rozszerzonej, ang.Externed

Memory). System operacyjny DOS, który ma bezpośredni

dostęp do tylko 640 kB przestrzeni adresowej, nie potrafi

wykorzystać tego obszaru. Współczesne systemy operacyjne

(Widnows) w pełni wykorzystują pamięć rozszerzoną.

000000÷09FFFF – 640kB – Pamięć systemowa RAM.

0A0000÷0BFFFF – 128kB – Pamięć obrazu wideo RAM.

0C0000÷0DFFFF – 128kB – Obszar zarez. dla pamięci ROM

na kartach rozszerzeń.

0E0000÷OEFFFF – 64kB – Obszar zarez. dla pamięci ROM

na płycie głównej.

0F0000÷0FFFFF – 64kB – Obszar zarez. dla ROM BIOSu na

płycie głównej.

Powyżej 100000h - … - Pamięć systemu dostępna w trybie

wirtualnym.

Procesor przetwarza dane, wykonując na nich podstawowe

operacje arytmetyczne i logiczne, na podstawie rozkazów

odczytywanych z pamięci operacyjnej. Zbiór tych instrukcji,

określających sposób wykonywania konkretnego zadania

nazywamy programem. Program i dane przechowywane są w

pamięci RAM. W pamięci tej zapisane są również rezultaty

wszelkich operacji, np. obliczeń wykonywanych przez

procesor. Jest to więc pamięć umożliwiająca zapis i odczyt

informacji, tak zwana pamięć o swobodnym dostępie (ang.

Random Access Memory, RAM). Jest to pamięć ulotna, co

oznacza iż po wyłączeniu zasilania informacja w niej

przechowywana jest bezpowrotnie tracona. W pamięci stałej

(służąca tylko do odczytu, Read Only Memory, ROM)

znajdują się podstawowe testy diagnostyczne mikrokomputera

oraz oprogramowanie obsługujące urządzenia we/wy,

dołączone do mikroprocesora (Basic Input Output System –

BIOS). Pamięć ta zachowuje swoją zawartość nawet po

wyłączeniu zasilania. We współczesnych komputerach stosuje

się najczęściej pamięć stałą typu Eeprom, która użytkownik

może sam skasować i ponownie zaprogramować bez

wymontowywania jej z systemu.

Wymiana inf. między systemem mikroprocesorowym a

urzadzeniami peryf. (takimi jak klawiatura, skaner, itd.)

zachodzi przez porty we/wy. Dla każdego standardowego

urządzenia zarezerwowano grupę portów które są adresowane

podczas wymiany danych, do tego celu używane są te same ,

co w przypadku pamięci linie adresowe lecz z użyciem innych

sygnałów sterujących.

Przestrzenie adresowe we/wy (wybrane):

000÷01F – Kontroler 1 DMA

020÷03F – Kontroler 1 przerwań

0A0÷0BF – Kontroler 2 przerwać

0C0÷0DF – Kontroler 2 DMA

1F0÷1F8 – Kontroler HDD

278÷27F – Port równoległy nr2 (LPT2)

2F8÷2FF – Port szeregowy nr2 (COM2)

378÷337F – Port równoległy nr1 (LPT1)

3F8÷3FF – Port szeregowy nr1 (COM1)

Współpraca mikroprocesora z otoczeniem odbywa się za

pomocą szyny adresowej, szyny danych i sygnałów

sterujących umożliwiających zapis lub odczyt danych do/z

pamięci lub układów we/wy. Pamięć adresowana jest z

użyciem sygnałów MEMW i MEMR. Układy we/wy dostępne

są dla procesora przy aktywnych sygnałach IOW (input output

write) i IOR (input output read).

UKŁADY WE/WY

Podczas operacji wej/wyj zachodzi wymiana informacji

pomiedzy RAM, a urzadzeniami peryferyjnymi. Operacje te

moga byc realizowane na 2 sposoby:

- pod nadzorem procesora

- z bezposrednim dostepem do pamieci (bez udzialu

procesora)

SZYNA DANYCH I ADRESOWA

Mikroprocesor komunikuje się z otoczeniem za pomocą szyny

danych i szyny adresowej. Szyna danych (ang. Data bus) –

część magistrali odpowiedzialna za transmisję właściwych

danych, w odróżnieniu od danych adresowych (za co

odpowiedzialna jest szyna adresowa), czy sygnałów

sterujących. Podział taki ma sens jedynie dla magistrali, w

których taka część jest wydzielona, czyli na ogół dla magistrali

równoległych.

Szerokość szyny danych (liczba linii danych a więc

równolegle przesyłanych bitów) oraz częstotliwość z jaką dane

są na nią podawane (najczęściej jest to częstotliwość cyklu

zegarowego magistrali) określa szybkość transmisji danych

danej magistrali. W bardziej złożonych systemach

komputerowych, gdzie jest wiele różnych magistralii może być

również wiele szyn danych. Szyna adresowa (ang. Addres bus)

– połączenie między jednostką centralną i pamięcią, które

przenosi adres z/do miejsc, gdzie jednostka centralna chce

czytać lub pisać. Liczba bitów szyny adresowej określa

maksymalną wielkość pamięci, do jakiej procesor ma dostęp.

Operacje pod nazdorem procesora zwane sa rowniez PIO

(Programed Input Output). W tym przypadku procesor

generuje wszystkie programy sterujace i adresy niezbedne do

przesylania informacji z /do pamieci operacujnej. Ten sposob

zarzadzania urzadzen peryferyjnych spowalnia prace kompa,

poniewaz procesor nie wykonuje innych zadan.

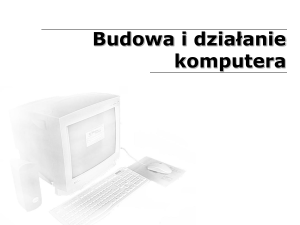

PAMIĘĆ OPERACYJNA CACHE

Typowym przykładem operacji nadzorowanych przez procesor

są tzw. operacje wej/wyj z przerwaniem pracy procesora. Cykl

operacji rozoczyca urzedzenie peryferyjne, które sygnalizuje

za pomoca lini IRQn (Interput Request – rzadanie przerwanie)

gotowość wymiany informacji. Specjalny uklad (kontroler

przerwań) powiadamia procesor INTR. Który z kolei przerywa

wykonanie swojego programu (potwierdza to sygnałem INTA)

i rozpoczyna wymianę informacji pomiędzy urządzeniami, a

pamięcią operacyjna. Każde urządzenie posiada swój

oryginalny nr przekierowania (np. IRQ3, IRQ4..) Jeśli dwa

urządzenia zgłoszą jednocześnie żądania przerwania to

obsłużone zostanie najpierw urządzenie o wyższym priorytecie

(niższym, to wyższy priorytet).

Pamięć operacyjna przechowuje programy oraz dane, na

których aktualnie wykonywane są operacje. Współczesne

oprogramowanie wymaga zastosowania pamięci o dużych

pojemnościach (rzędu kilkuset MB i więcej). Z tego powodu w

komputerach stosowane są głównie pamięci dynamiczne

(Dynamic RAM), które charakteryzują się niskimi kosztami

wytwarzania, lecz szybkość działania tych pamięci jest

zdecydowanie niższa od szybkości procesorów. Z tego

powodu, pomiędzy wolną a dynamiczną pamięcią operacyjną

DRAM, została wstawiona (w formie bufora – przechowalni)

szybka pamięć podręczna Cache Memory służąca do

przechowywania często używanych danych.

Do tego celu wykorzystuje się drogą, ale bardzo szybką

pamięć statyczną RAM (SDRAM – Static RAM) o niewielkiej

pojemności (128K, 256K, do 2MB). Pracą pamięci podręcznej

Cache steruje kontroler. Żądanie procesora odczytu danych

jest przechwytywane przez kontroler, który sprawdza czy

dane, które chce odczytać procesor znajdują się w pamięci

podręcznej. W sytuacji trafienia kontroler przesyła dane do

procesora, bez konieczności odczytu z powolnej pamięci

DRAM, a tym samym bez konieczności wprowadzenia

procesora w stan oczekiwania. W przypadku chybienia (dane

nie znajdują się w pamięci Cache) kontroler odczytuje dane z

pamięci DRAM, przesyła je do procesora i jednocześnie

zapisuje do pamięci Cache.

Liczba trafień do całkowitej liczby odczytu jest większa niż

90%, a tylko ok. 10% z pamięci operacyjnej komputera.

Zapis danych przesyłanych z procesora do pamięci DRAM

odbywa się z wykorzystaniem jednej z dwóch metod: zapis

równoczesny i zapis opóźniony. Metoda zapisu

równoczesnego polega na zapisie danych z procesora do

pamięci Cache i DRAM jednocześnie. A opóźniony –

kontroler pamięci cache zapisuje dane w pamięci DRAM tylko

w szczególnym przypadku, np.gdy blok danych w Cache ma

być skasowany.

Bezpośredni dostęp do pamięci urządzeń wej/wyj

Wymiana informacji (pomiędzy pamięcią operacyjna, a

urządzeniem peryferyjnym) z bezpośrednim dostępem do

pamięci (ang. Direct Memory Acces – DMA) zachodzi bez

udziału procesora (który w tym czasie może wykonywać inne

operacje. Sterowanie operacja wej/ wyj realizowana jest przez

specjalny układ zwany kontrolerem DMA, który przejmuje

kontrole nad magistralami.

Operacja DMA inicjowana jest przez urządzenie sygnałem

DRQn (n- nr kanału DMA), za pomocą sygnału HRQ zgłasza

gotowość przejęcia kontroli nad magistralami. Procesor

wprowadza magistrale w stan zawieszenia i fakt ten

potwierdza sygnałem HLDA. Kontroler za pomocą linii

DACK informuje urządzenie o ustawieniu trybu DMA.

Rozpoczyna się transmisja danych.

Pamięć Cache składa się z 2ch części: banku danych i katalogu

(Tag ram)

1