BADANIE BRAMEK SPECJALNYCH

Celem ćwiczenia jest poznanie i pokazanie podstawowych parametrów badanych bramek i wyjaśnienie różnicy

pomiędzy układami TTL serii standardowej, a układami bramek specjalnych.

Spis treści

BADANIE BRAMEK SPECJALNYCH ............................................................................................................... 1

1

Wiadomości ogólne ........................................................................................................................................ 2

1.1

Rodzaje bramek cyfrowych .................................................................................................................... 2

1.1.1

Podstawowa bramka serii standardowej 74 .................................................................................... 2

1.1.2

Układ wejściowy bramki logicznej TTL serii standardowej. ......................................................... 2

1.1.3

Podstawowa bramka TTL (7400) ................................................................................................... 3

1.1.4

Charakterystyka przejściowa bramki TTL NAND ......................................................................... 4

1.1.5

Bramka z układem Schmitta ........................................................................................................... 4

1.1.6

Bramka typu otwarty kolektor (OC)............................................................................................... 6

1.1.7

Bramka trójstanowa ........................................................................................................................ 8

2

Badanie bramek specjalnych......................................................................................................................... 9

2.1

Program ćwiczenia ................................................................................................................................. 9

2.2

Przebieg pomiarów ................................................................................................................................. 9

2.3

Badanie bramki z przerzutnikiem Schmitta ......................................................................................... 10

2.3.1

Kształtowanie przebiegów TTL z przebiegów wolno zmiennych ............................................... 10

2.3.2

Wyznaczanie charakterystyk przejściowych ................................................................................ 10

2.3.3

Pomiar czasu propagacji bramki Schmitta ................................................................................... 10

2.4

Badanie bramki typu otwarty kolektor ................................................................................................. 11

2.4.1

Wyznaczanie Rmin, Rmax ........................................................................................................... 11

2.4.2

Realizacja funkcji logicznych z użyciem bramek OC .................................................................. 11

2.4.3

Realizacja zadanej funkcji logicznej z użyciem bramki OC ........................................................ 12

2.5

Badanie bramki trójstanowej ................................................................................................................ 12

2.5.1

Wyznaczanie tablicy prawdy bramki trójstanowej ....................................................................... 12

2.5.2

Pomiar czasów blokowania i odblokowania ................................................................................ 12

3

Opis Stanowiska pracy................................................................................................................................. 13

3.1

Wykaz elementów użytych w ćwiczeniu ............................................................................................. 13

3.2

Schematy aplikacyjne układów scalonych badanych bramek .............................................................. 13

3.2.1

Bramka z przerzutnikiem Schmitta .............................................................................................. 13

3.2.2

Bramka typu otwarty kolektor ...................................................................................................... 14

3.2.3

Bramka trójstanowa ...................................................................................................................... 14

1 Wiadomości ogólne

1.1 Rodzaje bramek cyfrowych

Do najbardziej rozpowszechnianych układów cyfrowych wykonanych w monolitycznej technice bipolarnej

należą układy zrealizowane w technice tranzystorowo – tranzystorowej TTL (z ang. Transistor Transistor

Logic).

W technice TTL są obecnie produkowane następujące serie:

podstawowa – 74,

Schottky’ego – 742 (ang. Schottky),

Schottky’ego małej mocy – 74ALS (ang. Low power Schottky),

szybka – 74F (ang. Fast),

ulepszona Schottky’ego małej mocy – 74ALS (ang. Advanced Low power Schottky),

ulepszona Schottky’ego 74AS (ang. Advanced Schottky).

Można jeszcze spotkać układy serii o dużej szybkości (al. Wolniejsze od serii 74F) – 74H (ang. High speed)

oraz układy serii małej mocy 74L (ang. Low power). Serii tych obecnie nie są produkowane.

W ramach serii standarsowej są wytwarzane także bramki specjalne, różniące się od powyżej wymienionych

bramek budową obwód wejściowych lub wyjściowych. Rolą jaką spełniają one w układach cyfrowych wynika

z ich budowy i zostanie omówiona poniżej.

1.1.1 Podstawowa bramka serii standardowej 74

Podstawową i powszechnie stosowaną bramką jest bramka NAND. Jest ona układem o dwu lub większej

liczbie wejść. Realizują one funkcję iloczynu zmiennych wejściowych.

Bramkę NAND przedstawiono na rysunku 1.1.

Rys. 1.1. Dwuwejściowa bramka NAND (NIE-I): a) tablica prawdy; b) symbol graficzny

Bramka NAND jest funkcjonalnie pełna, bowiem stosując ją można zrealizować zarówno operacje iloczynu

logicznego (AND), jak i operacje negacji (NOT) – czyli dowolną funkcję logiczną.

1.1.2 Układ wejściowy bramki logicznej TTL serii standardowej.

Układ wejściowy bramki logicznej iloczynowej NAND zrealizowany w technice TTL jest zbudowany przy

użyciu tzw. tranzystora wieloemiterowego. Jest to układ tylu tranzystorów o połączonych bazach oraz

kolektorach, ile wynosi liczba wejść. W wersji scalonej takiego układu odpowiednie obszary baz i kolektorów

są także połączony, co daje w efekcie strukturę określoną jako tranzystor wieloemiterowy.

Na rysunku 1.2. przedstawiono schemat tranzystora wieloemiterowego jako układ połączeń zwykłych

tranzystorów, jego symbol graficzny oraz schemat zastępczy.

Rys. 1.2. Układ wejściowy bramki logicznej iloczynowej TTL: a) układ połączeń; b) symbol graficzny; c)

schemat zastępczy

1.1.3 Podstawowa bramka TTL (7400)

Układ 7400 zawiera w swojej obudowie cztery dwuwejściowe bramki NAND. Jest to układ 14 – nóżkowy. Po

trzy (dwie wejściowe, jedna wyjściowa) nóżki na każdą z czterech bramek plus dwie na doprowadzenie

napięcia zasilającego.

Schemat ideowy bramki NAND przedstawiono na rysunku 1.3.

Rys. 1.3. Schemat ideowy bramki NAND (7400)

Stopień wejściowy bramki stanowi tranzystor wieloemiterowy T1. Tranzystor T2 jest podstawowym

elementem wzmacniacza pośredniczącego, a tranzystory T3 i T4 – stopnia wyjściowego. Do wejść bramki są

dołączone iody, które tłumią oscylacje powstałe w liniach łączących bramk w czasie ich przełączania i

zapobiegają powstawaniu ujemnych napięć o wartości większej niż ok. 0,7V.

Wszystkie tranzystory (poza tranzystorem T3) w tym układzie pracują w charakterze tzw. kluczy

tranzystorowych, tzn. każdy z nich znajduje się w jednym z dwóch stanów pracy: w stanie nasycenia lub w

stanie odcięcia (zatkania).

W stanie nasycenia na wszystkich wejściach złącza emiter – baza tranzystora T1 są spolaryzowane zaporowo,

prąd bazy tego tranzystora płynie przez złącza baza – kolektor do bazy tranzystora T2 powodując jego

nasycenie. W tym stanie tranzystor T3 jest odcięty, a tranzystor T4 jest w stanie przewodzenia z nasyceniem.

Na wyjściu występuje stan niski (0). Jeżeli jedno lub więcej wejść znajduje się w stanie niskim (0), to

tranzystor T1 przewodzi z nasyceniem, a tranzystor T2 jest odcięty. W takiej sytuacji przy jednoczesnym

odcięciu tranzystora T4 na wyjściu jest stan wysoki (1).

Dioda D przyśpiesza odcięcie tranzystora Y3 w czasie procesu przełączania ograniczając stan przejściowy, w

którym oba tranzystory stopnia wyjściowego przewodzą.

1.1.4 Charakterystyka przejściowa bramki TTL NAND

Działanie bramki NAND można opisać za pomocą charakterystyk statycznych: przejściowej Uo=f(UI) i poboru

prądu przez bramkę Icc =f(UI)

Charakterystykę przejściową oraz charakterystykę poboru prądu przedstawiono na rysunku 1.4.

Rys 1.4. Charakterystyka przejściowa Uo=f(UI) oraz chrakterystyka poboru prądu przez bramkę Icc=f(UI)

Duża stromość charakterystyki przejściowej Uo=f(UI), (rys. 1.4.), jest spowodowana tym, że przewodzenie

tranzystora T4 (rys. 1.3.), w stanie wysokim, bocznikuje rezystancję tranzystora T3, powodując gwałtowne

zmniejszenie rezystancji tranzystora T2. W stanie wysokim zaczyna najpierw przewodzić tranzystor T2, który

przewodzi w obszar pracy aktywnej. Pracuje on jako prosty wzmacniacz w układzie wspólnego emitera z

ujemnym prądowym sprzężeniem zwrotnym. Powoduje to niewielkie nachylenie charakterystyki przejściowej.

Również istotny jest przebieg prądu pobieranego przez bramkę – charakterystyka Icc=f(UI) na rys. 1.4. Wynika

z niej, że każdorazowemu przełączeniu bramki TTL towarzyszy impuls (o względnej dużej amplitudzie) pobór

prądu ze źródła. Skutki, jakie powoduje, są analogicznie do tych, jakie można zauważyć w chwili załączania

silnika indukcyjnego do sieci. W chwili załączania takiego silnika wartość prądu rozruchowego wzrasta o

kilkakrotnie w stosunku do wartości początkowej. Mechanizm powstawania takiego zakłócenia jest

następujący: duży impuls prądowy powoduje duży spadek napięcia na impedancji źródła zasilania. Aby

zapobiec występowania takiego zakłócenia stosuje się tzw. kondensatory Blokujące. Są to bezindukcyjne

kondensatory ceramiczne o niewielkiej pojemności (0,01 – 0,1 mF).

1.1.5 Bramka z układem Schmitta

Schemat ideowy bramki NAND z przerzutnikiem Schmitta przedstawiono na rysunku 1.5. W jednej obudowie

znajdują się cztery (dwuwejściowe) bramki NAND.

Rys. 1.5. Schemat ideowy dwuwejściowej bramki I-NIE z przerzutnikiem Schmitta

Na schemacie z rysunku 1.5. można wyodrębnić następujące układy:

- układ wejściowy (prawie identyczny jak w zwykłej bramce TTL),

- układ wyjściowy (identyczny jak w zwykłej bramce TTL), oraz dodatkowe obwody (w odniesieni do układu

zwykłej bramki TTL 7400):

- przerzutnik Schmitta,

- układ przesuwania poziomu napięcia.

Przełączenie bramki następuje przy przekroczeniu napięcia ok. 1,7V przy narastaniu sygnału wejściowego i

przy napięciu ok. 0,9V przy opadaniu sygnału. Widać to na rysunku 1.6., na którym pokazano charakterystykę

przejściową tej bramki.

Rys. 1.6. Charakterystyka przejściowa ramki z przerzutnikiem Schmitta. Up+ - napięcie przełączania przy

rosnącym napięciu wejściowym,

Up- - napięcie przełączania przy malejącym napięciu wejściowym.

Histerezę przyłączeniową uzyskuje się dzięki temu, że bramka zawiera dodatkowo układ z przerzutnikiem

Schmitta (tranzystory T5, T6). Układ przesuwania poziomu (tranzystor T7 i dioda D2) dopasowuje poziom

napięć pomiędzy wyjściem ukladu Schmitta, a układem wyjściowym bramki.

Najważniejszą jednak cechą bramki z układem Schmitta jest jej histereza przyłączeniowa. Zwykła bramka nie

ma takiej histerezy. Bramka Schmitta przełącza przy napięciu przełączania Up+ » 1,7V. Występujące w niej

dodatnie sprzężenie zwrotne zmniejsza sygnał wejściowy. Ale, aby bramka ponownie przełączała, napięcie

wejściowe musiałoby się zmniejszyć do wartości 0,9V, czyli aż o ok. 0,8V. Dzięki bowiem pętli histerezy próg

przełączania przy zboczu opadającym przebiegu wejściowego Up- to ok. 0,9V. Wynika, z tego, że napięcie

wejściowe może się długo utrzymywać na poziomie 1,7V i nie będzie to grozić wzbudzeniem bramki, jeśli

zawiera ona układ Schmitta.

Bramki z układem Schmitta są stosowane na wejściach układów cyfrowych współpracujących z sygnałami

wolnozmiennymi o parametrach (amplituda, stromość zboczy) wykraczających poza standard TTL. Sygnały o

standardzie TTL to takie, których szybkość narastania bądź opadania napięcia jest większa niż 1V/ms, a

amplituda zawiera się w granicach 2-5V.

Duża stromość charakterystyki przełączania bramki Schmitta (rysunek 1.6.) w połączeniu z histerezą

przyłączeniową jest cechą korzystną i pożądaną, ponieważ pozwala uzyskać większe marginesy zakłóceń. Jest

to dodatkowa (poza odpornością na wzbudzanie się) zaleta tej bramki.

Symbol graficzny bramki z przerzutnikiem Schmitta przedstawiono na rysunku 1.7.

Rys. 1.7. Symbol graficzny bramki z przerzutnikiem Schmitta

1.1.6 Bramka typu otwarty kolektor (OC)

Schemat ideowy bramki z otwartym kolektorem (typu OC – ang. Open Colector) przedstawiono na rysunku

1.8.

Rys. 1.8. Schemat ideowy bramki z otwartym kolektorem (OC)

W stopniu wejściowym zastosowano, zgodnie z zasadą przyjętą dla całej serii LS, diodowy układ iloczynu.

Tranzystor T1 pracuje jako wtórnik wzmacniacza prądu, a tranzystor T2 stanowi wejściowy inwerter z

otwartym kolektorem.

Gdy wyjście F zostanie dołączone do napięcia zasilającego Ucc przez rezystor R, wówczas układ realizuje

funkcję NAND (F=AB). Bramka typu OC z dołączonym rezystorem nie różni się funkcjonalnie niczym od

bramki standardowej TTL NAND. Jej czas propagacji jest jednak znacznie dłuższy. Spowodowane jest to

(wydłużenie) ładowaniem pojemności obciążenia przez rezystor R.

Jedną z zalet bramek z otwartym kolektorem jest możliwość łączenia ze sobą ich wyjść. Z bramkami

standardowymi tak postępować nie wolno.

Układ pracy dwóch bramek typu OC z połączonymi wyjściami przedstawiono na rysunku 1.9. Takie

połączenie do wspólnego rezystora daje w efekcie iloczyn doprowadzanych sygnałów. A zatem AB

CD=AB+CD.

Rys. 1.9. Układ pracy dwóch bramek I-NIE typu OC z połączonymi wyjściami

Wartość rezystancji R0 wyznaczamy, gdy wyjścia bramek typu OC połączymy z wejściami bramek

sterowanych tej samej serii, czyli np. z bramkami Schmitta.

Układ połączeń przedstawiono na rysunku 1.10.

Rys. 1.10. Układ połączeń do wyznaczania rezystancji Rmax i Rmin

Liczba m bramek typu OC, których wyjścia będą ze sobą łączone, może być dowolna (mŁ10). Także liczba

wejść n sterowanych przez to wyjście (nŁ10). Dla każdej takiej konfiguracji (pary m, n) należy dobrać inną

wartość rezystora obciążającego R.

Wartość tej rezystancji powinna być tak dobrana, aby w stanie wysokim na wyjściu napięcie wyjściowe było

nie mniejsze niż UOH min=2,4V, natomiast w stanie niskim nie większe niż UOH max=0,4V. Pomiar tych

wartości umożliwia woltomierz.

Można także wyznaczyć tą rezystancję poprzez podstawienie do gotowych wzorów Rmax i Rmin w postaci:

Gdzie Ucc – napięcie zasilania,

UOH min –minimalne napięcie wyjściowe badanej serii układów ,

IIH max – maksymalny prąd wyjściowy w stanie wysokim bramek sterowanych (dla serii TTL – LS jest to 20

mA), IOL max – maksymalny prąd w stanie niskim bramek sterujących (dla serii TTL – LS jest to 18 mA),

IOH(OC) – największa wartość (gwarantowana przez producenta) prądu upływności tranzystorów wyjściowych

bramek sterujących (dla serii TTL – LS jest to 250 mA).

W praktyce często zachodzi konieczność współpracy różnych układów cyfrowych, których wyjścia są

połączone wspólnym przewodem – zwanym magistralą (szyną). Jednym ze sposobów umożliwiających taką

współpracę jest zastosowanie bramek z otwartym obwodem kolektora.

1.1.7 Bramka trójstanowa

Przyłączenie wyjść do wspólnej magistrali (szyny) umożliwiają również (poza bramkami OC) tzw. bramki

trójstanowe. Bramka trójstanowa, oprócz dwóch normalnych stanów (H, L) ma dodatkowy trzeci stan,

charaktryzujący się wielką impedancją wyjściową (wyłączenie bramki). Z tego powodu element taki posiada

dodatkowe wejście sterujące trybem jego pracy.

Schemat ideowy negatora z wyjściem trójstanowym przedstawiono na rysunku 1.11. a).

Rys. 1.11. Schemat ideowy bramki I-NIE z wyjściem trójstanowym (a), symbol graficzny (b)

Jeśli na wejściu sterującym B jest niski potencjał (stan L), to tranzystor T7, T8 układu sterującego są

zatkane i bramka zachowuje się jak zwykła bramka negacji. Jeżeli na wejściu sterującym poziom napięcia jest

wysoki (stan H), to tranzystory T7, T8 są w stanie nasycenia. W tej sytuacji dioda D jest spolaryzowana w

kierunku przewodzenia i na bazie tranzystora T5 występuje potencjał o wartości 0,9V, co sprawia, że

tranzystor T3 jest zatkany. Odcięte są również tranzystory T2, T4 ze względu na to, że na wejściu tranzystora

T1 połączony z punktem C poziom napięcia jest niski. W efekcie obydwa tranzystory (T3, T4) są w stanie

zatkania, co powoduje, że na wyjściu występuje nieokreślony stan charakteryzujący się dużą impedancją

wejściową. Tablicę stanów bramki trójstanowej przedstawiono w tablicy 1.1.

Tab. 1.1 Tablica stanów bramki z wyjściem trójstanowym

Stan (Z) oznacza stan wielkiej impedancji. Warto zauważyć, że bramka zachowuje się jak zwykła bramka

dwustanowa dla wejścia sterującego B=0, co można poznać po symbolu graficznym tej bramki.

Bramki trójstanowe mają dodatkowe parametry dynamiczne (po za takimi, jak dla bramek dwustanowych)

charakteryzujące ich działanie. Są to:

1. Czas zablokowania wyjścia (czas blokowania). Ponieważ blokowanie takiej bramki może nastąpić zarówno

w tedy, gdy znajduje się ona w stanie H, jak i w stanie L, rozróżnia się:

tHZ – czas zablokowania wyjścia przy przejściu ze stanu o poziomie wysokim do stanu wielkiej impedancji.

tLZ – czas zablokowania wyjścia przy przejściu ze stanu o poziomie niskim do stanu wielkiej impedancji.

2. Czas odblokowania wyjścia. Analogicznie jak dla stanu blokowania:

tZL – czas zablokowania wyjścia przy przejściu ze stanu wielkiej impedancji do stanu o poziomie niskim,

tZH – czas zablokowania wyjścia przy przejściu ze stanu wielkiej impedancji do stanu o poziomie wysokim.

Obwody bramek trójstanowych projektuje się tak aby czas blokowania bramki (przełączenia w stan wielkiej

impedancji) był krótszy od czasu jej otwierania (odblokowania), co jest istotne przy współpracy wielu bramek z

magistralą.

2 Badanie bramek specjalnych

2.1 Program ćwiczenia

Program ćwiczenia „Badanie bramek specjalnych” ma na celu poznanie szczególnych właściwości bramek z

przerzutnikiem Schmitta oraz z wyjściami typu OC (OD) i z wyjściami trójstanowymi.

Program ćwiczenia:

a)

-

Badanie bramki z przerzutnikiem Schmitta:

sprawdzenie odporności bramki na wzbudzanie się,

pomiar charakterystyki przejściowej,

wyznaczanie marginesów zakłóceń,

wyznaczanie napięć progowych,

pomiar czasu propagacji bramki Schmitta.

b) Badanie bramki z wyjściem typu OC (typu otwarty kolektor):

doświadczalna weryfikacja wzorów pozwalających na dobór rezystora dołączonego do wyjścia bramki,

sprawdzenie funkcji realizowanych przez kilka bramek z wyjściem typu OC pracujących na wspólny

rezystor.

c)

-

Badanie bramki z wyjściem trójstanowym:

doświadczalne określenia tablicy prawdy badanej bramki,

pomiar czasu propagacji od obu wejść (wyjścia danych, wyjścia sterującego),

pomiar czasu blokowania i odblokowania.

2.2 Przebieg pomiarów

2.3 Badanie bramki z przerzutnikiem Schmitta

2.3.1 Kształtowanie przebiegów TTL z przebiegów wolno zmiennych

Doprowadzić do wejścia bramki z przerzutnikiem Schmitta sygnał wolnozmienny. Może to być

wyprostowane (jedno lub dwupołówkowo) napięcie sieciowe, po uprzednim obniżeniu amplitudy tego napięcia

do wartości nie większej niż maksymalna wartość napięcia wyjściowego badanej bramki, albo przebieg

trójkątny o częstotliwości kilkunastu kilo herców. Zaobserwować na oscyloskopie obydwa przebiegi

(wejściowy i wyjściowy). Przerysować te przebiegi. Zanotować nastawy oscyloskopu. Powtórzyć powyższe

badania, zmieniając badaną bramkę na bramkę bez przerzutnika Schmitta.

Zwymiarować uzyskane przebiegi czasowe. Uzasadnić różnice występujące w przebiegach wyjściowych

badanych bramek.

2.3.2 Wyznaczanie charakterystyk przejściowych

Aby pomierzyć tę charakterystykę metodą oscyloskopową wystarczy w poprzednim układzie

pomiarowym przełączyć oscyloskop w tryb pracy X-Y. Narysować układ pomiarowy. Zanotować symbol

badanego układu.

Narysować charakterystykę. Wyznaczyć na jej podstawie napięcia progowe Up+ i Up- oraz marginesów

zakłóceń UL i UH.

2.3.3 Pomiar czasu propagacji bramki Schmitta

Narysować i połączyć układ do pomiaru czasu propagacji (Czas propagacji jest to czas, który jest

potrzebny na to żeby sygnał na wyjściu mógł dojść do stanu niskiego lub wysokiego). Narysować otrzymane

przebiegi czasowe oraz je zwymiarować. Określić na podstawie przebiegów wartości parametrów: tpHL i

tpLH. Otrzymane wyniki zanotować w tablicach. Zanotować symbol badanego układu.

Zamieścić w tablicy wartości czasów propagacji bramki tej samej serii co badana, ale nie zawierającej

przerzutnik Schmitta. Porównać te wartości. Ocenić.

Układ do wyznaczania charakterystyk przejściowych i pomiaru czasu propagacji przedstawiono na rys. 2.1.

jako wspólny dla całego ćwiczenia „Badanie bramek z przerzutnikiem Schmitta”.

Rys. 2.1. Układ do wyznaczania charakterystyk przejściowych i czasu propagacji bramki z przerzutnikiem

Schmitta.

2.4 Badanie bramki typu otwarty kolektor

2.4.1 Wyznaczanie Rmin, Rmax

Połączyć razem wyjścia m bramek typu OC, sterujących liczbą n wejść układów tej samej serii co bramki

sterujące (np. bramki z przerzutnikiem Schmitta). Narysować układ połączeń. Wykonać pomiary wartości

rezystancji Rmin, Rmax. Należy wyjścia bramek typu OC połączyć wejściami bramek z przerzutnikiem

Schmitta.

Obliczyć – korzystając ze wzorów (1.1) i (1.2.) – wartości teoretycznej rezystancji Rmin, Rmax. Sprawdzić,

czy zawierają się oe w przedziale wyznaczonym przez wartości zmierzone. Uzasadnić różnice między nimi.

Rys. 2.2. Układ do wyznacznia Rmin, Rmax

2.4.2 Realizacja funkcji logicznych z użyciem bramek OC

Zbudować układ składający się z dwóch dwuwejściowych bramek NAND typu OC do wspólnego

rezystora. Narysować układ. Wyznaczyć jego tablicę prawdy.

Znaleźć opis bulowski badanego układu. Porównać go z iloczynem logicznym funkcji realizowanych przez

poszczególne bramki. Określić postać kanoniczną badanego układu.

Rys. 2.3. Układ do realizacji funkcji logicznej z użyciem bramek typu OC

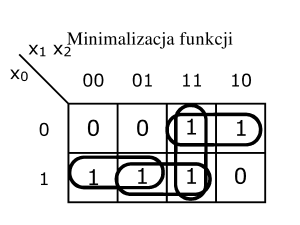

2.4.3 Realizacja zadanej funkcji logicznej z użyciem bramki OC

Zrealizować, używając bramek typu OC, funkcję logiczną opisaną kanoniczną postacią sumy (np.

następująco: f(d, c, b, a)= S[0, 1, 2, 5, 8, 9, 13, (6)]. Narysować układ, połączyć go i uruchomić. Sprawdzić jego

działanie.

2.5 Badanie bramki trójstanowej

2.5.1 Wyznaczanie tablicy prawdy bramki trójstanowej

Ustawiając na wejściach badanej bramki wszystkie możliwe kombinacje poziomów L i H zaobserwować

zachowanie się bramki (stan wyjścia). Zapisać tablicę prawdy.

Ustawić bramkę w stan dużej impedancji. Pomierzyć sygnał wyjściowy za pomocą próbnika stanów logicznych

oraz oscyloskopu. Zaobserwować, czy stan wejść ma jakikolwiek wpływ na wskazania obu przyrządów

pomiarowych, jeśli wyjście jest w stanie dużej impedancji.

Scharakteryzować pracę bramki w stanie wielkiej impedancji.

Rys. 2.4. Wyznaczanie tablicy prawdy bramki trójstanowej

2.5.2 Pomiar czasów blokowania i odblokowania

Narysować i połączyć układ do pomiaru czasów blokowania i odblokowania. Dobrać częstotliwość

przebiegu wejściowego tak, aby otrzymać przebiegi czasowe umożliwiające obserwację i pomiar tych czasów.

Dobarć i zanotować nastawy oscyloskopu:

Wzmocnienie i podstawa czasu. Narysować otrzymane przebiegi oraz je zwymiarować. Określić na podstawie

przebiegów czasy: tZL, tZH, tHZ, tLZ. Otrzymane wyniki zapisać w tablicy. Zanotować symbol badanego

układu.

Porównać czasy blokowania z czasami odblokowania.

Rys. 2.5. Układ do pomiaru czasu odblokowania i blokowania bramki trójstanowej

3 Opis Stanowiska pracy

3.1 Wykaz elementów użytych w ćwiczeniu

W ramach pracy dyplomowej zostały użyte następujące elementy:

·

·

·

-

Układy scalone:

bramka z przerzutnikiem Schmitta – UCY74LS132N

bramka typu otwarty kolektor (OC) – UCY74LS03N

bramka z wyjściem trójstanowym – UCY74LS366N

zwykła bramka standardowa – UCY7400N

Zasilacz:

transformator sieciowy TS6/B5 – 6,0V/1,3A

mostek prostowniczy – 2A

stabilizator – 7805

kondensatory elektrolityczne - 1000 mF/16V i 100nF/16V

tablica stanów:

przełączniki dwupołożeniowe

-

diody świecące

-

rezystory R=100 W

3.2 Schematy aplikacyjne układów scalonych badanych bramek

3.2.1 Bramka z przerzutnikiem Schmitta

Schemat aplikacyjny układu scalonego zawierającego bramki z przerzutnikiem Schmitta przedstawiono na

rysunku 3.1.

Rys. 3.1. Schemat aplikacyjny układu scalonego zawierającego bramki z przerzutnikiem Schmitta

Monolityczny układ scalony UCY74LS132N zawiera cztery dwuwejściowe bramki I-NIE z histerezą

napięcia wejściowego (bramki z przerzutnikiem Schmitta). Dzięki występującej histerezie napięć wejściowych

układy te znajdują szerokie zastosowanie w obwodach wejściowych kształtowania przebiegów impulsowych.

Układ scalony UCY74LS132N jest produkowany w obwodach plastikowych A49B(CE70).

3.2.2 Bramka typu otwarty kolektor

Monolityczny układ scalony UCY74LS03N zawiera cztery dwuwejściowe bramki I-NIE z otwartym

kolektorem serii małej mocy (LS). Bramki z tego układu charakteryzują się, znacznie dłuższym czasem

propagacji sygnału (32ns) w stosunku do bramki serii standardowej (15ns).

Schemat aplikacyjny układu scalonego zawierającego bramki typu otwarty kolektor przedstawiono na

rysunku 3.2.

Rys. 3.2. Schemat aplikacyjny układu scalonego zawierającego bramki typu otwarty kolektor

3.2.3 Bramka trójstanowa

Schemat aplikacyjny układu scalonego zawierającego bramki trójstanowe przedstawiono na rysunku 3.3.

Rys. 3.3. Schemat aplikacyjny układu scalonego zawierającego bramki trójstanowe

Monolityczny układ scalony UCY 74LS366N zawiera sześć inwerterów buforowych z wyjściem

trójstanowym.

W tym układzie wszystkie inwertery mają dwa wspólne wejścia uaktywniania 1OE i 2OE. Stan wysoki na

jednym lub na obu wejściach uaktywniania powoduje wystąpienie stanu dużej impedancji na wyjściu każdego

inwertera tego układu.

4

Przykłady pytań sprawdzających

1. Narysuj ch-ke przejściowa bramki Schmidta i zaznacz na niej napięcie przełączania oraz marginesy

zakłóceń.

2. Podaj symbol bramki z przerzutnikiem Schmidta.

3. Wymień serie układów scalonych TTL/

4. Podaj symbol i tablicę prawdy bramki NAND.

5. Narysuj układ połączeń, symbol graficzny i schemat zastępczy układu wejściowego iloczynowej bramki

TTL.

6. Narysuj ch-kę przejściową oraz ch-kę poboru prądu bramki NAND.

7. Podaj wzory na obliczanie Rmax i Rmin dla bramek OC oraz schemat połączeń do obliczania tych

wartości.

8. Podaj symbol i tablicę stanów bramki trójstanowej.

9. Opisz działanie bramki trójstanowej.

10. Narysuj układ do wyznaczania ch-ki przejściowej i czasu propagacji bramki Schmidta.

11. Narysuj układ do wyznaczania Rmin i Rmax. Dla bramek OC.

12. Podaj układ do pomiaru czasu blokowania i odblokowania bramki trójstanowej.

13. Opisz parametry dynamiczne bramki trójstanowej.