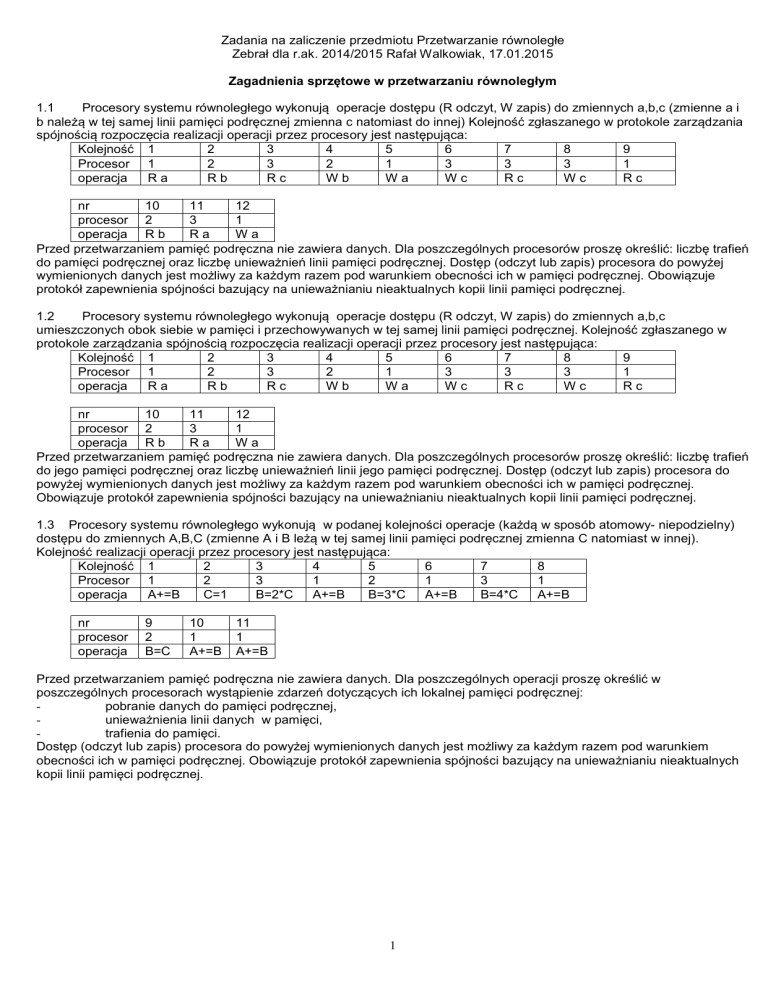

Zadania na zaliczenie przedmiotu Przetwarzanie równoległe

Zebrał dla r.ak. 2014/2015 Rafał Walkowiak, 17.01.2015

Zagadnienia sprzętowe w przetwarzaniu równoległym

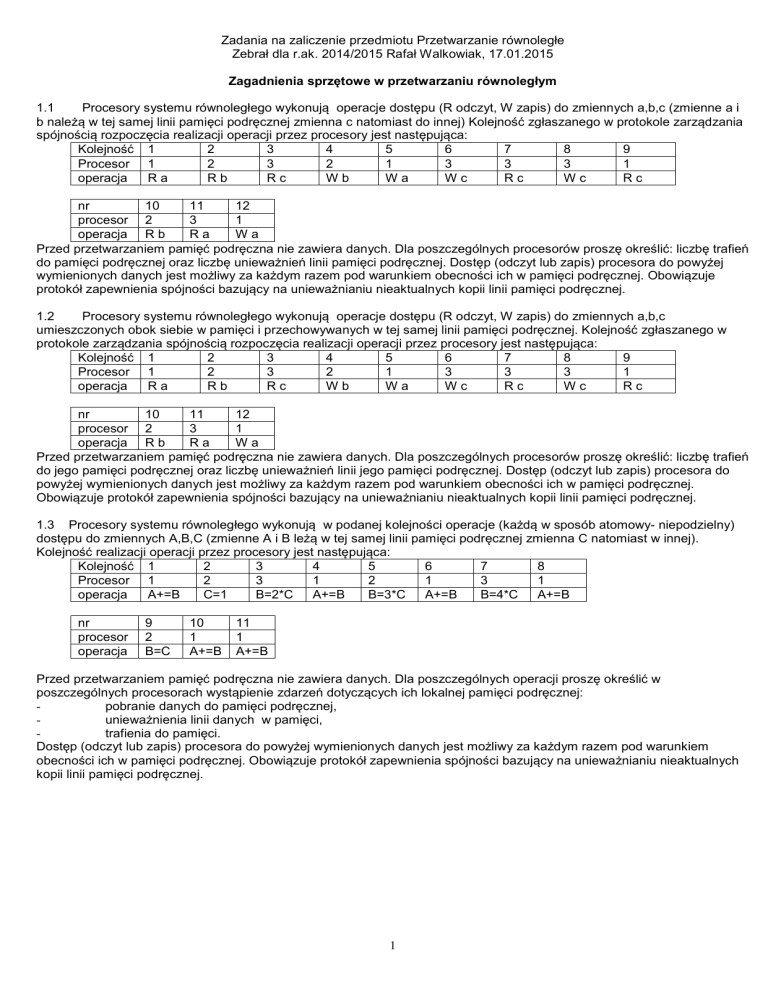

1.1

Procesory systemu równoległego wykonują operacje dostępu (R odczyt, W zapis) do zmiennych a,b,c (zmienne a i

b należą w tej samej linii pamięci podręcznej zmienna c natomiast do innej) Kolejność zgłaszanego w protokole zarządzania

spójnością rozpoczęcia realizacji operacji przez procesory jest następująca:

Kolejność 1

2

3

4

5

6

7

8

9

Procesor 1

2

3

2

1

3

3

3

1

operacja

Ra

Rb

Rc

Wb

Wa

Wc

Rc

Wc

Rc

nr

10

11

12

procesor 2

3

1

operacja R b

Ra

Wa

Przed przetwarzaniem pamięć podręczna nie zawiera danych. Dla poszczególnych procesorów proszę określić: liczbę trafień

do pamięci podręcznej oraz liczbę unieważnień linii pamięci podręcznej. Dostęp (odczyt lub zapis) procesora do powyżej

wymienionych danych jest możliwy za każdym razem pod warunkiem obecności ich w pamięci podręcznej. Obowiązuje

protokół zapewnienia spójności bazujący na unieważnianiu nieaktualnych kopii linii pamięci podręcznej.

1.2

Procesory systemu równoległego wykonują operacje dostępu (R odczyt, W zapis) do zmiennych a,b,c

umieszczonych obok siebie w pamięci i przechowywanych w tej samej linii pamięci podręcznej. Kolejność zgłaszanego w

protokole zarządzania spójnością rozpoczęcia realizacji operacji przez procesory jest następująca:

Kolejność 1

2

3

4

5

6

7

8

9

Procesor 1

2

3

2

1

3

3

3

1

operacja

Ra

Rb

Rc

Wb

Wa

Wc

Rc

Wc

Rc

nr

10

11

12

procesor 2

3

1

operacja R b

Ra

Wa

Przed przetwarzaniem pamięć podręczna nie zawiera danych. Dla poszczególnych procesorów proszę określić: liczbę trafień

do jego pamięci podręcznej oraz liczbę unieważnień linii jego pamięci podręcznej. Dostęp (odczyt lub zapis) procesora do

powyżej wymienionych danych jest możliwy za każdym razem pod warunkiem obecności ich w pamięci podręcznej.

Obowiązuje protokół zapewnienia spójności bazujący na unieważnianiu nieaktualnych kopii linii pamięci podręcznej.

1.3 Procesory systemu równoległego wykonują w podanej kolejności operacje (każdą w sposób atomowy- niepodzielny)

dostępu do zmiennych A,B,C (zmienne A i B leżą w tej samej linii pamięci podręcznej zmienna C natomiast w innej).

Kolejność realizacji operacji przez procesory jest następująca:

Kolejność 1

2

3

4

5

6

7

8

Procesor 1

2

3

1

2

1

3

1

operacja

A+=B

C=1

B=2*C

A+=B

B=3*C

A+=B

B=4*C

A+=B

nr

procesor

operacja

9

2

B=C

10

1

A+=B

11

1

A+=B

Przed przetwarzaniem pamięć podręczna nie zawiera danych. Dla poszczególnych operacji proszę określić w

poszczególnych procesorach wystąpienie zdarzeń dotyczących ich lokalnej pamięci podręcznej:

pobranie danych do pamięci podręcznej,

unieważnienia linii danych w pamięci,

trafienia do pamięci.

Dostęp (odczyt lub zapis) procesora do powyżej wymienionych danych jest możliwy za każdym razem pod warunkiem

obecności ich w pamięci podręcznej. Obowiązuje protokół zapewnienia spójności bazujący na unieważnianiu nieaktualnych

kopii linii pamięci podręcznej.

1

1.4

Procesory systemu równoległego wykonują w podanej kolejności instrukcje (każdą w sposób atomowyniepodzielny) korzystając ze zmiennych współdzielonych przetwarzanych wątków, zmienne oznaczono A,B,C (zmienne A i

C leżą w tej samej linii pamięci podręcznej natomiast każda zmienna B w innej linii). R1 i R2 oznaczają kolejne rejestry

każdego z procesorów. Kolejność realizacji operacji przez procesory jest następująca:

Kolejność

1

2

3

4

5

6

Procesor

1

2

1

2

1

2

operacja

R1=B

R1=C

R1=R1+1

B=R1

A=R1

C=2*R2

Przed przetwarzaniem pamięć podręczna nie zawiera danych. Dla poszczególnych operacji proszę określić w

poszczególnych procesorach wystąpienie zdarzeń dotyczących ich lokalnej pamięci podręcznej:

- unieważnienia linii pamięci podręcznej w pp poszczególnych procesorów,

- pobrań linii pamięci podręcznej danych do pp.

Dostęp (odczyt lub zapis) procesora do danych jest możliwy za każdym razem pod warunkiem obecności ich aktualnej

wartości w pamięci podręcznej. Obowiązuje protokół zapewnienia spójności bazujący na unieważnianiu nieaktualnych kopii

linii pamięci podręcznej, pamięć jest dowolnie duża.

1.5

Poniżej zapisano kolejne dostępy do pamięci współdzielonej zrealizowane przez 4 procesory P1- P4.

Procesory posiadają pamięć podręczną, w której powielone są przetwarzane dane. Odwołania do pamięci zapis i odczyt

dotyczą zawsze jednego słowa danych np. 1R(3) oznacza odczyt przez pierwszy procesor trzeciego kolejno słowa licząc od

początku wykorzystywanego obszaru. Wielkość linii pamięci podręcznej wynosi 4 słowa, a wykorzystywany obszar danych

jest wyrównany do początku linii pamięci podręcznej. Proszę określić stan i zawartość pamięci podręcznej procesorów po

wykonaniu wszystkich operacji. Ile nastąpiło trafień do pamięci podręcznej (które z 12 poniższych dostępów są trafieniami).

Obowiązuje protokół 3 stanowy unieważniania kopii zmodyfikowanych linii danych.

1R(3),2R(4),3R(7),1W(1),2W(2),4R(7),4W(5),4W(6),1R(2),3R(3),4R(11),1R(10)

1.6

System wieloprocesorowy posiada 8 procesorów korzystających z pamięci współdzielonej i prywatnych pamięci

podręcznych. Opóźnienie dostępu do danych w pp wynosi 5 cykli zegara procesora, a opóźnienie dostępu do danych w

przypadku potrzeby ściągnięcia danych z RAM wynosi 30 cykli zegara procesora. Rozmiar linii pp (wielkość danych

transmitowanych do pp) wynosi 4 słowa.

o

Jeden procesor realizuje obliczenia zgodnie z kodem zamieszczonym poniżej. Element tablicy a,b,c ma wielkość

jednego słowa. Jaki jest średni czas realizacji instrukcji dla jednego procesora jeśli byłby on ograniczony czasem dostępu

do pamięci?

o

Jak w równoległej realizacji pętli przez 8 procesorów systemu należy przydzielić iteracje pętli do poszczególnych

procesorów, aby efektywnie korzystać z pp ? Proszę wprowadzić odpowiednie dyrektywy Open MP i uzasadnić odpowiedź.

for (i=0;i<1024;i++) c[i]= a[i]*b[i];

1.7

Proszę określić stosunek trafień do pp w realizowanym przez 4 procesory równoległym algorytmie sumowania

elementów dwuwymiarowej tablicy (o rozmiarze 4k słów) zapisanej w pamięci współdzielonej. Suma częściowa jest zmienną

współdzieloną wątków, chronioną za pomocą zamka przed niepoprawnym uaktualnieniem. Każdy z procesorów sumuje 1k

słów z kolejnych różnych wierszy macierzy, a rozmiar linii pp wynosi 8 słów. Koszt realizacji zamka nie jest w uwzględniany

w analizie stosunku trafień. Pamięć podręczna jest wystarczająco duża. Elementy tablicy są zapisane kolejno wierszami.

Jaki byłby stosunek trafień, gdyby zastosowano zmienną lokalną do pamiętania sumy częściowej w każdym wątku

przetwarzania? Jakiego przyspieszenia można się spodziewać w wyniku zastosowania zaproponowanych powyżej metod

sumowania elementów tablicy?

1.8

Procesory systemu równoległego wykonują w następującej kolejności operacje dostępu (R odczyt, W zapis) do

zmiennych umieszczonych w obszarze danych należącym do tej samej linii pamięci podręcznej: P1 R, P2 W, P3 R, P1 R, P2

R, P3 W, P1 R, P2 R, P3 R, P2 W. Przed przetwarzaniem pamięć podręczna nie zawiera danych. Proszę określić stosunek

trafień, oddzielnie do pamięci podręcznej każdego procesora.

1.9

Rozważmy problem mnożenia tablicy przez tablicę metodą zagnieżdżonych pętli (kod poniżej) na komputerze z

pamięcią podręczną 80 KB o czasie dostępu 1ns i pamięcią RAM o czasie dostępu 100 ns. W przypadku braku danych w

pamięci podręcznej sprowadzane są one w podanym czasie z RAM w bloku równym rozmiarowi linii pp - 4 słów. Procesor

pobiera dane z pp. Tablica mnożona ma rozmiar 4Kx4K słów, a każdy wiersz tablicy zajmuje 16 KB. Jaka jest maksymalna

prędkość przetwarzania ograniczonego dostępem do pamięci? Proszę założyć optymalną strategię wykorzystania pamięci

podręcznej.

for (i=0; i<dim; i++)

for (j=0; j<dim;j++)

for (k=0; k<dim; k++)

C[i][j]+=a[i][k]*b[k][j];

2

1.10

Rozważmy problem mnożenia tablicy przez wektor metodą zagnieżdżonych pętli (kod poniżej) na komputerze z

pamięcią podręczną 16 KB o czasie dostępu 1ns i pamięcią RAM o czasie dostępu 50 ns. W przypadku braku danych w

pamięci podręcznej sprowadzane są one w podanym czasie z RAM w bloku równym rozmiarowi linii pp - 4 słów. Procesor

pobiera dane z pp. Tablica mnożona ma rozmiar 4Kx4K słów, a każdy wiersz tablicy zajmuje 16 KB. Jaka jest maksymalna

prędkość przetwarzania ograniczona czasem dostępu do pamięci –uwzględniamy tylko czas pobierania danych z pamięci,

gdyż zakładamy, że pozostałe operacje (obliczenia) realizowane są równocześnie (w tle) ? - jak długo (średnio) trwa czas

realizacji jednej instrukcji? Proszę założyć optymalną strategię wykorzystania pamięci podręcznej.

for (i=0; i<dim; i++)

for (k=0; k<dim; k++)

C[i]+=a[i][k]*b[k];

1.11

Maszyna SMP z rozproszoną przestrzenią adresową pamięci. Obliczenia ograniczone są prędkością dostępu do

pamięci - czas wykonywania instrukcji przez procesor biegnie równolegle z pobraniami danych z pamięci, czas pobierania

danych ma decydujący wpływ na prędkość przetwarzania. Zakładamy, że dla badanego kodu jedna instrukcja wymaga

średnio pobrania 1,5 słowa z pamięci.

Model dostępu do pamięci opisany następującymi parametrami:

–czas dostępu do danych w pamięci podręcznej (pp) – 10 ns

–czas dostępu do danych w przypadku konieczności odwołania do pamięci lokalnej węzła – 100 ns

–czas dostępu do danych w przypadku konieczności odwołania do pamięci zdalnej – 400 ns

Powyższe czasy zawierają wszystkie komponenty kosztów dostępu do danych w powyższych przypadkach niezależnie od

liczby wykorzystywanych do obliczeń procesorów. Dane procesor pobiera, po uzupełnieniu zawartości, zawsze

bezpośrednio z pp.

Przetwarzanie sekwencyjne kodu charakteryzuje stosunek trafień do pp 0.7.

Przetwarzanie współbieżne kodu na każdym z procesorów charakteryzuje następującymi stosunkami trafień: do pp 0.8, do

pamięci lokalnej 50% odwołań nieobsłużonych w pamięci podręcznej, pozostałe dane pobierane są z pamięci zdalnej.

Proszę porównać średnią prędkość przetwarzania (w MIPS) kodu na maszynie SMP (przy zachowaniu powyższych

parametrów): sekwencyjnie i równolegle na 4 procesorach. Ile razy przetwarzanie równoległe jest szybsze? Jak wyglądałaby

prędkość przetwarzania, gdyby stosunek trafień do pp był dwukrotnie mniejszy i brakujące dane musiałyby być pobrane z

pamięci lokalnej.

1.12

Dla maszyny o pamięci współdzielonej: koszt dostępu procesora do pp – Tc, koszt dostępu do pamięci systemowej –

ts, długość lini pamięci DLP, rozmiar pp PPS. Określić prędkość przetwarzania ograniczonego prędkością dostępu do

pamięci dla równoległego sumowania macierzy o rozmiarze NxN (kod w języku C) 4 procesory:

• KOD 1 Sumowanie elementów wierszami. Kolejne wiersze sumuje kolejny procesor

• KOD 2 Sumowanie elementów kolumnami. Kolejne kolumny sumuje następny procesor.

Proszę uwzględnić różne nietrywialnie scenariusze przetwarzania zależne od rozmiaru macierzy.

1.13

Rozważmy realizację przez 8 procesorów równoległego algorytmu sumowania elementów dwuwymiarowej tablicy A

(o rozmiarze 8k słów) zapisanej w pamięci współdzielonej. Każdy procesor odwołuje się do jednego (każdy innego) z

elementu współdzielonej tablicy B 8 elementowej w celu zapisania sumy częściowej. Każdy z procesorów sumuje 1k słów z

kolejnych różnych wierszy macierzy, a rozmiar linii pamięci podręcznej (pp) każdego procesora wynosi 8 słów. PP jest

wystarczająco duża. Elementy tablicy są zapisane kolejno wierszami. Po zakończeniu obliczeń procesy docierają do bariery

synchronizacyjnej po czym jeden proces sumuje wartości tablicy sum częściowych. Zakładamy, że dostęp do pamięci

podręcznej jest 40 razy szybszy od dostępu w przypadku braku trafienia do pamięci podręcznej (dowolnego typu pobrania

danych). Czas obliczeń jest zdominowany czasem dostępu do pamięci, dostępy do różnych lokacji pamięci przez różne

procesory są realizowane współbieżnie. Procesor nie realizuje równolegle dostępów do pamięci. Zakładając, że w systemie

realizowany jest protokół zapewnienia spójności pamięci podręcznej proszę określić pesymistyczny stosunek trafień i

pesymistyczną wartość przyspieszenia (względem realizacji tych obliczeń na jednym procesorze).

1.14

Rozważmy problem mnożenia tablicy przez tablicę metodą zagnieżdżonych pętli (kod poniżej) na komputerze 16

procesorowym z współdzieloną pamięcią. Podział pracy bazuje na podziale danych wyjściowych. Każdy procesor posiada

pamięć podręczną o wielkości 512 KB. W przypadku braku danych w pamięci podręcznej sprowadzane są one z pamięci

operacyjnej w bloku równym rozmiarowi linii pp – 128 B. Procesor pobiera dane tylko z pp. Tablica mnożona ma rozmiar

512x512 słów, a każdy wiersz tablicy zajmuje 2kB. Kod jest napisany w języku C. Proszę założyć optymalną strategię

wykorzystania pamięci podręcznej (jeżeli mamy wybór to usuwamy te dane, które nie będą potrzebne).

Proszę uzasadnić jaki efektywny podział pracy między procesory należy zaproponować?

Proszę określić i uzasadnić stosunek trafień do pamięci podręcznej i rozmiar danych pobieranych z pamięci głównej

przez każdy z procesorów w trakcie realizacji przedzielonej mu pracy. W jakiej kolejności procesory powinny realizować

przydzieloną im pracę.

//sekwencyjny kod mnożenia tablic

for (i=0; i<dim; i++)

for (j=0; j<dim;j++)

for (k=0; k<dim; k++)

3

C[i][j]+=a[i][k]*b[k][j];

1.15

Rozważmy problem mnożenia tablicy przez wektor metodą zagnieżdżonych pętli (porównaj kod poniżej) w

komputerze wieloprocesorowym z współdzieloną pamięcią operacyjną i prywatnymi pamięciami podręcznymi. W przypadku

braku danych w pamięci podręcznej sprowadzane są one z pamięci operacyjnej w bloku równym rozmiarowi linii pp.

Procesor pobiera dane z pp. Tablica a ma rozmiar n X n słów. Proszę podać i uzasadnić sposób zrównoleglenia

przetwarzania na 4 procesorach za pomocą dyrektyw Open MP uwzględniając następujące fakty:

Ilość pracy dla kolejnych iteracji pętli zewnętrznej zmienia się, gdyż tablica a zawiera na przekątnej i poniżej

przekątnej tylko zera,

w linii pamięci podręcznej mieszczą się 4 słowa,

pamięć podręczna ma rozmiar 3n,

optymalizacja zrównoleglenia powinna minimalizować czas przetwarzania zadania przez system.

for (i=0; i<n; i++)

{ C[i]=0;

for (k=0; k<n; k++) if (a[i][k]) C[i]+=a[i][k]*b[k];

}

Dla przyjętego rozwiązania proszę przeanalizować (przypadek optymistyczny) odwołania do pamięci dla elementów tablicy

a. Następnie proszę oszacować i wyjaśnić dla tej tablicy stosunek trafień do pamięci podręcznej w ramach jednego

procesora.

1.16

Wymienić 3 kategorie braków trafień do pamięci podręcznej i podać możliwe drogi ich usunięcia.

Określić co oznaczają i w jaki sposób można wyznaczyć następujące miary jakości przetwarzania:

• Wskaźnik (rate) braku trafień do bufora translacji adresów danych

- DTLB

• Wskaźniki IPC i CPI

• Stosunek trafień do pamięci podręcznej L2 (hit ratio), wskaźnik braku trafień do pamięci L1(miss rate)

• Przyspieszenie przetwarzania równoległego dla implementacji algorytmu równoległego A

• Koszt zrównoleglenia dla przetwarzania równoległego implementacji algorytmu równoległego A

1.17

Za pomocą wyników profilowania bazującego na zdarzeniach wyznaczono dla badanego programu następujące

wielkości:

- A- liczbę instrukcji,

- B- liczbę dostępów do pamięci danych,

- C- liczbę trafień do pamięci podręcznej danych,

- D - liczbę trafień do bufora translacji adresów danych,

- E- liczbę cykli procesora.

Proszę zdefiniować poniższe miary efektywności i określić ich wartość za pomocą pomierzonych wielkości:

- IPC

- stosunek trafień do pamięci podręcznej danych,

- wskaźnik braku trafień do bufora translacji adresów.

Na podstawie funkcjonalności programu oceny jakości przetwarzania - Code Analyst proszę porównać cele stosowania i

ograniczenia profilowania kodu bazującego:

1)

na zdarzeniach,

2)

na operacjach procesora i

3)

na upływie czasu.

4

Algorytmy i środowiska równoległe (open OMP)

2.1

Podać prezentowany na wykładzie algorytm znajdowania liczb pierwszych w łańcuchu procesorów. Określić: wejście

systemu, algorytm realizowany przez poszczególne procesory, zaproponować sposób uzyskiwania wyników na wyjściu

systemu, uzasadnić liczbę procesorów niezbędnych do znalezienia liczb pierwszych z zakresu od 950-X, określić

przybliżoną liczbę następujących po sobie (w najgorszym przypadku) operacji dzielenia w ramach tych obliczeń

(wskazówka: założyć, że X okaże się liczbą pierwszą).

2.2

Podać prezentowany na wykładzie algorytm znajdowania liczb pierwszych w łańcuchu procesorów. Określić: wejście

systemu, algorytm realizowany przez poszczególne procesory, zaproponować sposób uzyskiwania wyników na wyjściu

systemu, uzasadnić liczbę procesorów niezbędnych do znalezienia tym algorytmem liczb pierwszych z zakresu od 100 - 130,

określić złożoność przetwarzania równoległego w najgorszym wypadku mierzoną za pomocą liczby następujących po sobie

(w najgorszym przypadku) operacji dzielenia.

2.3

Proszę wyjaśnić liczbę kolejnych kroków oraz pracę realizowaną w przedstawionym na wykładzie równoległym

algorytmie sumowana w hiperkostce 16 procesorowej z wynikiem w każdym węźle. Każdy procesor posada n liczb

podlegających sumowaniu.

2.4

Podać prezentowany na wykładzie algorytm (i wyjaśnić jego złożoność) sumowania liczb z udostępnieniem wyniku

we wszystkich procesorach w systemie o architekturze pierścienia jednokierunkowego.

2.5

Podać prezentowany na wykładzie algorytm sortowania n liczb w łańcuchu procesorów. Określić:

algorytm realizowany przez poszczególne procesory,

sposób uzyskiwania wyników,

uzasadnić liczbę procesorów niezbędnych do poprawnego sortowania n liczb,

podać i wyjaśnić przybliżoną (z dokładnością do stałej) liczbę następujących po sobie operacji porównania.

2.6

Proszę przedstawić równoległy algorytm Cannona mnożenia macierzy kwadratowych w systemach z pamięcią

rozproszoną.

Należy określić sposób dystrybucji danych wejściowych, wyniku, naszkicować kod algorytmu dla poszczególnych

procesorów, określić rodzaj wykorzystywanych komunikacji - synchroniczna, asynchroniczna, buforowana, niebuforowana,

dla każdego procesora proszę określić rozmiar przetwarzanych danych oraz wymagania pamięciowe algorytmu w funkcji

rozmiaru macierzy n i liczby procesorów p.

2.7

Proszę przedstawić algorytm mnożenia macierzy kwadratowych metodą zagnieżdżonych 6 pętli w systemach z

pamięcią współdzieloną . Proszę założyć, że przetwarzanie równoległe bazuje na podziale pracy w pętli zewnętrznej

(#pragma omp parallel for) Proszę:

• wyjaśnić liczbę iteracji poszczególnych pętli algorytmu,

• podać ogólną zależność na ilość danych przetwarzanych przez każdy procesor,

• podać ogólną zależność na liczbę danych pobieranych do prywatnej pamięci podręcznej przez poszczególne

procesory.

2.8

Porównać fazy przetwarzania (zadania kolejnych pętli) w równoległym mnożeniu macierzy w metodach:

- 6 pętlowej dla komputera wieloprocesorowego z pamięcią współdzieloną (zrównoleglenie na poziomie pętli zewnętrznej) –

podejście zoptymalizowane

- 4 pętlowej (metoda Cannona) w systemie komputerowym z pamięcią rozproszoną.

Zakładając kolejność pętli i,j,k oraz dostęp do wyniku za pomocą odwołania C[i][j] proszę określić czy występuje lokalność

dostępów do poszczególnych tablic w obu metodach.

2.10

Proszę wyjaśnić problematyczne dla poprawnej i efektywnej równoległości przetwarzania elementy w poniższym

kodzie. Jakiego typu są to zagrożenia (jeśli dla tego kodu występują) ? Jak poszczególne zagrożenia można usunąć i

dlaczego? Potencjalne typy zagrożeń to: wyścig, dostęp do danych nielokalny czasowo lub dostęp do danych nielokalny

przestrzennie (przy jakiej wielkości pamięci podręcznej brak lokalności wystąpi), niezamierzone współdzielenie - false

sharing. Proszę określić których tablic dotyczą i jakie są danego zagrożenia konsekwencje? Proszę określić czy program

umożliwia deterministyczne przetwarzanie równoległe.

float a[N][N], b[N][N], c[N][N];

…

for (i = 0 ; i < N ; i++)

#pragma omp parallel for schedule(static,5)

for (int k = 0 ; k < N ; k++)

for (int j = 0 ; j < N ; j++) c[i][j] += a[i][k] *b[k][j] ;

5

2.11

Proszę wyjaśnić problematyczne dla poprawnej i efektywnej równoległości przetwarzania elementy w poniższym

kodzie.. Jakiego typu są to zagrożenia (jeśli dla tego kodu występują) ? Jak poszczególne zagrożenia można usunąć i

dlaczego? Potencjalne typy zagrożeń to: wyścig, dostęp do danych nielokalny czasowo lub przestrzennie, niezamierzone

współdzielenie- false sharing, proszę określić których tablic dotyczą i jakie są danego zagrożenia konsekwencje?

float a[N][N];

…..

int i,j,k;

#pragma omp parallel for schedule(dynamic,1)

for (i = 0 ; i < N ; i++) {

for (k = 0 ; k < N ; k++) {

for (j = 0 ; j < N ; j++) {

c[i][j] += a[i][k] *b[k][j] ;

}}}

2.12

Proszę wyjaśnić problematyczne dla poprawnej i efektywnej równoległości przetwarzania elementy w poniższym

kodzie. Jakiego typu są to zagrożenia (jeśli dla tego kodu występują) ? Jak poszczególne zagrożenia można usunąć i

dlaczego? Potencjalne typy zagrożeń to: wyścig, dostęp do danych nielokalny czasowo lub dostęp do danych nielokalny

przestrzennie, niezamierzone współdzielenie - false sharing,

proszę określić których tablic dotyczą i jakie są danego

zagrożenia konsekwencje?

float a[N][N];

#pragma omp parallel

for (j = 0 ; j < N ; j++) {

for (int i = 0 ; i < N ; i++) {

#pragma omp for schedule(dynamic,1)

for (int k = 0 ; k < N ; k++) {

c[i][j] += a[i][k] *b[k][j] ;

}}}

2.13

Proszę wyjaśnić jaką pracę wykonają poszczególne wątki w czasie realizacji poniższego kodu (proszę

założyć wykonanie kodu przez 4 wątki). Z jakim rodzajem lokalności dostępu do danych potencjalnie powielonych w

pamięciach podręcznych procesorów mamy do czynienia w kodzie. Jakie są warunki lokalności dostępu. Proszę założyć

wyrównanie początku każdego wiersza tablicy do początku linii pamięci podręcznej.

float a[N][N], b[N][N], c[N][N];

…

for (int i = 0 ; i < N ; i++) {

#pragma omp parallel

for (int k = 0 ; k < N ; k++)

#pragma omp for schedule(static,block)

for (int j = 0 ; j < N ; j++)

c[i][j] += a[i][k] *b[k][j]; }

2.14

W każdym z poniższych trzech przykładów kodu proszę wyjaśnić ile razy i z jakim parametrem istniejący wątek o

identyfikatorze równym 1 będzie realizował wywołania Funkcja1.

------------------------------------------------------------------omp_set_num_threads(m);

#pragma omp parallel for schedule (static)

for (j=0; j<n;j++)

Funkcja1(j) ;

------------------------------------------------------------------

------------------------------------------------------------------omp_set_num_threads(m);

#pragma omp parallel

for (j=0; j<n;j++)

Funkcja1(j) ;

2.15

Proszę omówić dostępne w ramach OpenMP dyrektywy:

A.

podziału pracy na wątki - single, master, for, section, task. Proszę określić ich znaczenie i warianty tych dyrektyw oraz

porównać zakres stosowania tych wariantów.

B.

Czym różni się dyrektywa critical od atomic, proszę zaprezentować przykład ich zastosowania.

2.16

Korzystając z dyrektyw Open MP proszę zapisać kod w meta języku pozwalający na równoległe sumowanie N

elementowej

tablicy jednowymiarowej na dowolnej liczbie P procesorów. Proszę określić jeśli to możliwe dla przygotowanego kodu

jaką pracę wykonają poszczególne procesory. Proszę omówić kluczowe dla efektywności przetwarzania elementy kodu.

Wynik będący sumą ma zostać wyświetlony na ekranie.

6

2.17

Proszę omówić algorytm znajdowania maksimum w zbiorze N liczb dla CRCW PRAM. Proszę określić:

liczbę maszyn,

liczbę kroków przetwarzania,

uzasadnić poprawność obliczeń w przypadku wielu równych wartości maksymalnych i

zastosowaną strategię zapisu i uzasadnić poprawność jej realizacji dla każdego zapisu w kodzie.

2.18 Proszę zaproponować algorytm dla modelu maszyny równoległej typu CRCW PRAM z jednorodną strategią zapisu dla

problemu:

sprawdzania czy liczba N podana na wejściu komputera jest liczbą pierwszą.

Program ma dać odpowiedź w czasie stałym niezależnym od wartości liczby: np. tak dla liczby 7, nie dla liczby 121. Proszę

założyć, że interesują nas liczby N, których czas dzielenia przez dowolną inną liczbę jest stały. W szczególności proszę:

określić minimalna liczbę procesorów niezbędnych do przeprowadzenia obliczeń wg podanego kodu,

określić liczbę kroków przetwarzania,

określić liczbę procesorów uczestniczących w poszczególnych krokach przetwarzania i

uzasadnić poprawność zastosowanej strategii zapisu dla każdego występującego w kodzie kroku zapisu komórki

danych.

Przesyłanie komunikatów

3.1

Jaki jest możliwy (czy zawsze jednakowy) efekt realizacji poniższego kodu przez procesy w trybie SPMD w

zależności od rodzaju (1. blokujące, 2. Nieblokujące z buforami ) zastosowanych wywołań:

•Send(void *sendbuf, int nelems, int dest,…)

•Receive(void *recvbuf, int nelems , int source,…)

Proszę wyjaśnić odpowiedź i opisać sytuację - kiedy określony efekt nastąpi.

//KOD procesów

I=zwracam_identyfikator_wywołującego_procesu();/* 0,1,2,3,....*/

N=zwracam_liczbe_procesow();

A=I;

Send(&A,1, (I+1)mod N,…);

Receive(&A,1, (I+N-1)mod N,…);

printf(‘’zrealizowano przeslanie od %d do %d \n’’,A,I);

Krótko odpowiedzieć na pytanie: jak można zmodyfikować powyższy kod, aby umożliwić realizację wszystkich komunikacji

zgodnie ze specyfikacją w kodzie (przy użyciu poszczególnych typów wywołań) przed wypisaniem komunikatów na ekranie?

3.2

Operacje komunikacji w przesyłaniu komunikatów, a ukrywanie kosztów komunikacji (uwzględnić funkcje blokujące,

nieblokujące, z buforami i bez)– dokonać porównania.

Szeregowanie i równoważenie obciążenia procesorów

4.1 Załóżmy, że M zadań ma być przydzielonych do p procesorów za pomocą scentralizowanego dynamicznego

schematu równoważenia obciążenia. Czasy przetwarzania zadań nie są znane z góry. Dostępne są tylko informacje

ogólne dotyczące zbioru zadań: średni czas przetwarzania jednego zadania jest równy scz, minimalny czas

przetwarzania jednego zadania jest równy mincz, maksymalny czas przetwarzania jednego zadania jest równy maxcz,

koszt/czas pobierania zadania/zadań przez proces wynosi KS. Proszę obliczyć przyspieszenie przetwarzania na p

procesorach dla algorytmów:

• samoszeregowania (ang. self-scheduling) i

• szeregowania w oparciu o pakiety wielozadaniowe – k zadań przydzielanych jednocześnie jednemu procesorowi

(ang.chunk scheduling).

Przykład dynamicznego self-scheduling to szeregowanie pojedynczo niezależnych iteracji pętli pobieranych przez

proces na bieżąco do realizacji po zakończeniu realizacji poprzedniej iteracji.

ANALIZĘ ( OBLICZENIA WARTOŚCI PRZYSPIESZENIA) NALEŻY WYKONAĆ W 2 WERSJACH: W NAJLEPSZYM I

NAJGORSZYM PRZYPADKU DLA OBU SCHEMATÓW DYNAMICZNEGO SZEREGOWANIA.

4.2 Drzewo binarne D z 8 liściami określa pełny schemat sekwencyjnego poszukiwania rozwiązania zgodnie z algorytmem

przeszukiwania w głąb począwszy od lewej strony drzewa. Poszukiwane rozwiązanie znajduje się w piątym liściu (zielony)

od lewej strony – po jego znalezieniu obliczenia są kończone. Przejście w grafie wzdłuż jednego łuku do niższego węzła

7

zajmuje jednostkę czasu przetwarzania , powrót nie wymaga czasu. Na znalezienie rozwiązania sekwencyjnie potrzeba

zatem (wg tutaj opisanej metody) 10 jednostek czasu.

Przetwarzanie realizowane współbieżnie polega wpierw na wyznaczeniu sekwencyjnym węzłów 2 poziomu (czerwone) –

zajmuje to czas równy 2 jednostki a następnie na przetwarzaniu równoległym na 2 procesorach poddrzew rozpoczynających

się w wyznaczonych węzłach (czerwonych).

Proszę określić możliwe do uzyskania przyspieszenie, czy jest to anomalia – jeśli tak to dlaczego i czym jest ona

spowodowana. Jaka jest inna możliwa przyczyna tego typu anomalii?

8

Efektywność przetwarzania współbieżnego

5.1

Przetwarzanie równoległe w systemie z przekazywaniem komunikatów ma charakteryzować się stałą efektywnością.

Obliczenia dotyczą wyznaczenia w korzeniu drzewa binarnego procesorów sumy N elementów (rozproszonych równomiernie

w p procesorach tworzących to drzewo). Proszę określić jak musi się zmienić N przy wzroście liczby procesorów z 7 na 15.

Czas komunikacji jest 5 razy dłuższy od czasu sumowania. Proszę założyć efektywne wykorzystanie komunikacji

nieblokującej.

5.2

W systemie z pamięcią współdzieloną proszę porównać prędkość przetwarzania w GFLOPS dla obliczeń, których

prędkość jest ograniczona czasem dostępu do pamięci:

A.

sumowanie kolejnych komórek pamięci zawierających elementy MxM elementowej macierzy,

B.

mnożenie macierzy o wymiarach MxM metodą 3 zagnieżdżonych pętli (kolejność zagnieżdżenia - i,k,j

c[i][j]+=a[i][k]*b[k][j];)

Rozmiar pamięci podręcznej jest równy 3M, a rozmiar linii pamięci podręcznej wynosi 64B czyli 16 słów. Czas dostępu do

pamięci podręcznej wynosi jeden cykl procesora, natomiast pobranie linii do pamięci podręcznej z pamięci operacyjnej trwa

50 cykli.

5.3

Proszę wyznaczyć funkcję stałej efektywności dla sumowania z wynikiem w każdym z węzłów przetwarzających M

n

liczb rozproszonych w kostce o liczbie procesorów równej 2 . Proszę założyć efektywną komunikację nieblokującą asynchroniczną i koszt przesłania jednego słowa danych między sąsiednimi węzłami równy 5A, koszt sumowania dwóch

liczb jest równy A.

5.4

Proszę wyznaczyć funkcję stałej efektywności dla sumowania z wynikiem w każdym z węzłów N liczb rozproszonych

w pierścieniu P procesorów. Proszę założyć koszt komunikację blokującą i koszt przesłania jednego słowa danych między

sąsiednimi węzłami równy 5A, koszt sumowania dwóch liczb jest równy A.

5.5

Graf zadań (liczba zadań = 15) ma strukturę drzewa binarnego o łukach skierowanych w kierunku korzenia drzewa.

Łuki oznaczają zależności kolejnościowe i komunikacje.

Obliczenia każdego zadania mają jednakowy koszt.

Obliczenia każdego zadania mają koszt dwukrotnie większy niż minimalny koszt komunikacji między zadaniami.

Globalny czas trwania wszystkich obliczeń w przetwarzaniu równoległym jest równy czasowi obliczeń

sekwencyjnych.

Proszę dokonać przydziału zadań do komputera równoległego o architekturze łańcucha.

W przypadku przydziału wielu zadań do jednego procesora koszt komunikacji między tymi zadaniami jest równy zero.

Proszę dokonać przydziału zadań do procesorów minimalizując przeciążenie i maksymalizując równoległość.

Ewentualne przeciążenie łącza powoduje liniowy wzrost czasu komunikacji przeciążonym łączem.

Koszt komunikacji między zadaniami (po przydziale) jest liniowo zależny od odstępu dla tej komunikacji. Proszę

określić maksymalne wartości: odstępu, przeciążenia i powiększenia dla zaproponowanego rozwiązania.

Proszę wyznaczyć przyspieszenie dla przetwarzania realizowanego zgodnie z zaproponowanym przydziałem zadań.

Proszę określić wpływ rodzaju komunikacji: synchroniczna, asynchroniczna na efektywność obliczeń.

5.6

Graf zadań (liczba zadań >= 15) ma strukturę drzewa binarnego o łukach skierowanych w kierunku korzenia drzewa.

Łuki oznaczają zależności kolejnościowe i komunikacje.

Obliczenia każdego zadania mają jednakowy koszt.

Obliczenia każdego zadania mają koszt dwukrotnie większy niż minimalny koszt komunikacji między zadaniami.

Globalny czas trwania wszystkich obliczeń w przetwarzaniu równoległym jest równy czasowi obliczeń

sekwencyjnych.

Proszę dokonać przydziału zadań do komputera równoległego o architekturze kostki 3 wymiarowej.

W przypadku przydziału wielu zadań do jednego procesora koszt komunikacji między tymi zadaniami jest równy zero.

Proszę dokonać przydziału zadań do procesorów minimalizując maksymalne przeciążenie. Ewentualne przeciążenie

łącza powoduje liniowy wzrost czasu komunikacji tym łączem.

Koszt komunikacji między zadaniami (po przydziale) jest liniowo zależny od odstępu dla tej komunikacji. Proszę

określić maksymalne wartości: odstępu, przeciążenia i powiększenie dla zaproponowanego rozwiązania.

Proszę wyznaczyć przyspieszenie dla przetwarzania realizowanego zgodnie z zaproponowanym przydziałem zadań.

5.7

Proszę wyznaczyć efektywność obliczeń polegających na sumowania N liczb rozproszonych równomiernie w systemie

wielokomputerowym o architekturze 3 wymiarowej kostki. Wynikiem przetwarzania i komunikacji ma być udostępnienie

9

wartości będącej sumą liczb w każdym z 8 węzłów obliczeniowych. Proszę założyć komunikację nieblokującą i koszt

przesłania jednego słowa danych między sąsiednimi węzłami równy 2A, koszt sumowania dwóch liczb jest równy A.

5.8 Wyznaczanie

w korzeniu drzewa procesorów sumy n elementów rozproszonych w p procesorach. Proszę wyznaczyć

funkcję stałej efektywności przy założeniu, że koszt komunikacji między sąsiednimi procesorami jest dany wzorem ts+

mdtw gdzie m jest liczbą słów komunikatu, d odległością, a t i t stałymi równymi 1. Koszt dodawania wynosi 4. Proszę

podać wzór określający ile razy musi wzrosnąć n, aby uzyskać stałą efektywność przy wzroście wysokości drzewa

procesorów o jeden poziom z 6 na 7. Proszę założyć komunikację asynchroniczną.

5.9

Niech nproc będzie zmienną przechowującą liczbę procesorów w systemie pomniejszoną o 1. Dany jest następujący

algorytm sortowania przez scalanie, który sortuje elementy pewnej tablicy począwszy od elementu o indeksie lewy do

elementu o indeksie prawy:

sort(lewy, prawy)

{

if (lewy == prawy) return;

srodek = (lewy + prawy) / 2;

if (nproc > 0) { nproc--; wykonaj sort(lewy, srodek) w nowym watku; }

else sort(lewy, srodek);

sort(srodek+1, prawy);

synchronizuj_watki();

merge(lewy, prawy)

}

Jeżeli przyjmiemy n=prawy-lewy+1 (czyli n to liczba elementów na których operują funkcje sort i merge), to zakładamy że:

Wykonanie funkcji sort na jednym procesorze trwa n*log2(n) jednostek czasu (wliczając wszystkie wywoływane przez

nią rekurencyjnie funkcje sort i merge).

Wykonanie funkcji merge, która łączy ciągi posortowane przez funkcję sort, na jednym procesorze trwa n jednostek

czasu.

Czas wykonania pozostałych instrukcji (np. warunek, dekrementacja nproc) można pominąć.

Nie wystąpi problem związany z dostępem do zmiennej nproc jednocześnie z więcej niż jednego wątku.

Funkcja synchronizuj_watki, czeka aż oba wątki sortujące zakończą swoje działanie, jeżeli nproc pozwoliło na

utworzenie kolejnego wątku.

Odpowiedz na poniższe pytania zakładając, że liczba procesorów, na komputerze na którym wykonywany jest

algorytm, wynosi 4:

Podaj wzór na przyspieszenie powyższego algorytmu w zależności od n. Jeżeli w zależności od przebiegu wykonania

programu przyspieszenie może być różne, opisz rozważany przypadek i podaj dla niego wzór.

Oblicz przyspieszenie dla sortowania n=64 (przyspieszenie możesz podać jako nieskrócony ułamek zwykły).

Czy jeżeli zwiększymy liczbę elementów to przyspieszenie zwiększy się?

5.10

Część obliczeń nie podlegająca zrównolegleniu zajmuje 20% czasu obliczeń realizowanych sekwencyjnie.

A) Jaka liczba procesorów zapewni wg prawa Amdahla uzyskanie przyspieszenia równego 4 ?

B) Zauważono dodatkowo, że użycie 4 procesorów udostępnia systemowi większą (niż w przypadku jednego identycznego

procesora) ilość pamięci podręcznej. Powoduje to wzrost stosunku trafień do pp . W wyniku tego faktu następuje wzrost

wydajności przetwarzania procesora i przydzielone obliczenia (realizowane współbieżnie) wykonuje on w czasie o 10 %

krótszym w stosunku do czasu realizacji tych obliczeń w sposób sekwencyjny.

Czy spowoduje to uzyskanie ponad liniowego przyspieszenia ? Odpowiedź uzasadnij.

5.11

Realizując przetwarzanie zadania A na 9 procesorach uzyskano 5 krotne przyspieszenie. Stosując prawo Amdahla

podaj liczbę procesorów niezbędnych do uzyskania 10 krotnego przyspieszenia. Jakie przyspieszenie uzyskano by, gdyby ze

wzrostem liczby procesorów liniowo (zgodnie z założeniami dla prawa Gustafsona) wzrastała wielkość części zadania

podlegającej zrównolegleniu.

5.12

W wyniku 3 krotnego uruchamiania pewnego kodu na różnej liczbie procesorów (5, 10 i 20 dostępnych na

wyłączność) stwierdzono, że za każdym razem czas przetwarzania jest w przybliżeniu jednakowy i wynosi 10 sekund. Co

można powiedzieć o efektywności przetwarzania i koszcie zrównoleglenia dla poszczególnych uruchomień? Czy informacje o

rozmiarze danych wejściowych mają znaczenie dla odpowiedzi na postawione pytanie? Jeżeli tak to proszę rozważyć 2

przypadki, w których sekwencyjny czas przetwarzania:

byłby dla wszystkich danych wejściowych jednakowy i wynosił 20 sekund lub

wynosiłby odpowiednio dla poszczególnych wykorzystanych danych 60, 80 i 160 sekund.

Czy uzyskane wartości parametrów jakości przetwarzania mają sens ? Proszę uzasadnić odpowiedź.

10

5.13

Przetwarzanie zadania A realizowane na 9 procesorach umożliwia uzyskanie 5 krotnego przyspieszenia.

Przetwarzanie tego samego zadania A realizowane na 2 procesorach umożliwia uzyskanie przyspieszenia równego 100/55.

Proszę określić maksymalne możliwe do uzyskania przyspieszenie.

5.14

Część obliczeń niepodlegająca zrównolegleniu zajmuje 30% czasu obliczeń realizowanych sekwencyjnie. Jaka liczba

procesorów zapewni uzyskanie przyspieszenia równego 4, a jakie przyspieszenie przetwarzania można uzyskać przy

zastosowaniu 10 procesorów? Odpowiedź uzasadnij.

5.15

Pewne obliczenia A można częściowo zrównoleglić. 80% obliczeń A może być podzielone proporcjonalnie na dowolną

liczbę procesorów – zapewnia to przyspieszenie przetwarzania tej części równe liczbie wykorzystanych procesorów.

Pozostała część obliczeń A - 20% musi być zrealizowana sekwencyjnie. Jaka liczba użytych procesorów zapewni uzyskanie

przyspieszenia przetwarzania równego 7 dla całości obliczeń A ? Jakie przyspieszenie przetwarzania dla omawianych

obliczeń można uzyskać przy zastosowaniu 10 procesorów? Odpowiedź uzasadnij podając obliczenia i słowne wyjaśnienia.

5.16

Skierowany graf acykliczny służy do prezentacji algorytmu równoległego. Węzły oznaczają zadania, a łuki komunikacje między zadaniami. Zadanie może zostać przydzielone do procesora po wykonaniu zadań, które są połączone z

nim za pomocą łuków wejściowych. Zakładamy, że każde zadanie zajmuje 2 s, a czas komunikacji jest równy 0. Komunikacje

realizowane są współbieżnie. Dla każdego z 2 algorytmów zaprezentowanych poniżej określić:

A)

Maksymalny i średni stopień współbieżności,

B)

Wielkość przyspieszenia, efektywności i kosztu zrównoleglenia dla przetwarzania przy użyciu

liczby procesorów równej połowie maksymalnego stopnia równoległości.

5.17

Skierowany graf acykliczny służy do prezentacji algorytmu równoległego. Węzły oznaczają zadania, a łuki komunikacje między zadaniami. Zadanie może zostać przydzielone do procesora po wykonaniu zadań, które są połączone z

nim za pomocą łuków wejściowych. Zakładamy, że każde zadanie wymaga 2 s czasu procesora, a czas komunikacji jest

równy 0. Dla każdego z 2 algorytmów zaprezentowanych poniżej obliczyć:

Maksymalny i średni stopień współbieżności,

Wielkość przyspieszenia, efektywności i kosztu zrównoleglenia dla przetwarzania przy użyciu liczby procesorów

równej połowie maksymalnego stopnia równoległości

11

Przetwarzanie na GPU

6.1

Rozważmy obliczenia dla tablicy NxN uruchomione dla gridu z 2 wymiarowymi blokami wątków o rozmiarach: 16

wierszy po 32 wątki wg kodu poniżej.

__global__ void MatrixMulKernel(float* A_d, float* B_d, float* C_d, int N)

{

int Col = blockId.y * blockDim.y + threadId.y;

int Row = blockId.x * blockDim.x + threadId.x;

float C= 0;

for (int k = 0; k < N; ++k)

C += A_d[Row][k] * B_d[k][Col];

C_d[Row][Col] = C;

}

Proszę przeanalizować efektywność dostępów do pamięci globalnej.

Ile wynosi dla powyższego kodu stosunek liczby operacji do liczby dostępów do pamięci globalnej (CGMA). Jakie jest

znaczenie tego wskaźnika dla prędkości obliczeń przy użyciu GPU?

Proszę określić szczegółowo na poziomie koncepcyjnym (na czym polegają i jak je zrealizować) możliwe modyfikacje kodu

zmierzające do przyspieszenia obliczeń, proszę ocenić możliwy zarówno dodatni jak i ujemny wpływ poszczególnych

modyfikacji na prędkość obliczeń.

6.2

Rozważmy obliczenia dla tablicy NxN uruchomione dla gridu (N/K,1,1) z blokami wątków o wymiarach (K,1,1) wg

kodu poniżej (grid i blok mają w wymiarze X rozmiar różny od jeden).

__global__ void SUMKernel(float* Ad, float* Rd, N)

{

int Col = blockId.x * blockDim.x + threadId.x;

for (int i = 0; i < N ; ++i)

Rd[Col] += Ad[i][Col];

}

Proszę przeanalizować kod programu – opisać wykonywaną pracę, a następnie określić efektywność dostępów do pamięci

globalnej (tj. możliwość łączenia dostępów do pamięci globalnej).

Ile wynosi dla powyższego kodu stosunek liczby operacji zmiennoprzecinkowych do liczby dostępów do pamięci globalnej

(CGMA). Jakie jest znaczenie tego wskaźnika dla prędkości obliczeń przy użyciu GPU? Proszę założyć, że kolejne elementy

wiersza tablicy leżą pod kolejnymi adresami pamięci. Proszę ocenić i uzasadnić oczekiwaną prędkość przetwarzania w

stosunku do maksymalnej prędkości przetwarzania GPU, jakie czynniki i w jaki sposób wpływać będą na tę prędkość.

6.3 Rozważmy obliczenia dla tablic A i B (o rozmiarach NxN) i tablicy C (o rozmiarze N) uruchomione dla jednowymiarowego

gridu z jednowymiarowymi blokami H wątków wg kodu poniżej:

__global__ void test(float* Ad, float* Bd, float* Cd, int N)

{

int I = blockId.x * blockDim.x + threadId.x;

float C= 0;

for (int k = 0; k < N; ++k)

C += A_d[I][k] * B_d[I][k];

Cd[I] = C;

}

Proszę określić i uzasadnić:

- Niezbędną wielkość gridu

- Jaką pracę wykonają poszczególne wątki ?

- Ile wynosi CGMA? Jak wpłynie ta wartość na efektywność przetwarzania ?

- czy poszczególne dostępy do pamięci globalnej będą realizowane efektywnie dla compute capability 1.3 ?

- Jak wielkość H i N może wpłynąć na liczbę wykorzystywanych multiprocesorów (SM)?

- Jak wielkość H i N może wpłynąć na zajętość multiprocesora (SM occupancy) ?

12